从理论上讲,异构多核设备可以配备一个计算块,该计算块针对给定用例的任何类型的操作进行了优化。用于视频处理的 GPU、用于对象识别的神经网络处理器、运行操作系统的 CPU 等等。与同级别的同质处理器相比,不同用途的内核为 SoC 提供了更大的灵活性,因此在更广泛的工作负载范围内具有更高的性能和更低的功耗。

但当您开始考虑基于边缘的 AI、计算机视觉等应用程序的要求时,事实是 I/O 和内存变得与原始处理性能一样受到限制,甚至更多。

“内存速度只会这么快,对吧?” 英伟达嵌入式与边缘计算副总裁兼总经理 Deepu Talla “它并没有呈指数级增长。由于大小,位宽大致相同:它可以是 16 位、32 位、64 位、128 位,等等。大多数嵌入式处理器通常具有 32 位甚至 16 位接口,这也是出于成本和尺寸的原因。

“内存的速度只是一代比一代增长 2 倍,而且这通常每三年发生一次,”他继续说道。“然而,SoC 中的计算需求可能增加了 10 倍或 20 倍。”

您如何协调计算性能的这种不成比例的增长与内存技术的相对较小的进步?特别是当处理器演变成独特的逻辑集合时,它们都需要自己访问内存等资源。

根据塔拉的说法,你把它给了他们。以下是嵌入式存储器架构为满足下一代异构多核处理器的需求而发展的三种方式。

1、内核专用 SRAM

“如果你看很多这些嵌入式处理器,它们过去一直都有 SRAM,”Talla 说。“现在,对于每个特定单元,我们都有本地 SRAM,它从 DRAM 获取数据,在本地存储并处理它,然后发回最终输出。”

特定于内核的 SRAM 提供了几个优势,首先是由于不必将临时数据写回片外 DRAM 所带来的内存性能提升。

这种架构还具有降低功耗的额外好处,因为超低电压 SRAM 模块位于 SoC 内相应的逻辑 IP 附近或附近。

“如果你使用 DRAM,这可能是一个数量级的功率,所以你实际上是通过使用这些技术来节省功率,”Talla 解释道。

2、增加系统内存

今天的嵌入式处理器具有高达 4 MB 到 8 MB 的系统内存。此系统内存并非专用于任何特定内核,并且可以在 CPU、GPU 和加速器等元素之间共享。

与专用 SRAM 类似,更多共享系统内存的主要好处是更少的 DRAM 访问。例如,传统的视频编码序列如下所示:

DRAM -》 视频编码器 -》 DRAM -》 附加计算 -》 DRAM

增加的系统缓存可以实现这一点:

DRAM -》 视频编码器 -》 系统内存 -》 附加计算 -》 DRAM

如前所述,不同之处在于单独的内核不必不断地从片外 DRAM 中获取数据,因为大系统内存消除了对中间步骤的需要。

3、增加缓存大小

最后,随着更新的工艺技术使更高容量的内存更便宜,缓存大小将不可避免地增加。在异构 SoC 上发现的用于 CPU、GPU、DSP 和其他核心架构的更大缓存也将减少 DRAM 流量。

并且将增加的缓存大小与前两个进步配对开始产生一些重大收益。

“更多的 SRAM、通用的系统内存以及更多的大容量缓存可以让您在接下来的三到五年内将性能提高 10 倍到 100 倍,即使内存带宽可能只增加了一倍或四倍,”Talla 指出出去。

审核编辑:郭婷

-

嵌入式

+关注

关注

5056文章

18953浏览量

301644 -

DRAM

+关注

关注

40文章

2297浏览量

183189 -

编码器

+关注

关注

45文章

3563浏览量

133928

发布评论请先 登录

相关推荐

基于全志T113-i多核异构处理器的全国产嵌入式核心板简介

MCUXpresso IDE下在线联合调试双核MCU工程的三种方法

一文解析嵌入式多核异构方案,东胜物联RK3588多核异构核心板系列一览

嵌入式多核系统崛起,IAR将复杂化为简易的利器

嵌入式多核心系统渐成趋势,IAR工具化繁为简

简谈Xilinx Zynq-7000嵌入式系统设计与实现

简谈Xilinx Zynq-7000嵌入式系统设计与实现

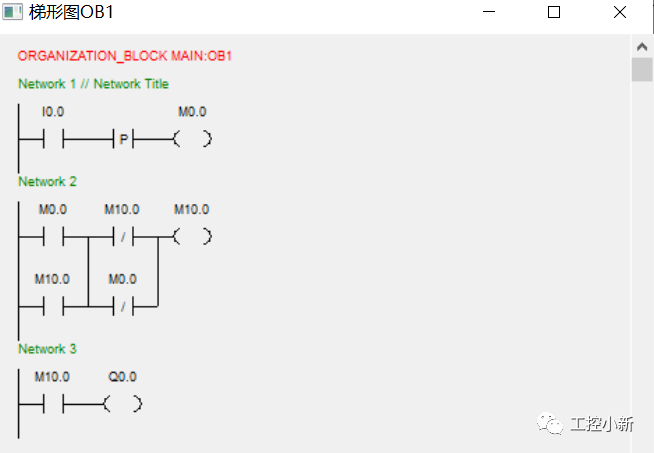

如何用三种不同的方法来用按钮控制灯光

为异构多核实现十倍嵌入式内存性能的三种方法

为异构多核实现十倍嵌入式内存性能的三种方法

评论