过去十年以来,从消费应用、网络或防御系统(包括传感器)开始的不同应用领域都受到半导体 VLSI 电路技术的影响。对于 ASIC (SoC),功率、性能(时间)和面积始终是设计中的挑战因素。基于用户应用,过去对上述一项或全部因素进行优化。除了 PPA,处理 IC 结构测试 -DFT 时间也成为一项具有挑战性的综合任务。随着设计复杂性与日俱增——由于摩尔定律,使用传统的 DFT 扫描方法可以测试 ASIC,但它会导致更高的测试数据量和非线性测试时间增加。早些时候,测试成本是实施扫描压缩时唯一考虑的因素。任何压缩技术的关键要求是保持与标准(未压缩)相比的高测试质量。测试压缩比在减少总测试时间方面起着至关重要的作用。在本文中,我们主要关注一种在不影响测试质量的情况下使用芯片顶部的最佳测试通道数量来减少测试时间的方法。

一、 简介

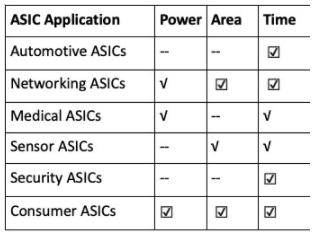

正如名称所定义的,ASIC 专为特定应用而设计。可以使用不同的技术来创建 ASIC,但由于高可靠性和低成本,CMOS 很常见。对于 ASIC(SoC 设计)来说,功耗、性能(时间)和面积是设计中的挑战因素。基于这些因素的应用权重取决于ASIC。在这里,图 1 显示了不同的应用,表 I 列出了因素的权重。

表 I

功率、面积和时间比较

二、 ASIC设计中对扫描压缩的需求

早些时候,测试人员成本是实施扫描压缩时唯一考虑的因素。测试模式的数量取决于测试数据量和测试时间。模式截断选项会导致测试覆盖率降低,最终会增加运送给客户的百万分之二的缺陷零件 (DPM),这会影响良率。因此,为了避免由于测试质量低而导致测试逃逸的增加,业界已经认识到测试模式压缩的必然需求。下一代 ASIC (SoC) 设计流程具有更复杂的结构,这会导致具有新的故障模型和额外的测试模式来检测这些故障模型,并且压缩也有助于解决该因素。

扫描压缩结果如下:

• 减少扫描数据内存的需求

• 减少每个零件的测试应用时间

• 减少所需扫描通道的数量

• 减少串行负载模式的仿真时间

A. 压缩技术简介

与标准(未压缩)ATPG 相比,任何压缩技术的关键要求是保持较高的测试质量。压缩技术基于传统的确定性 ATPG,并使用相同的故障模型通过熟悉的流程获得相似的测试覆盖率 。它通过改进扫描测试数据的压缩和减少测试时间来扩展ATPG 。它通过使用少量扫描通道控制大量内部扫描链来实现扫描测试数据的压缩。

B. 基本压缩术语

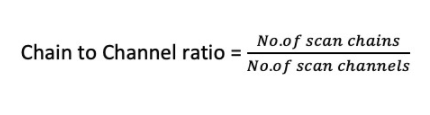

对于压缩,外部扫描链称为扫描通道,以将它们与核心内的内部扫描链区分开来。它们的数量明显少于内部扫描链的数量。链通道比的确定,定义了设计的压缩,直接影响测试覆盖率和测试数据量。有效的压缩取决于扫描链和扫描通道。

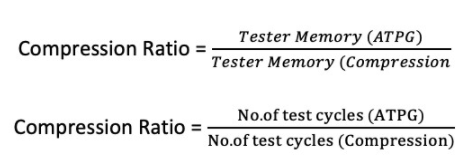

压缩可以表示为 ATPG 的测试器内存与压缩的比率,也可以表示为 no。ATPG 与压缩的测试周期。由于没有。通道数是相同的,两个计算将是等效的 。

压缩是两个因素的函数:

* Chain-to-channel ratio:扫描链(内部到核心)与扫描通道(外部)的比率

* 每个图案的移位周期数的变化(扫描链的数量、扫描单元的数量和每个图案的初始周期)。

三、S can 压缩分析

我们只能直接控制链与通道的比率。然而,这三个因素是相关的。内部扫描链与外部扫描通道的比率越高,每个模式的压缩率越高,但压缩分析将为您提供压缩的估计计算,因为您改变了不同的因素。

A. 什么是分析压缩?

通常扫描通道的数量取决于硬件资源,例如 ATE 上的测试通道和可用于测试的顶层设计引脚。但是,为了有效压缩,我们可以更改扫描链要求。压缩分析命令适用于不同链通道比对测试数据的影响,而无需修改您的芯片设计。压缩分析有助于确定压缩结构的链通道比、测试覆盖率和测试数据量。

B. 压缩分析是如何工作的?

它分两步分析应用程序的压缩。

两个步骤如下:

1. 分析插入扫描的设计并给出测试覆盖率开始下降的最大链通道比范围。

2. 计算指定链与通道比率的硬件配置,生成临时测试模式,并返回压缩配置的测试数据统计[4]。

C. 压缩分析流程:

1. 检查当前扫描配置并计算通道/链比率。

一个。根据压缩配置,它将为您提供估计的压缩比。(检查 intest/extest 配置报告)。

2. 用现有的扫描配置写出扫描设计网表并生成运行模式。

3. 在模式生成开始之前添加analyze_compression 命令。(在模式生成之前)[4]。

4. 此命令将帮助分析压缩并在模式生成阶段结束时为您提供以下统计信息。

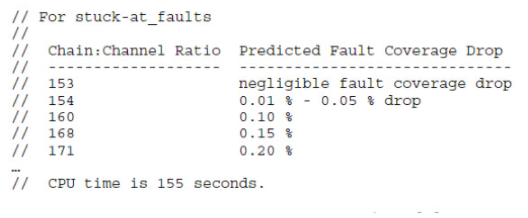

该工具分析设计并返回一系列链与通道比率值,从故障覆盖率下降可忽略不计的比率开始,到故障覆盖率下降 1% 的比率结束,如下所示:

图 2 压缩分析数据

6. 对于可忽略的故障覆盖率下降,选择相应的通道链比值并重新计算通道数。

7. 更新的通道数将是实现高压缩所需的最小通道,故障覆盖率下降可忽略不计。

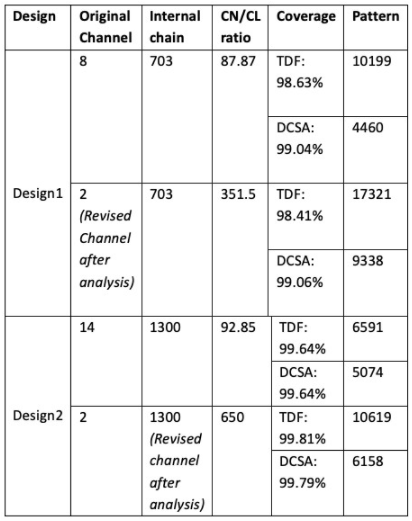

表三

结果比较

基于Flow,进行了通道缩减实验,表2显示了通道与链比、压缩比、覆盖和模式数的结果比较。

四。 对分层测试的影响

致力于尖端技术会导致顶级 ASIC/SoC 的引脚数减少。有限的引脚将在顶层用于测试,大多数时候这些引脚在功能引脚之间共享。管脚的数量在顶层受到限制。使用以下示例,我们可以检查块级扫描通道减少在芯片级协作期间的帮助。考虑下图所示的场景。

使用不同的案例/场景,我们将检查扫描通道减少如何在顶层提供帮助。

1) 案例 1:考虑我们有 3 个块内核可用并且在芯片顶层有两个实例可用的场景。每个核心运行 4 个扫描通道,如图 3(a) 所示。在芯片顶层模式生成和仿真期间,所有三个实例都将成组使用。3 个核心/块 * 2 个实例 = 6 个顶级实例。考虑我们将有 12 个频道可用。为了适应所有 6 个实例,我们需要为模式生成创建 2 个模式,如图 3(b) 所示。

图 3(b)。分层测试的概念图

因此,在这种情况下,我们需要创建总共 2 个组来容纳所有实例(每个 3 个)以使用 12 个可用的扫描通道。现在让我们看另一个案例。

2) Case2:在这种情况下考虑使用analyze_compression。我们已经完成了扫描通道缩减,每个内核使用的扫描输入/输出通道数为 2,如图 4(a) 所示。让我们检查统计数据。3 个核心块 * 2 个实例 = 6 个实例,顶部可用的总扫描通道为 12。每个块将仅使用 2 个通道,因此使用的总通道为 6 个通道。考虑到这一点,我们现在可以在 1 模式下容纳所有 6 个实例,如图 4(b) 所示。测试时间将减少一半。

图 4(b)。分层测试的概念图

V. 增加压缩和模式膨胀之间的权衡

1) 压缩比

扫描通道数的减少导致更高的压缩比。平衡压缩目标与测试资源和设计需求也很重要。使用不必要的大压缩目标可能会对压缩、测试质量和芯片设计布局产生不利影响。

2) 较低的测试覆盖率

较高的压缩比会增加每个测试模式的压缩率,但也会增加生成无法压缩的测试模式的可能性,并可能导致测试覆盖率降低。

3) 模式通货膨胀

更高的压缩比也减少了动态压实可以适应测试模式的故障数量。这可以增加检测这些故障的测试模式的总数。

为了减轻较高压缩对 ATPG 覆盖率和模式数量的影响,在分析压缩期间,选择通道与链的比率值,以使对覆盖率的影响可以忽略不计。

结论

在本文中,我们检查了扫描压缩确实有助于减少 ASIC 设计中的测试时间 (DFT),但扫描通道减少也是一种有助于顶层测试时间的方法。根据示例案例研究,我们可以确定有效压缩所需的最小通道数,以及它如何影响其他参数,如链通道比、压缩比和测试时间。如今在半导体行业,这些因素被广泛用于节省测试成本。

作者:Chintan Panchal,Charu Patel

审核编辑:郭婷

-

芯片

+关注

关注

459文章

51893浏览量

433293 -

半导体

+关注

关注

335文章

28309浏览量

229755 -

asic

+关注

关注

34文章

1238浏览量

121678

发布评论请先 登录

相关推荐

如何减少dsp启动时间?

如何通过直流负载箱优化电源测试效率?

DFT的常见误区与解决方案

DFT在生物信号分析中的应用

DFT的优缺点比较 DFT在机器学习中的应用

DFT与离散时间傅里叶变换的关系 DFT在无线通信中的应用

DFT在图像处理中的作用 DFT在音频信号处理中的应用

如何使用DFT进行频谱分析

DFT在信号处理中的应用 DFT与FFT的区别

FPGA和ASIC在大模型推理加速中的应用

通过解决测试时间减少ASIC设计中的DFT占用空间

通过解决测试时间减少ASIC设计中的DFT占用空间

评论