今天的许多设计都包括三个不同值(10uF/1uF/100nF)的去耦电容器,或者当只使用一个电容器时,可以使用 0.1 uF 这样的小值。是时候重新考虑这些过时的遗留设计指南了。

作为遗留问题的神话

从一开始,电子行业就被更快、更小、更便宜、现在的四种力量拉向未来。这推动了技术、材料、制造和设计方面的革命性和进化性发展的不断进步。

有时,我们在上一代采用的设计原则在下一代变成“遗留代码”,不再适用。适用于一种互连技术组合的方法可能不适用于新的组合。遗留设计指南成为一个神话,应该重新评估。

唯一不变的是变化

我们的行业见证了从电子管、晶体管、集成电路到封装系统的革命性进步。我们经历了从离散布线到单层和双层印刷电路板,再到多层板,再到 HDI 技术的革命性进步。

我们已经看到了从早期通孔器件(例如简单的金属罐封装到 DIP 到大型针栅阵列)到带引线框架的表面贴装封装到小型有机印刷电路基板到球栅阵列到芯片级封装的革命性进步,以及多芯片模块。。

图 1显示了四个具有代表性的技术代板和封装的时间快照

图1 四个时间快照。

从左到右:管子和分立线、管子和电路板、分立晶体管和电路板,以及带有多层电路板的表面贴装 BGA 封装。

技术世代对设计的影响

信号如何与互连交互背后的基本原则没有改变。它们仍然基于具有 150 年历史的麦克斯韦方程组。然而,随着每一代封装和互连技术的发展,我们如何实施设计原则并将其转化为设计指南已经发生了变化。

在使用离散布线的管子的早期,互连通常是透明的。当互连很重要时,首先要解决的问题通常是由于大环路电感引起的串扰。“越短越好”的设计原则以及捆绑在一起的电源线和地线很受欢迎。

当引入多层板时,这些遗留代码中的一些继续将电源和接地路由为离散线,而不是使用接地层。将电源和接地紧密捆绑在一起的传统阻碍了一些早期设计中接地层的实施。

随着时钟频率升至 20 MHz 以上,传输线效应开始占据主导地位,受控阻抗、布线拓扑和端接策略成为互连设计的重要驱动力。“越短越好”的遗留代码导致人们不愿使用菊花链路由拓扑,这可能会导致路径长度更长但反射噪声更低。

当我们进入 1 Gbps 状态时,损耗变得很重要,我们开始选择除了常见的基于环氧玻璃的材料之外的其他材料,以降低损耗。当使用这些低损耗层压板时,我们发现超过 5 Gbps 的铜损耗比预期的要高,我们发现更光滑的铜更好。超过 10 Gbps 时,我们发现 50 年前的玻璃纤维增强电路板制造方法导致了玻璃或纤维编织歪斜的新问题。

有了新技术,我们需要新的设计规则。高剥离强度、环氧树脂玻璃电路板的旧规则不一定是千兆互连时代的最佳设计指南。

专家指南

我们每天在我们的电子产品中应用的设计指南是由行业领导者制定的。这些公司在信号完整性、电源完整性、EMC、材料、制造、可靠性和集成方面拥有专门的专家,他们正在推出最前沿的产品。这些专家应用基本原则为他们引入的新材料、IC 技术和互连技术建立设计指南。

但有时,在一代技术中起作用的东西在下一代中变成了神话。由于这些设计规则是由专家制定的,因此业界其他人有时不愿意放弃旧的设计指南,并继续在可能不适用的新一代技术中使用它们。它们成为我们工具箱中根深蒂固的神话。

如果最后一个设计遵循这些旧的设计指南,人们通常认为这是因为设计指南,即使它可能不顾它们。有时遗留代码是中性的,有时它有缺点。即使它是中立的,如果它阻止建立更好的设计指南,它也会变成负面的。它变成了一个即将被取代的神话。

设计指南神话,例如每个电源引脚使用三个不同的电容器进行去耦,这会降低下一代设计的性能,因此应始终重新评估。

高频电容器

当安装电感大于约 1 nH 时,一个简单的串联 RLC 电路可以很好地描述真实电容器的理想等效电路模型。当它低于 1 nH 时,会出现新的效果,真实电容器的传输线模型更匹配。

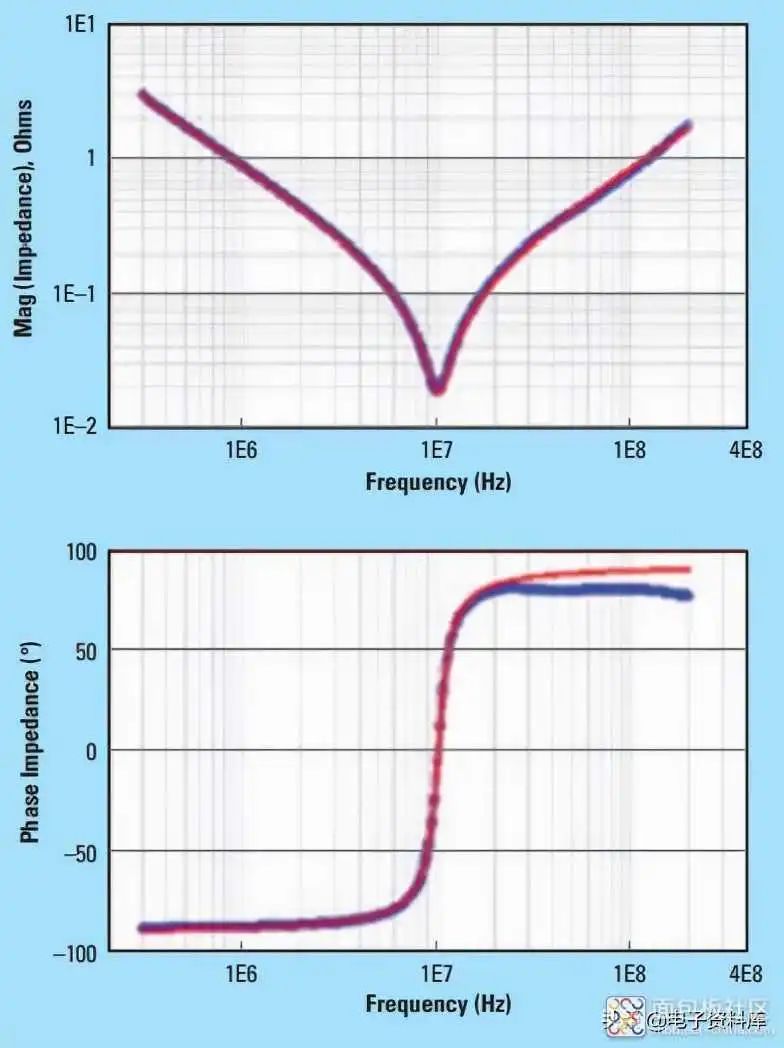

简单的 RLC 模型适用于大多数代的电容器。图 2显示了实际 SMT、MLCC 电容器的测量阻抗和理想 RLC 串联电路的模拟阻抗的示例 。

图2 真实 SMT 电容器的测量阻抗(蓝色)和相位以及简单 RLC 电路模型的模拟阻抗(红色)示例。

测量相位和模拟相位的差异表明实际电容器中的 ESR 行为不包括在简单的 RLC 模型中。

该系列 RLC 电路模型是最简单的模型,通常适用于电解、钽、陶瓷、MLCC 电容器的技术范围,无论是通孔还是表面贴装。这只是一阶模型,许多实际电容器可以与二阶模型更好地匹配。但第一个模型提供了对这三个重要术语的作用的洞察。

理想的 C 对应于低频下的阻抗行为。R 通常被称为等效串联电阻 (ESR)。这是由于实际电容器的引线、极板的金属化,以及在较小程度上,电容器中的其他损耗机制。L 称为等效串联电感 (ESL)。这主要是由于电容器的内部结构及其电路板电源和接地路径到它所连接的 IC 引脚。

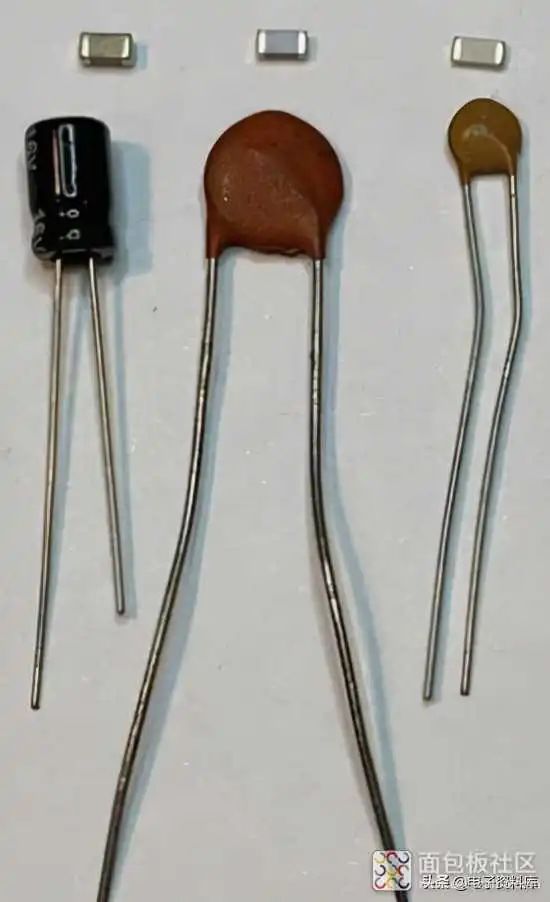

在通孔电容器时代,从 50 多年前开始,两种常用的电容器技术是电解和陶瓷盘。这些示例如图 3所示。

图3 电解和陶瓷圆盘电容器的例子。

较小物理尺寸的电容器具有较小的电容、较小的 ESL 和较大的 ESR。

在电解电容器和陶瓷圆盘电容器技术中,可以在电容器中设计的电容数量与其物理尺寸和引线长度之间存在直接联系。较大的电容值意味着较大的物理尺寸电容器。

因为 ESL 还取决于电容器的物理尺寸及其引线长度,所以较大值的电容器也具有较大的 ESL。例如,47 uF 电解电容器的 ESL 可能高达 30 nH,而小型 0.1 uF 圆盘电容器的 ESL 可能低至 7 nH。

甚至 ESR 也因电容器技术和尺寸而异。电解电容器的 ESR 可能在 0.1 到 5Ω 的量级。较小尺寸的电容器通常具有较高的 ESR。陶瓷圆盘电容器的 ESR 约为 0.1 至 1Ω。

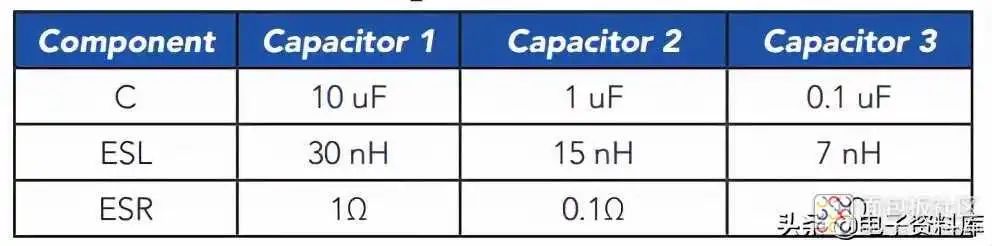

电容值和 ESL 之间的这种联系极大地影响了大电容和小电容的阻抗分布。在低频下,真实电容器的阻抗与其电容有关。在高频下,真实电容器的阻抗大约是其引线电感。图 4显示了具有三种不同阻抗曲线的三种不同电容器的示例。他们的一阶模型的组件值可能是:

图4 这三个电容器的模拟阻抗曲线。最小值提供高频下的低阻抗

对于带引线的通孔电容器,通常正确的是,较小值的电容器尺寸较小,并且可以安装较低的环路电感。这意味着它们在较高频率下将具有较低的阻抗。在寻找高频下阻抗低的通孔电容器时,应选择小值和小尺寸的电容器。

这就是为什么小值电容器通常被称为“高频”电容器的原因。由于它们的引线较短,如果以低回路电感安装到电路板上,它们在高频时提供最低阻抗。

如果我们想要低频时的最低阻抗以及高频时的最低阻抗,通常的做法是并联添加两个或三个电容器。大容量电容器在低频时提供低阻抗,而具有较低 ESL 的小容量电容器在高频时提供低阻抗。并行组合充分利用了两种配置的优点。

MLCC电容器与高频电容器的神话

当我们改用基于MLCC表面贴装技术的电容器时,电容器的特性与引线电容器有很大的不同。图 5显示了 1206 型 MLCC 电容器的示例,其电容值对应于相应陶瓷盘电容器中的相同电容。

图5 个 1206 封装的 MLCC 电容器(顶部)和相应值的陶瓷圆盘电容器。

通常,可以在完全相同的机身尺寸中获得大范围的电容值。0402 中的 10 uF 与 0.01 uF 一样容易。这意味着 MLCC 电容器的 ESL 如果以最佳方式集成到电路板中,将与其电容值无关。

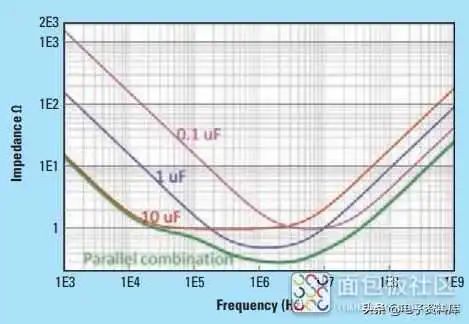

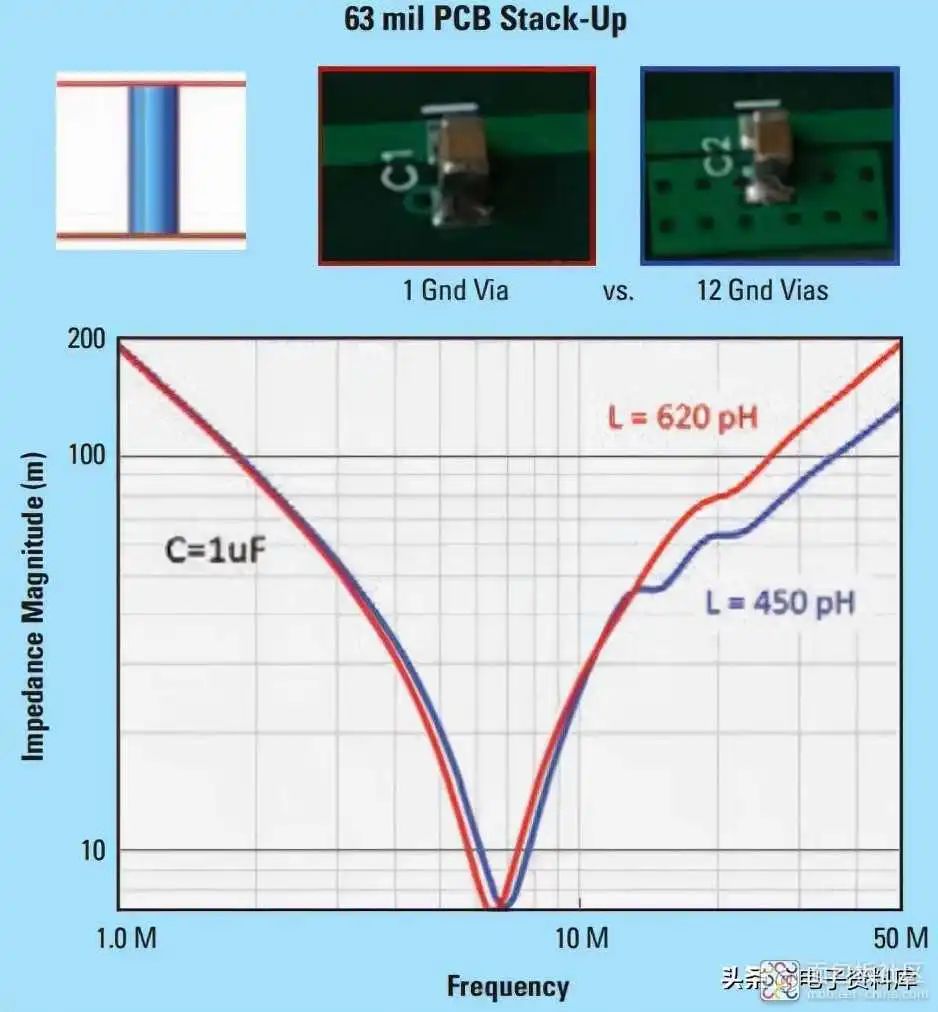

事实上,使用低环路电感设计,MLCC 的 ESL 可以设计为小于 1 nH,即使在两层电路板上也是如此。图 6显示了在具有 0.620 nH ESL 的两层 063 mil 厚板上测得的 1 uF MLCC 电容器的阻抗曲线示例 。

图 6 电路板上 1 uF MLCC 电容器的测量阻抗曲线示例,电路板上的 ESL 为 0.620 nH。

这也表明当安装电感小于 1 nH 时需要二阶模型。测量由Picotest提供。

10 和 0.1 uF MLCC 电容器将具有完全相同的高频阻抗。电容值较小的电容不再是“高频”电容。事实上,一个 10 uF 的 MLCC 电容也将是一个“高频”电容。

如果设计中具有低 ESL 的价值,则应始终使用 MLCC 电容器。即使是 10 uF MLCC 电容器,其 ESL 和“高频”陶瓷圆盘电容器的阻抗也可能低于 10%。

在较旧的产品中,当使用通孔电容器时,较小的电容值具有较低的 ESL 和较高频率下的较低阻抗。当电路板上的电源引脚上只有一个电容器的空间并且来自该引脚的瞬态电流很小时,指定了一个具有低电感的单个“高频”电容器。这是一个低值电容,通常为 0.1 uF。

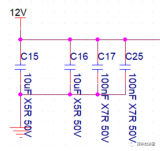

当一个引脚有三个电容器的空间时,通常会指定三个电容器值的范围。与仅一个值电容器相比,这提供了在高频下的较低阻抗和在低频下的较低阻抗。图 7是显示这些常见规格的典型示意图示例。

图7 一个典型电路示例,显示了具有三个不同电容值和一个小值单个电容的去耦网络。

但是,此原理图示例并非来自使用通孔部件和通孔电容器的旧设计,而是来自 120 MHz 前沿 Cortex M4 微控制器板,全部采用 MLCC 电容器设计和组装。

高频电容器的神话已经延续到这个设计中,因为它在许多其他设计中仍然指定一个小值电容器用作单个电容器和三个不同的值用于更高电流的引脚。

高频电容器和使用三种不同电容器值的神话是许多现代设计中仍然存在的遗留代码。

哪个更好?

那么,哪个更好:三个电容值相差十倍还是三个电容值相同?

不幸的是,只有具有所有元素的准确模型的系统级分析才有机会回答这个问题。

如果规范中的建议是使用三种不同值的电容器,那么编写规范的工程师很有可能从未做过任何分析,而是使用了基于高频电容器神话的 50 年历史的设计指南。随着 20 年前 MLCC 电容器的推出,该建议背后的理由消失了。怀疑 PDN 设计。

在这种情况下,您使用什么可能并不重要。尽管有电容值,您的产品也可能工作,但可能不是因为它们。

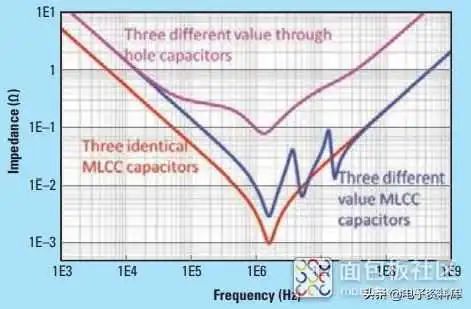

当三个具有相同ESL的不同值的电容器并联组合时,在它们的自谐振频率之间会产生两个并联谐振峰。峰值阻抗值与相邻电容器的电容和电感以及电容器的ESR有关。

图 8显示了三个电容器的三种不同组合的模拟阻抗曲线。一种组合是建议在通孔技术中实现 10、1 和 0.1 uF。第二个是在 MLCC 电容器技术中实现的相同组合。第三种组合都是相同的 10 uF MLCC 电容器。MLCC 电容器的 ESL 为 1 nH。

图 8 三个不同和三个相同 MLCC 电容器的模拟阻抗曲线。

与三个不同值的电容器相比,三个相同大值的电容器值可能会在整个频谱上提供更低的阻抗(并且在中频处没有并联谐振峰值),但这并不意味着它是一个更稳健的解决方案。

最后一个产品可能有效,但您可能不知道该设计有多健壮,或者某些无法追踪、不可重现的故障是否可能是由于过度的开关噪声以及恰到好处的数据模式收敛而导致的并联谐振时的阻抗。

不要误以为三个不同值的电容器是一种稳健的策略,或者三个电容器的值都相同更稳健。如果没有系统级分析,它们都可能同样可接受、同样边缘化或因相同故障而失败。

“测试”质量

如果您不打算进行自己的系统级分析,请计划实施彻底的测试计划,以便您可以找到 PDN 中的薄弱环节并“测试质量”。

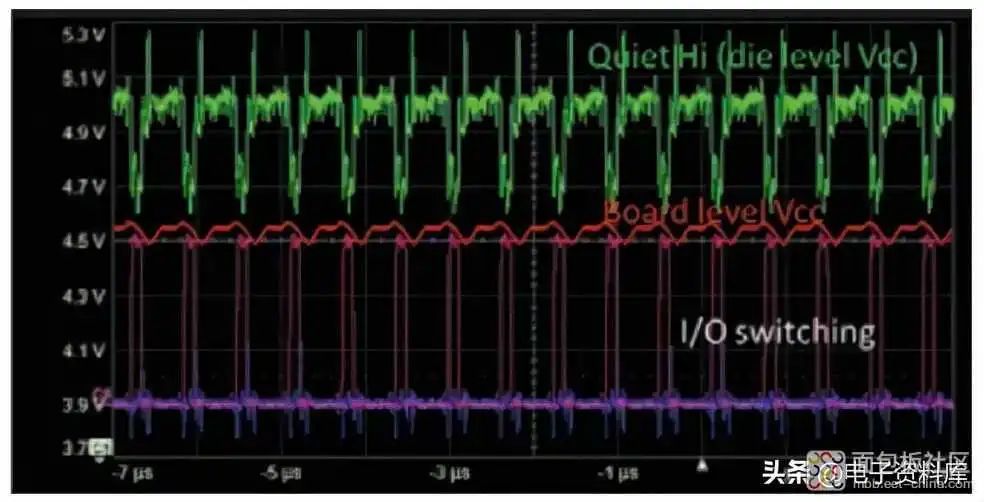

完整的测试计划的一部分是为 PDN 中的测试进行设计。例如,使用高带宽感测线表征噪声(不仅在板级,而且在管芯的焊盘上)越好,您就越能够将一种去耦策略与另一种去耦策略进行比较。图 9是在 I/O 切换时在芯片电源轨和板级上测得的电压噪声示例。在 5 V 电压轨上,片上电压噪声为 600 mV 峰峰值。板级电压噪声仅为 75 mV 峰峰值。

图9 在芯片上相同的电源轨上测量的电压噪声是通过检测线测量的,在电路板上,两者的标度相同,均为 200 mV/div

无论应用如何,较低的安装回路电感总是有价值的。这就是为什么 MLCC 去耦电容器应始终是放置在板上的第二个组件,因此它们可以以实际最低的安装电感进行布线。

如果在一个引脚上只指定一个电容器,这是许多低电流应用的常见做法,那么在可接受的额定电压下,始终使用允许的最大电容,以实现最小的实际尺寸。如果没有系统级分析,这仍然不能保证产品的稳健性,因此必须制定全面的测试计划。

设计质量:正确的去耦电容策略

使用三种不同值的去耦电容器是基于过时的假设,即小值电容器是“高频”电容器。在我们的 MLCC 电容器时代,这个假设不适用,有什么更好的建议?不幸的是,答案是“视情况而定”。

但是,有一些适用于大多数系统的通用设计指南。

任何 PDN 的目标都是为那些需要它的组件提供直流电压,并为应用提供可接受的噪声水平。用于去耦的 MLCC 电容器只是良好 PDN 策略的一部分。

PDN 设计的基本原则之一是保持阻抗分布,如 IC 的焊盘所见,阻抗平坦且值可接受的低。这意味着通常通过增加更多电容来减少并联谐振峰值,减少环路电感,并通过使用不同的电容值或通过受控的 ESR(这将降低峰值的 q 因子)来塑造阻抗曲线。

这有时会转化为足够的大容量电容,从而降低 VRM 大容量电容器的峰值。在高频端,板级的平坦阻抗分布将有助于抑制片上电容和封装引线电感并联谐振峰值的班迪尼山。

选择电容器值需要进行系统级分析,包括一端的 VRM 和另一端的消耗元件。当您设计所有安装功能以尽可能减少电容器的环路电感时,使用 3D 仿真器和基于测量的建模工具为 PDN 元件开发准确的模型以仿真整个系统总是很有价值的。

VRM 的准确模型以及每个导轨和封装引线电感的片上电容是设计稳健设计的整体分析的一部分。

当存在相当大的封装去耦时,大容量电容器和 MLCC 电容器的低频特性更为重要。当片上电容和封装引线电感占主导地位时,从它们的并联谐振中产生一个大的班迪尼山,从板级 MLCC 电容器产生的平坦阻抗分布中进行阻尼是很重要的。

不幸的是,除了使用受控 ESR 电容器之外,仅三个电容器值的组合不会为 Bandini Mountain 提供板级的任何阻尼。

这只是对真正进入优化的、具有成本效益的解耦策略的一些设计驱动力的一瞥。第一步是识别问题。第二步是确定问题的根本原因,第三步是确定提供可接受噪声的整体 PDN 设计策略,其中优化的解耦策略只是其中的一部分。

当系统的目标阻抗差异超过六个数量级时,从许多物联网应用中的超过 10Ω 到基于大型网络处理器的产品中的小于 10 uOhms,没有一种具有成本效益的策略,而是许多。

但这是一个不同章节的故事。

概括

使用三种不同电容器值的起源是基于使用通孔引线电容器。较小电容值的电容器通常在高频下具有较低的 ESL 和较低的阻抗。对于通孔电容器,使用三种不同的电容器值具有性能优势。

但是对于使用了 20 多年的 MLCC 电容器,这些陈旧的传统设计指南不再适用。

当只指定一个或三个电容器用于去耦时,可能是因为没有对设计进行分析。相反,在上一个设计中起作用的是在下一个设计中推荐的。尽管使用了三个不同的值,并且很有可能,该设计作品在使用所有三个相同的值时同样有效。在这种情况下,您的设计的稳健性是“测试”而不是“设计”。

最好的方法是始终进行自己的分析,包括配电系统的其余部分,以及所有组件的准确模型(如果可用),因为它们正在安装到您的系统中。

如果您的设计指定了三种不同的电容值,您可能会遵循已沿用 20 多年的传统设计指南。可能是时候为您的下一个设计重新考虑该设计指南并进行自己的分析了。

审核编辑 :李倩

-

电容器

+关注

关注

64文章

6358浏览量

100709 -

去耦电容

+关注

关注

11文章

318浏览量

22572

原文标题:去耦电容 0.1 uF、10uF、1uF、100nF,现在还适用吗?

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

三个不同值(10uF/1uF/100nF)的去耦电容器

三个不同值(10uF/1uF/100nF)的去耦电容器

评论