ASML开发的下一代EUV平台,将数值孔径从0.33增加到0.55,将能提供比当前的EUV平台高70%的分辨率能力。

在最近的SPIE Advanced Lithography+Patterning Conference上,来自英特尔的Mark Phillips对0.55高数值孔径极紫外光刻技术进行了有见地的分享。Mark甚至断言High-NA EUV的开发进展将支持2025年的生产部署。本文总结了Mark演讲的亮点,包括对0.55NA一代之后的预测。

具有13.5nm波长源的高数值孔径系统将提高亚13nm半间距曝光所需的分辨率,以及更大的图像对比度以实现更好的印刷线均匀性。High-NA EUV光刻的分辨率通常被称为“13nm到8nm半间距”。

EUV技术历史

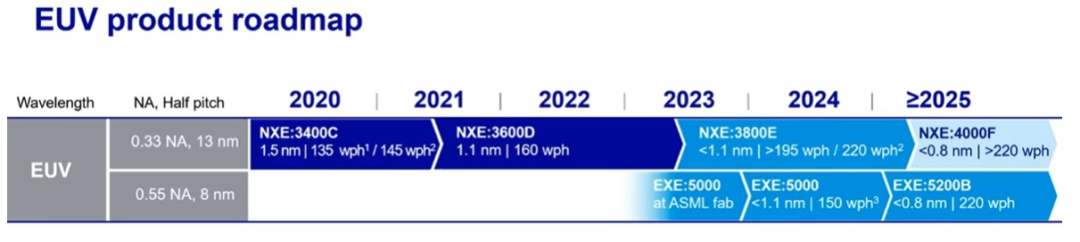

首先回顾以下0.33 NA EUV技术的历史。2014-2017年第一代系统开发周期中实现目标源功率和可用性的困难。晶圆成本评估反映了增加的工具成本、掩模成本和0.33NA过渡对吞吐量的影响。

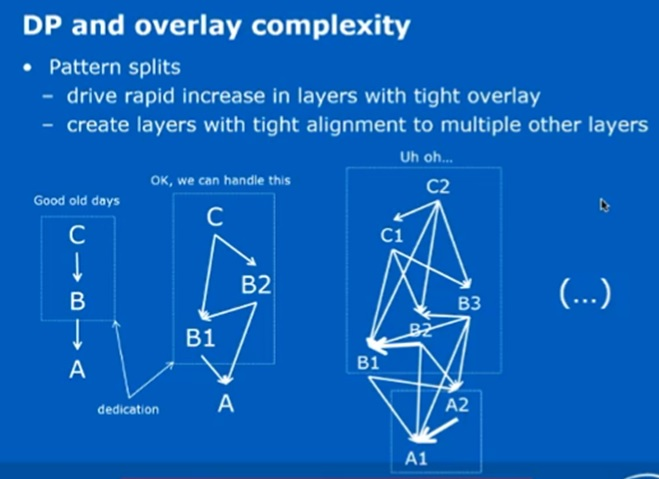

Mark指出:“93i的间距分割光刻(多图案)运行良好。与EUV过渡相结合所需的光刻基础设施尚未完全可用。转向0.33NAEUV的令人信服的原因是间距划分对边缘放置误差(EPE)的影响。带有间距划分的叠加对齐复杂性显着增加。”下图说明了Mark提到的掩模对齐依赖关系的示例,因为使用了越来越多的双图案掩模层。

Mark表示,从成本分析的角度来看,在解决用单个0.55NA掩模替换双图案0.33NA层时,与早期用单个0.55NA掩模替换193i掩模时的成本权衡相比,0.55NA EUV会比0.33NA EUV更方便掩膜。

EUV基础设施

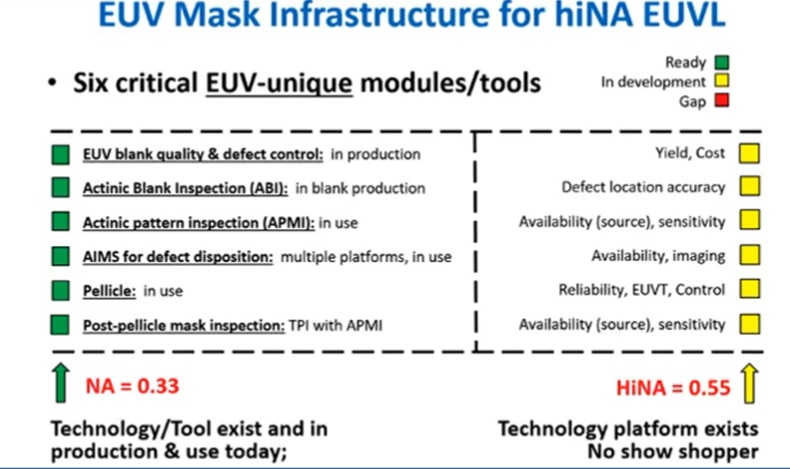

EUV光刻的讨论往往集中在ASML光刻机上——然而,有一组丰富而复杂的相互依赖的技术需要伴随曝光系统的任何变化:

剂量敏感性、粘度、涂层均匀性与厚度、可实现的分辨率以及对曝光时材料内光子/离子/电子相互作用的理解

掩模空白质量:平整度、缺陷、热膨胀系数

图案掩模质量:掩模吸收层的缺陷、反射率/消光

掩模缺陷检测技术——分辨率和吞吐量

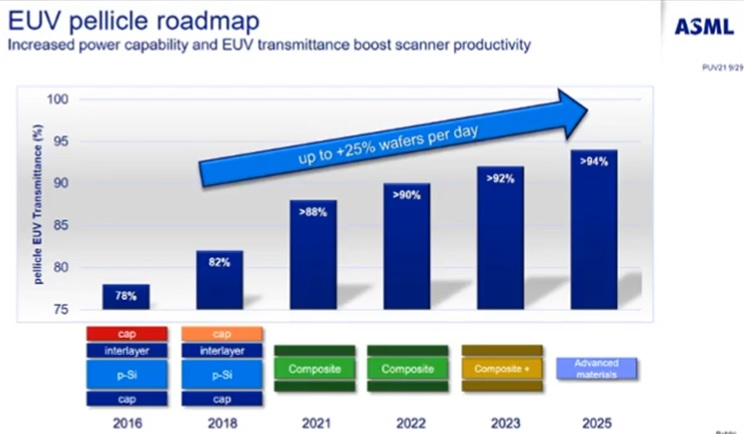

薄膜:透射率、均匀性、与暴露于高能照明的兼容性、薄膜贴附后缺陷检测

Mark称赞了光刻行业在所有这些领域取得的相应进展,并特别提到了检测计量系统供应商。他说,“到2019年,所有0.33 NA EUV的基础设施系统都是不错的,尽管薄膜的传输、均匀性和功率弹性仍需要改进。”

ASML的下图说明了防护膜透光率与晶圆产量之间的直接关系,目标是在2025年实现“先进的防护膜材料”,提供》94%的透光率。

0.55 High-NA转换

Mark分享了即将到来的流程节点转换的目标:

7nm节点:18nmHP

5nm节点:13nmHP

3nm节点:10nmHP

然后,他回顾了0.55NA基础架构的各个方面。

EUVEXE:5000系统

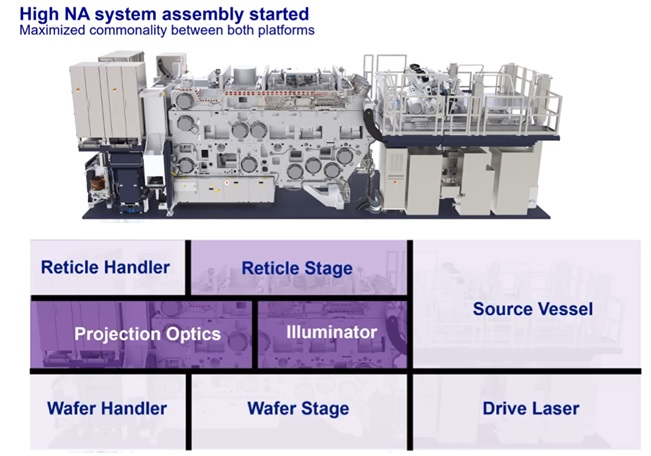

Mark表示,对下一代EUV光刻机可用性的信心很高。这些系统利用了第一代NX:3000系列中的许多现有子系统。

下图显示了高NA EUV系统的新子系统(紫色),以及从当前系列移植的子系统。

投影光学器件是一个关键的新模块。蔡司和ASML之间的合作开发进展顺利。至于必需的EUV光刻胶,Mark表示化学放大光刻胶(CAR)和金属氧化物光刻胶仍处于积极开发阶段。Mark说:“还有几个优化参数仍在评估中,包括光刻胶类型、粘度、厚度和达到目标分辨率的能量剂量、显影光刻胶轮廓和线边缘均匀性。”

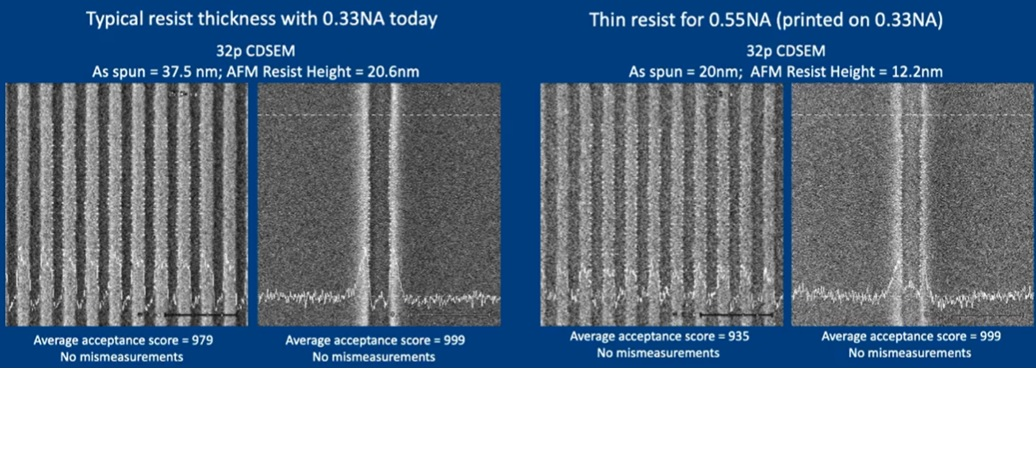

下图显示了0.55NA抗蚀剂实验在20nm旋转厚度下(使用0.33NA曝光)的SEM和原子力显微镜轮廓结果。

Mark指出,从0.33NA工艺步骤的约37.5nm抗蚀剂厚度到0.55NA更薄的层需要详细注意抗蚀剂粘度和旋转工艺步骤。(较薄的抗蚀剂在抗蚀剂高度与宽度方面保持2:1的纵横比。请注意,对于较高的NA光学系统,曝光的景深会降低,这是选择抗蚀剂厚度时的另一个考虑因素。另请注意,较薄的抗蚀剂抗蚀剂会导致SEM图像对比度降低,因此需要不断开发改进的高通量抗蚀剂计量。)

高数值孔径EUV掩模

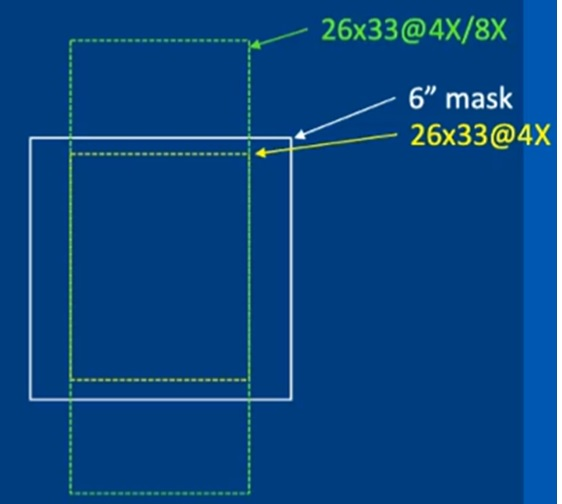

0.55NA系统采用了独特的创新光路。光场数值孔径的增加需要相应地改变掩模到晶片的曝光减少。投影光学系统利用各向异性缩小因子,即x维度缩小4倍,y维度缩小8倍。然而,如下图所示,传统的6英寸掩模尺寸不支持“全光罩”26mmX33mm视场——8X demagy范围超过面罩高度。

因此,每个High-NA EUV层将有一个双“半场”掩模曝光序列。

Mark表示0.55 NA EUV掩模基础设施的其余部分将充分利用为0.33 NA开发的现有技术。Mark说:“与过渡到(环栅)RibbonFET器件相关的计量挑战远远超过了与High-NA EUV掩模检查和测量相关的挑战。”

未来的0.7NA系统

在SPIE高级光刻会议上的另一次演讲中,ASML和imec表示他们正在荷兰Veldhoven建立一个High-NA EUV系统原型设施,将于2023年上线。该实验室将允许进一步开发抗蚀剂和实验室合作伙伴的方法流程。

Mark表示:“英特尔将继续与ASML密切合作,与该实验室的High-NA研究人员合作。我们预计2023年底或2024年初在俄勒冈州安装试点工具系统,并于2025年投入生产。”

Mark认为下一个目标可能是:

7NA

非整数掩模缩小光路(例如,y维度上为7.5X,x维度上为5X)

新的掩膜材料和尺寸的出现

Mark说:“我们需要一种热膨胀率极低的材料(LTEM)来制造掩模坯。我们将需要更好的吸收器。而且,我们将需要一个新的‘标准’掩膜尺寸。”下图显示了如何应用300毫米圆形(775微米厚的基板)。

英特尔正与ASML合作,在2024年实现早期High-NA系统可用性,生产日期目标为2025年。由于重用扫描仪的0.33NA经验的显着影响,这些日期的置信度相对较高子系统对掩模计量和检测技术的重大成就。

Mark表示,尽管在选择用于High-NA曝光的抗蚀剂和薄膜方面仍有重大进展,但新扫描仪中的光学系统是关键路径。

采用0.55NA光刻技术将实现亚13nm半间距关键尺寸,与英特尔超越18A节点的工艺路线图一致。

审核编辑 :李倩

-

EUV

+关注

关注

8文章

607浏览量

86081 -

ASML

+关注

关注

7文章

718浏览量

41277

原文标题:详解ASML最新0.55 High-NA EUV平台

文章出处:【微信号:ICViews,微信公众号:半导体产业纵横】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

意法半导体下一代汽车微控制器的战略部署

西门子EDA发布下一代电子系统设计平台

ASMPT与美光携手开发下一代HBM4键合设备

24芯M16插头在下一代技术中的潜力

丰田、日产和本田将合作开发下一代汽车的AI和芯片

日本车企联手开发下一代汽车软件

英特尔率先推出业界高数值孔径 EUV 光刻系统

使用NVIDIA Holoscan for Media构建下一代直播媒体应用

NVIDIA的专用AI平台如何推动下一代医疗健康行业的发展

ASML 首台新款 EUV 光刻机 Twinscan NXE:3800E 完成安装

ASML为什么能在EUV领域获胜?

ASML开发的下一代EUV平台

ASML开发的下一代EUV平台

评论