本文档是基于对高速信号和电源开关的电磁干扰的实际观察编写的,这些干扰可能导致认证过程中的失败。产品中使用的组件的布局和原理图设计建议可能在数据表中提供,但实际观察和解决方案可能会有所不同。

本文档涵盖 HDMI、MIPI CSI、MIPI DSI 和以太网等高速信号。9 kHz 以上频率范围内的辐射应在认证标准规定的限制范围内。来自设备的辐射通常是 PCB 上高频时钟的多个谐波。与差分时钟相比,单端时钟辐射更多,因为单端信号的电压电平和功率更高。强烈建议在任何高速单端时钟的源端使用系列 0 欧姆电阻器。

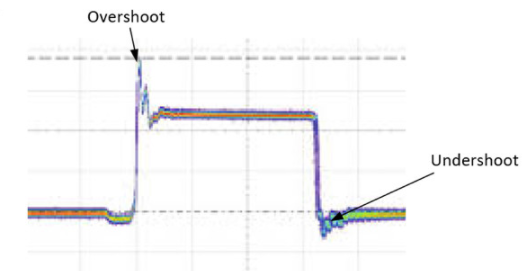

在认证过程中,增加串联电阻值有助于控制时钟中存在的过冲和下冲,这是辐射的主要原因。增加串联电阻的值有助于减少过冲和下冲。串联终端电阻的最大值可以通过接收器的建立和保持时间违规来确定。还建议尽可能不要使用重复频率。

例如,如果将两个开关部件用作电源稳压器,则确保两者的开关频率不同,因为辐射总和会超过辐射的禁止限制。时钟信号的较长长度导致辐射功率增加。例如,较长的 HDMI 电缆将充当天线,因此这种情况下 HDMI 接口的辐射会更高。

布局在辐射中起着重要作用。确保时钟信号的设计满足特性阻抗要求,并在时钟走线周围提供连续接地,以避免阻抗失配。非常准确地遵循芯片制造商的布局指南,并确保制造商从辐射角度审查特定部分的原理图和布局。芯片制造商可能会根据他们在与芯片相关的认证失败方面的经验提出一些建议来添加到新设计中。

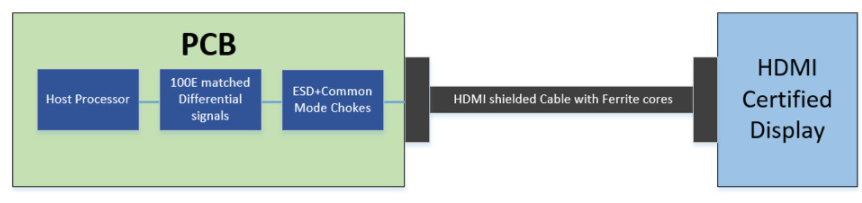

1. HDMI(高清多媒体接口)

HDMI 接口导致的 EMI 故障在嵌入式产品中最为常见。HDMI 辐射出现在 148.5MHz、297MHz、445.5MHz、594MHz、742.5MHz 和 891MHz 的基波上,通常高达五次谐波。

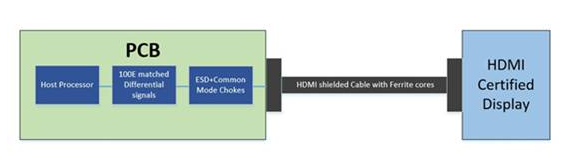

如果未经认证,辐射源可能来自 HDMI 电缆、PCB 设计或显示器本身。共模扼流圈和终端电阻/电容有助于消除 PCB 的辐射,但常见的错误发生在 HDMI 电缆选择上。来自不同制造商的不同电缆提供不同级别的发射,即使它们被屏蔽。因此,从 Molex 或 TE 等值得信赖的供应商处选择电缆非常重要。当然选择的电缆应该是屏蔽的并且有内置的铁氧体磁芯。建议携带 3-4 根不同的电缆(来自不同的品牌)进行预扫描,以验证每根电缆的性能。

以下技术有助于减少 HDMI 信号的辐射:

- 共模扼流圈应选择截止频率高于基频5-6倍。在 148.5MHz 的情况下,1GHz 以上的截止频率应该是理想的。

- 从一层传递到另一层的差分信号应确保接地过孔位于信号附近,以减少环路电感。

- 在 HDI PCB 的情况下,接地过孔应作为信号向下传输,以最短路径流回源。

- 金属外壳应利用良好的接地方案,电缆屏蔽层与外壳适当端接,使用屏蔽连接器以减少干扰。

- 在具有不同电位(接地和电源)的参考平面的情况下,建议使用拼接电容器。

- 其他一般准则,如长度匹配(10mil 对内和 100mil 对间)、阻抗匹配(100 欧姆)、实心参考平面、微带布线、较少数量的过孔、45 度弯曲是最佳实践。

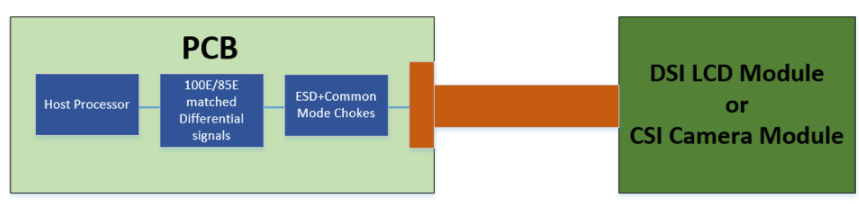

2. MIPI DSI and CSI(移动行业处理器接口)

MIPI 信号 (CSI/DSI) 是专门为移动行业设计的,因此它们是非常低功率的差分信号,并且不太可能辐射。MIPI 信号时钟因分辨率参数而异。

传输 MIPI 信号的 FPC 电缆可能会产生辐射。在定制电缆的情况下,我们在两侧添加屏蔽或接地可以立即提供帮助,但它可能会影响电缆的柔韧性。最好的方法是使用直接图层上的阴影地面作为参考地面。具有更高带宽的偏心共模扼流圈将有助于消除 PCB 中的共模噪声。MIPI 信号对于 D-PHY 具有 80Mbps-2.5Gbps 的数据速率,对于 C-PHY 具有 183Mbps -5.7Gbps 的数据速率。因此,提供一个保护环以及与其他信号至少 40 mil 的隔离是非常重要的。

以下技术有助于减少 MIPI 信号的辐射:

- 为 D-PHY 选择截止频率超过 2GHz 的共模扼流圈。C-PHY 可使用特殊滤波器来传递三重奏信号。

- 从一层传递到另一层的差分信号应确保接地过孔位于信号附近,以减少环路电感。

- 在 HDI PCB 的情况下,接地过孔应作为信号向下传输,以最短路径流回源。

- 对于 FPC 上的 EMI 薄膜,确保薄膜的末端连接到 FPC 上裸露的信号地。

- 在具有不同电位(接地和电源)的参考平面的情况下,建议使用拼接电容器。

- 其他一般准则,如长度匹配(线对内 25 密耳和线对间 55 密耳)、阻抗匹配(少数情况下为 100 欧姆/85 欧姆)、实心参考平面、微带布线、较少数量的过孔、 45 度弯曲是遵循的最佳做法。

3.以太网

以太网信号上的辐射与双绞线电缆的长度成正比。屏蔽 CAT5 电缆和电缆上的铁氧体磁芯将有助于减少干扰。

当电缆上存在的共模噪声通过机箱接地返回噪声时,差分 MDI 信号会辐射。

来自单端 MII 和电源部分的噪声会通过机箱接地耦合到双绞线,从而产生不需要的辐射。

以下技术有助于减少以太网信号的辐射:

- 以太网电缆上的铁氧体磁芯可以降低 EMI。在认证过程中保留不同类型的 CAT5 电缆。

- MDI 信号应与 MII 信号良好隔离(至少相隔 40 密耳)。

- 保持单端 MII 信号的最小长度。

- 空隙应保持在所有层的磁性元件下方。

- MDI 和 MII 信号从一层传递到另一层应确保接地通孔位于信号附近,以减少环路电感。

- 在 HDI PCB 的情况下,接地过孔应作为信号向下传输,以最短路径流回源。

- 金属外壳应利用良好的接地方案,电缆屏蔽层使用屏蔽 RJ 45 连接器与外壳适当端接,以减少干扰。

- 在具有不同电位(接地和电源)的参考平面的情况下,建议使用拼接电容器。

- 其他一般准则,如长度匹配(10mil 对内和 100mil 对间)、阻抗匹配(100 欧姆)、实心参考平面、微带布线、较少数量的过孔、45 度弯曲是最佳实践。

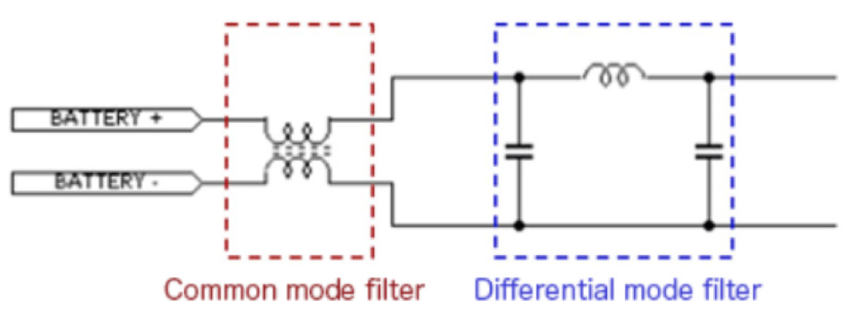

4. DC-DC电源产生

对于高速 PCB 设计,嘈杂的电源是 EMI-EMC 辐射的主要贡献者之一。稳定且噪声较小的电源肯定有助于降低 EMI。

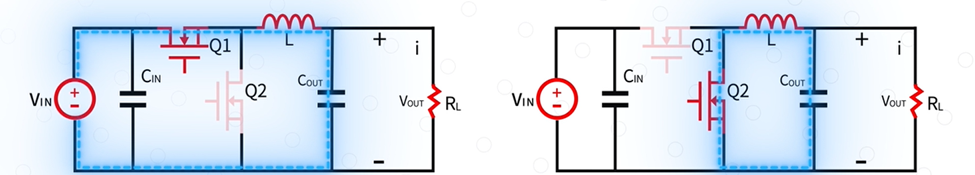

用于高速接口的处理器、内存和桥接芯片在非常低的电压下工作。在设计中选择 DC-DC 开关稳压器以获得高输出电流和效率。但是这些开关产生的开关频率、纹波(过冲和下冲)噪声会导致辐射。地面中噪声信号的耦合会增加辐射,因为地面将与电缆一起传播,电缆可以充当高频噪声的天线。

如果系统实际功耗较高(》10W)且产品涉及较长的电缆,则建议在输入直流电源处使用共模扼流圈和 LC 滤波。在线计算器可用于计算需要衰减辐射功率的特定频率的 L 和 C 值。如果空间没有限制,电感值越高越好。

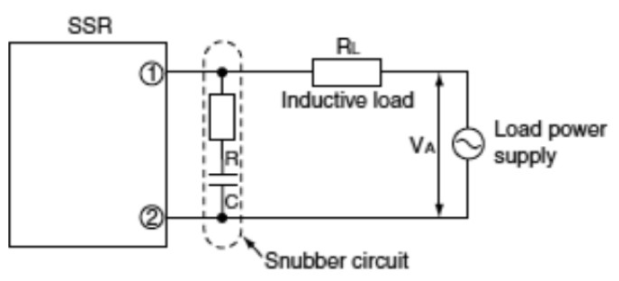

通常,在开关频率的过冲和下冲处观察到的高频(振铃)更容易辐射。

缓冲器调整将有助于减少这种过冲和下冲功率。使用更大的封装或高额定功率的电阻器,因为高频噪声会被绕过,而较小的封装可能会增加 PCB 的温度。缓冲电路应安装在电感的开关节点处。

高速 PCB 设计的注意事项

·表面贴装部分应优先于通孔部分。像电容器这样的通孔部件在 80MHz 以上时会变得更具电感性,这可能会导致更高频率的辐射/分类问题。

· 保持高速信号走线尽可能小,并尽可能提供接地以减少环路电感。

· 尽量避免堆叠中的相邻信号层或使用正交布线来减少电容耦合。

· 将去耦电容放置在非常靠近 IC 引脚的位置。这将有助于在电源和接地之间更快地切换。

· 信号采用星形布线,电源采用单点布线。

· 在电源输出上使用铁氧体磁珠。在铁氧体磁珠周围放置电容器将充当高频噪声的低通滤波器。

· 在每个》1MHz 的时钟输出上保持0E 系列终端电阻。这将有助于在出现干扰问题时进行调整。

· 对于晶体,请根据数据表选择一个考虑负载和杂散电容的并联电容器。它们是基本的辐射源,因此请遵循 IC 对晶体布线的建议。此外,尽量将晶体/振荡器保持在 PCB 的中心,而不是边缘。

· PCB 边缘的走线不应以 90 度角走线。

· 保留射频部分的屏蔽设置。FCC(对于模块化认证)是强制性的。

· 高频方波由多个高频正弦波组成。因此,请确保此类关键信号的周围应有适当的接地。

· 确保连续接地层的过孔不应形成与非常薄的铜区域连接的岛。这可以增加信号的接地返回路径。

· FR4 材料最好具有《5Gbps 时钟速度和低成本。对于高于 5Gbps 的数据,请使用 Nelco、Megatron、Rogers 等其他材料。

· 其他信号与高速信号之间保持 》3W 间距

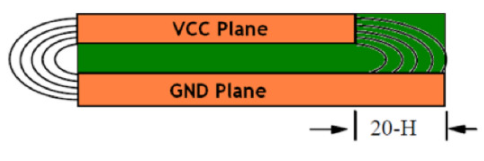

· 与接地层相比,电源层应位于 PCB 边缘内。根据经验法则,最好选择 20H。(H=层间介电厚度)

概括

本文档基于对高速 PCB 设计中 EMI 降低的实际观察。EMI 预防措施对认证非常有帮助。高速接口的辐射因设计而异,因此建议在设计中使用有助于在认证过程中进行调整的规定。

本文档涵盖了 PCB 上常用的高速信号的预防措施。几乎所有产品都观察到 HDMI 接口导致的 EMI 问题。串联、并联端接、扼流圈对减少辐射没有多大帮助。HDMI 电缆和 HDMI 显示器的变化会改变辐射功率。长电缆将充当高速接口的天线,因此如果产品连接了多条长电缆(例如,汽车产品),则需要采取许多预防措施。

作者:Kinjan Patel ,Divyesh Patel

审核编辑:郭婷

-

pcb

+关注

关注

4319文章

23080浏览量

397497 -

显示器

+关注

关注

21文章

4970浏览量

139926 -

emi

+关注

关注

53文章

3587浏览量

127606

发布评论请先 登录

相关推荐

Tips:大功率电源PCB绘制注意事项

Buck电路中PCB layout布局设计和注意事项

pcb印制板设计规则要求有哪些?你知道多少!

PCB设计的EMC有哪些注意事项

FPGA的高速接口应用注意事项

降低EMI的高速PCB设计注意事项的一些建议

降低EMI的高速PCB设计注意事项

降低EMI的高速PCB设计注意事项

评论