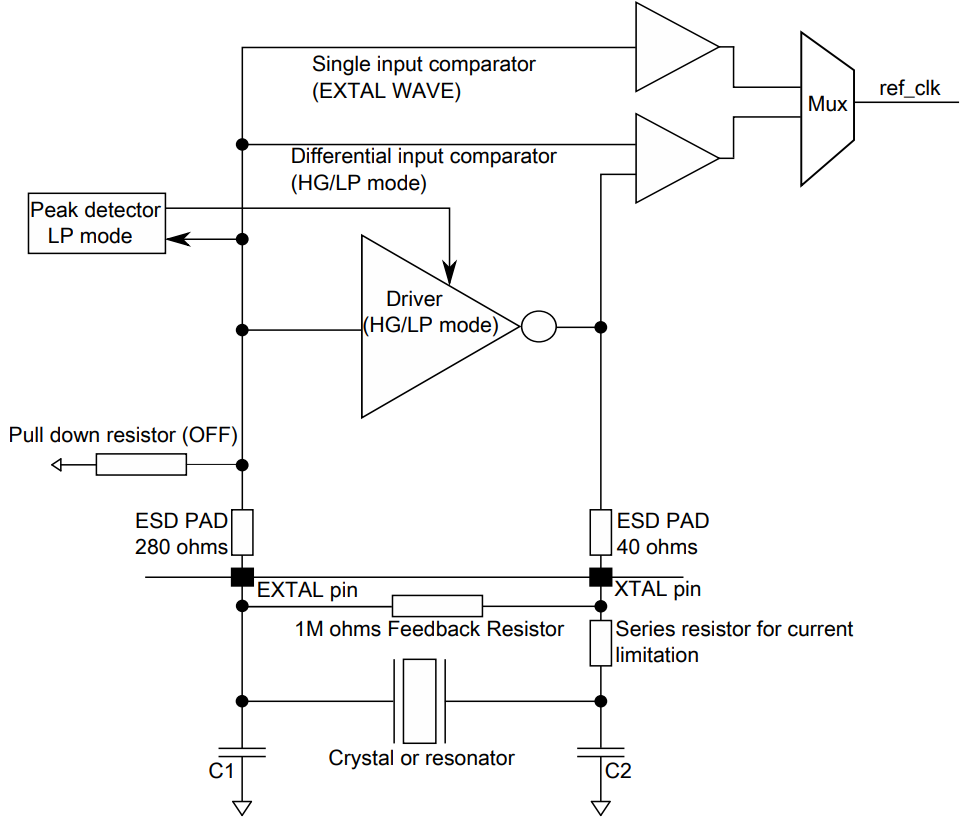

时钟(Clock)在一般SoC电路上是必不可少的,精准的时钟通常由晶振提供,晶振很难集成到芯片中去,而是作为分立元件设计在PCB上。它就像是人的心脏,如果时钟出错了,整个电路或者通信就会发生问题。比如,16MHz晶振给一个2.4G蓝牙芯片提供参考时钟,如果16MHz出现频偏,比如偏-48ppm(频率为15.999223MHz),由于射频是参考时钟倍频上去的,也会出现-48ppm的频偏(蓝牙频点变成2,399,883,450Hz,约100KHz的频偏),造成蓝牙与标准频率的对端无法通信。因此一个好的时钟电路是非常必要的,此篇文章对时钟电路中的晶振电路layout简单做一下阐述。

对于晶振电路,我们需要从几个方面考虑设计:

降低寄生电容的不确定性

降低温度的不确定性

减少对其他电路的干扰

设计注意点:

1. 晶振尽量靠近芯片,保证线路尽量短,防止线路过长导致串扰以及寄生电容。

2. 晶振周围打地孔做包地处理。

3. 晶振底部不要走信号线,尤其是其他高频时钟线。

4. 负载电容的回流地要短。

5. 走线时先经过电容再进入晶振。

下面分别举例贴片无源晶振及有源晶振的走线方式:

两脚贴片无源晶振

6. 封装较大,可从晶振中间出线。

7. 如果有测试点,使stub尽量短。

8. 走线可以走成假差分形式。尽量走在同一层。

9. 部分晶振底下需要做掏空处理,以防电容效应以及热效应造成频偏。

10. 如果是铁壳晶振,外壳做接地处理,提高抗干扰能力。

11. 晶振选型需要选工作温度达到125摄氏度及以上的。

四脚贴片无源晶振

HTOL测试板上有源晶振的布局:

由于老化测试中一般芯片都在socket中测试,所以晶振不能与Socket放置在同一面,否则晶振会距离芯片较远。

晶振放在反面则需要打孔后连接至芯片管脚,此时需要在打孔附近增加回流地孔。

有源晶振需额外注意电源滤波电路处的电容,从大到小依次靠近晶振放置。

贴片有源晶振

原文标题:PCB上晶振电路的layout设计

文章出处:【微信公众号:上海季丰电子】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

Layout

+关注

关注

14文章

408浏览量

62047 -

时钟电路

+关注

关注

10文章

239浏览量

50846 -

晶振电路

+关注

关注

7文章

92浏览量

25397

原文标题:PCB上晶振电路的layout设计

文章出处:【微信号:zzz9970814,微信公众号:上海季丰电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

时钟电路中的晶振电路layout简单阐述

时钟电路中的晶振电路layout简单阐述

评论