PCIe 仿真需要Endpoint 模型和Root Port 模型协同工作。用户一般可以采用购买BFM/VIP 来模拟对端模型也可以自己设计对端模型,更简便的方法则是使用Xilinx 提供的模型 (Xilinx Root Port model) 。

仿真例子工程介绍:

Versal 的PCIe 仿真和VU/VU+ 系列有些不一样,在endpoint 模式下,会有两种类型的example design, 默认的例子 是BMD 模式,(以前的器件默认的模式是PIO 模式 )在生成IP 后, 可以通过设置下面参数来切换产生的例子工程。

CONFIG.bmd_pio_mode {false}

用户仿真的例子一般有两个部分:

1. Root Port 模型,这个是模拟了RP 的产生config 读写,读写memory 空间并负责对收回来的数据进行检查。

2. Endpoint 用户代码部分,负责对收到的请求进行回复并且发起读写,中断请求。

在不同的测试间切换:

sample_tests.vh 定义了不同的测试名字,

sample_smoke_test0:

确认device/vender ID,运行BMD test (如果是BMD mode)

sample_smoke_test1:

确认device/vender ID,确认比较completion 数据。

RP 模型会对每一个BAR发起一次写操作,再发起一次读操作,EP 收到后会发出CPLD。PR模型会对收到的CPLD 进行检查。RP 模型可以往EP 的特定位置写特定的值使得EP发起读写或者中断。

如果要在不同的测试间切换, 可以 TESTNAME 参数,比如:

demo_tb.exe-gui -view wave.wcfg -wdb wave_isim -tclbatch isim_cmd.tcl -testplusarg TESTNAME=sample_smoke_test0

修改仿真例子:

修改提供的 example 代码可以得到自己想要的测试。

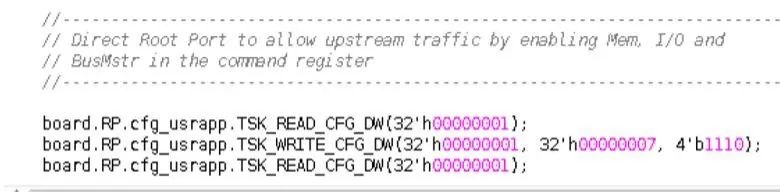

如果需要修改 Sample_smoke_test0/1 中 ROOT PORT 对自己的设置, 可以直接修改 Sample_tests.vh 下面的代码,比如下面的代码实现的是读取地址1 往地址1里面写7 再读出来的过程,实现的是bus master /memory /IO 的使能。请注意这里的地址是DW Address , 也就是这个地址1 实际上是地址4 (byte address) 也就是协议固定的command register。

可以复制以上代码 修改地址数据和byte enable 来实现对不同寄存器的操作。

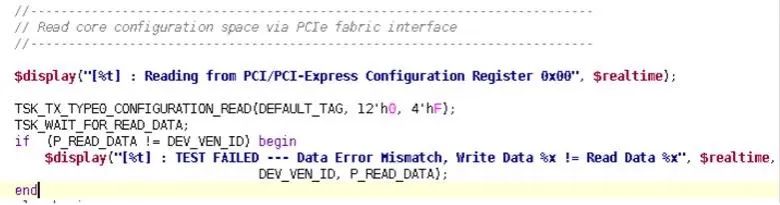

如果需要修改对于EP侧 配置寄存器的直接控制,可以修改下面的代码,填入不同的地址实现不同寄存器的读写。

如果使用其他的分支,修改的方式类似。

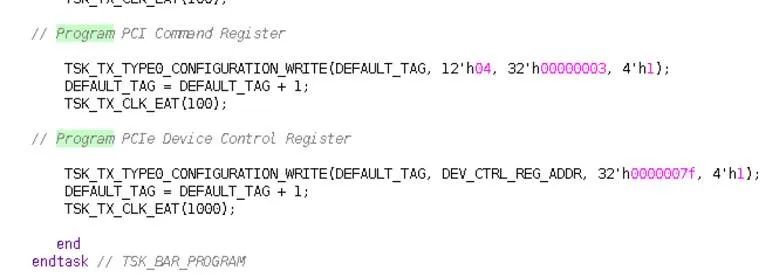

RP 模型还提供了丰富的功能来实现对PCIe EP 配置空间的操作和memory 的读写操作。这些操作大部分都用通过一些task 在pci_exp_usrapp_tx / pci_exp_usrapp_rx 中实现。比如下面的 BAR_PROGRAM 任务 就是把对BAR 的读写以及控制的过程实现了一遍。

由于BAR 读写是所有memory 请求的基础,大部分的测试都会用到,所以一般就可以直接修改这个task 来丰富测试的内容。比如可以直接在这个 task 内部 ,复制下面的语句, 把地址修改为自己需要的配置地址来实现对其他配置寄存器的操作。最常见的修改就是修改下面的语句把 32‘h00000003 修改为32‘h00000007 使得 bus master 被打开。这样 EP 就具备了发起读写操作的能力。需要修改其他寄存器也是一样的道理, 请注意这里的地址区别与上面的DW address 而是byte address。(04 表示command register)

其他的修改也是类似。

原文标题:开发者分享|Versal PCIe Example Design 仿真技巧 1

文章出处:【微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

-

Xilinx

+关注

关注

71文章

2167浏览量

121382 -

仿真

+关注

关注

50文章

4080浏览量

133586 -

PCIe

+关注

关注

15文章

1238浏览量

82639 -

Versal

+关注

关注

1文章

158浏览量

7662

原文标题:开发者分享|Versal PCIe Example Design 仿真技巧 1

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

是否采用 Versal?为什么升级到 Versal?

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

利用ORAN IP的例子工程来做仿真

仿真例子工程介绍

Versal CPM AXI Bridge模式的地址转换

如何加速PCIe仿真

AMD Versal™ Adaptive SoC CPM PCIE PIO EP设计CED示例

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

Versal PCIe仿真例子工程介绍

Versal PCIe仿真例子工程介绍

评论