详细流程:

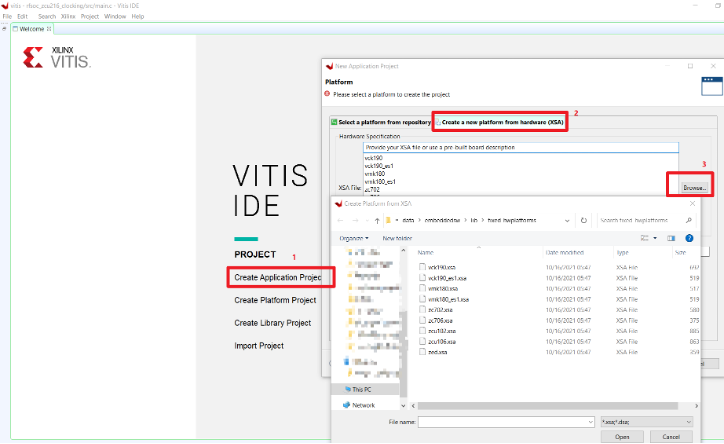

Ø 打开Vitis,选择一个Vitis工作目录。

Ø Create Application,选择一个新的XSA文件,导入从Vivado获得的XSA文件。

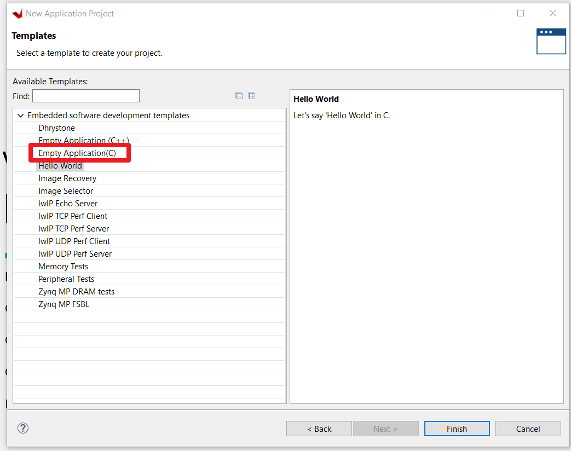

Ø为工程取一个名,以Empty Application(C)为模板新建工程。

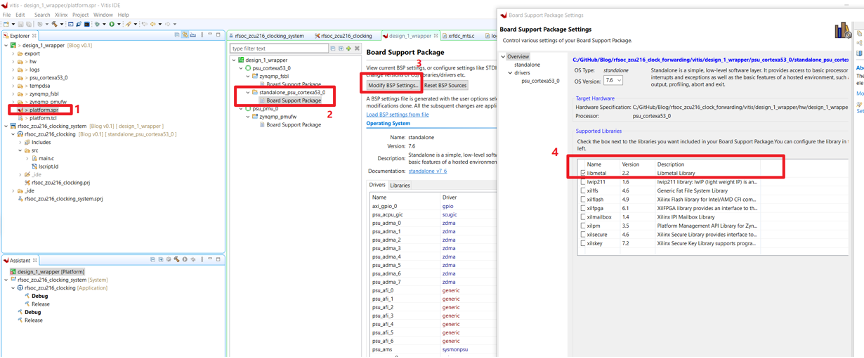

Ø勾选BSP中的库,双击platform.spr,选中standalone_psu_cortexa53_0下的Board Support Package,选择Modify BSP Settings,勾选libmetal库,保存。

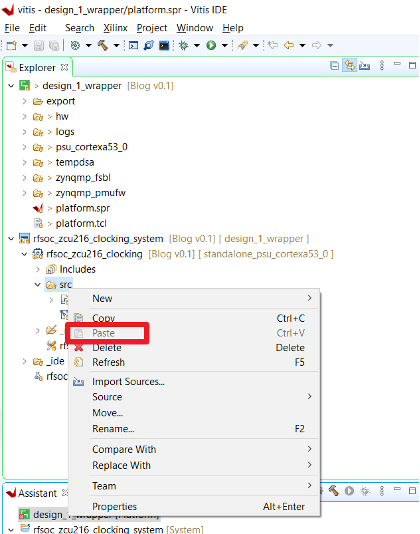

Ø 导入源码,从附件中找到main.c,可以直接拷贝到工程src目录下,或者右键src目录选择Import sources。

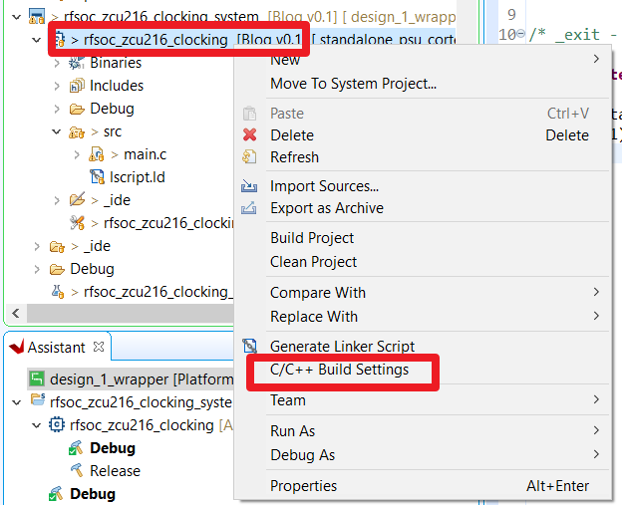

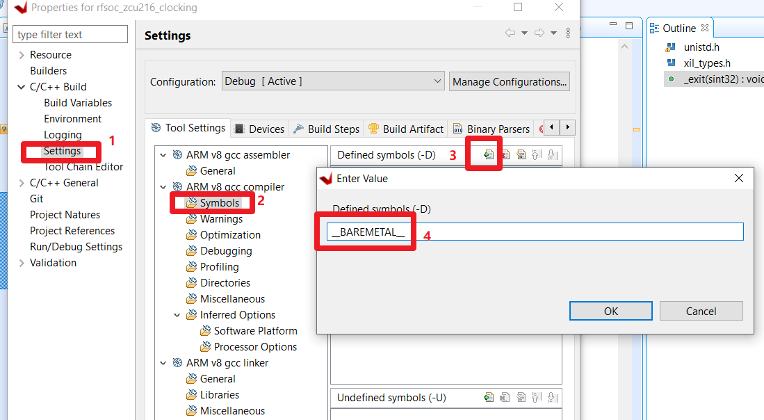

Ø 添加工程Symbol。右键工程选择C/C++ build settings,在Symbols中添加__BAREMETAL__。

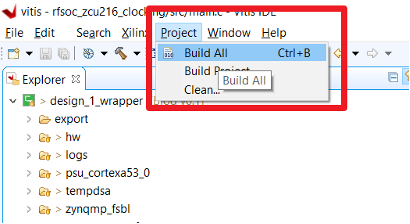

Ø 编译工程,如果有宏定义相关报错,应该是底层IP命名问题,可以在xparameters.h中找到实际的宏定义。

如何添加metal log:

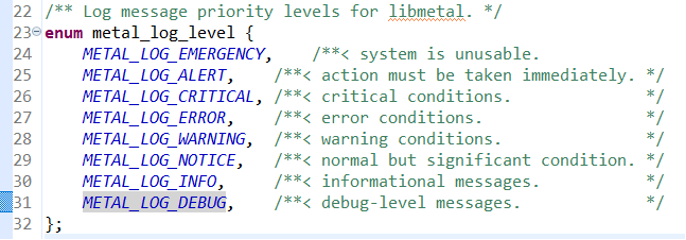

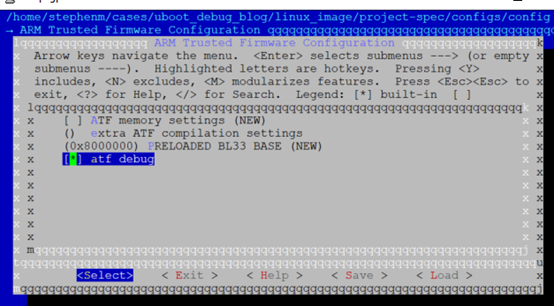

Libmetal库提供了metal_log API以便于用户调试,用户可以参考AR#71068使能打印功能:

https://support.xilinx.com/s/article/71068

Metal_log提供了8个等级的打印信息,用户可以根据项目所处的不同阶段决定开启哪一个等级的调试信息。

代码简要分析:

整体流程大致如下:

1. Libmetal初始化。

3. IIC/GPIO/SPI Mux初始化。

4. CLK104时钟IC复位。

5. CLK104时钟配置。

6. 设置RFDC Clock Distribution。

7. 查看RFDC IP状态。

这里主要强调一下三个部分,一是时钟配置,二是Clock Distribution,三是状态检查。

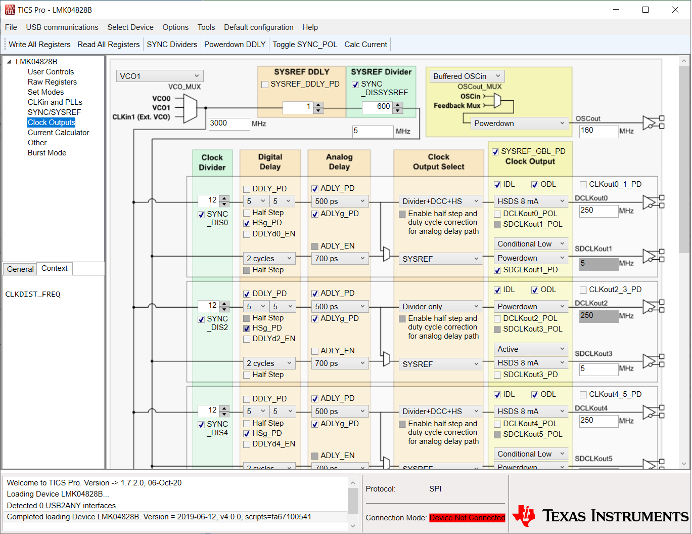

如前面章节所说,FPGA通过IIC接口与IIC to SPI桥接芯片进行交互,桥接芯片通过SPI接口控制时钟IC。配置数据在本案例中是记录在数组中的,数据来源于TI的TICS Pro软件。用户需要根据实际的需求,在软件中选择时钟IC的输入输出频率和管脚复用,由软件导出一组针对此时钟IC的寄存器数值。

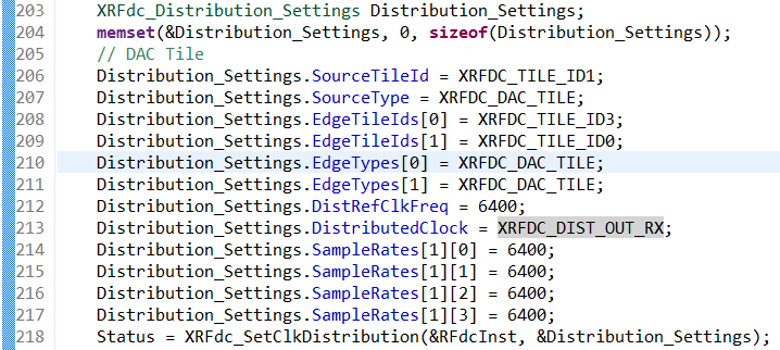

Clock Dsitribution部分,IP驱动提供了相关的结构体和API,具体组成部分可以参考PG269文档相关部分。以下是DAC Tile的时钟分发网络配置代码:

在我们目前的设计中,使用LMX2594产生的高频参考时钟输入到DAC Tile1,因此结构体中指定source tile为XRFDC_TILE_ID1;此时钟分发组内最北的是DAC Tile3,最南的是DAC Tile0;分发类型是参考钟分发,因此选择XRFDC_DIST_OUT_RX;参考钟频率为6400,采样率为6400;将此结构体传入到XRFdc_SetClkDistribution函数中,函数内部会检查当前配置是否有效,并在配置结束以后启动tile。

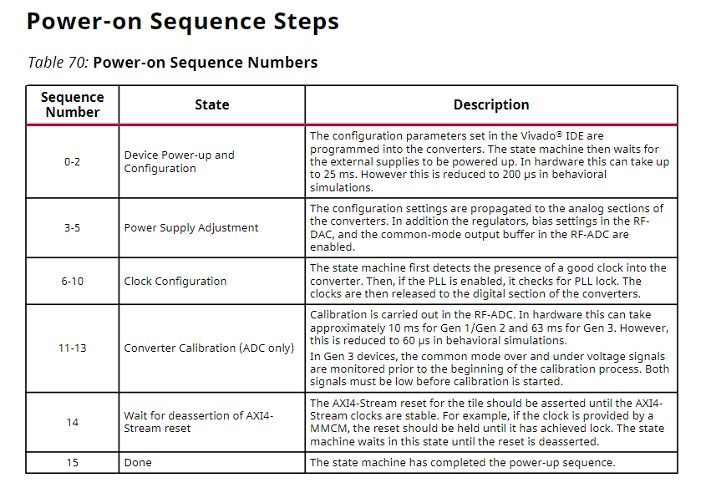

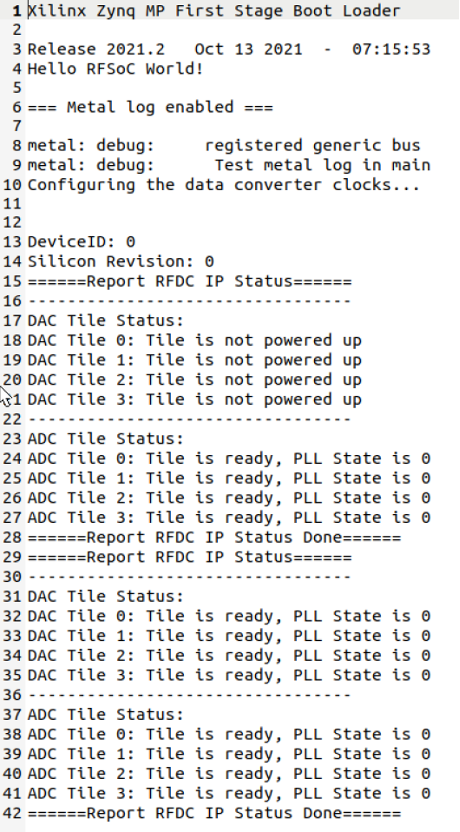

检查IP状态是最后一步,IP启动过程共有15个阶段,只有当Tile状态达到0xf的时候说明此Tile正常启动,接下来可以正常工作,如果发现Tile状态停在某一步,可以对照PG269 Power-on Sequence Steps章节查找原因。

硬件环境及测试结果:

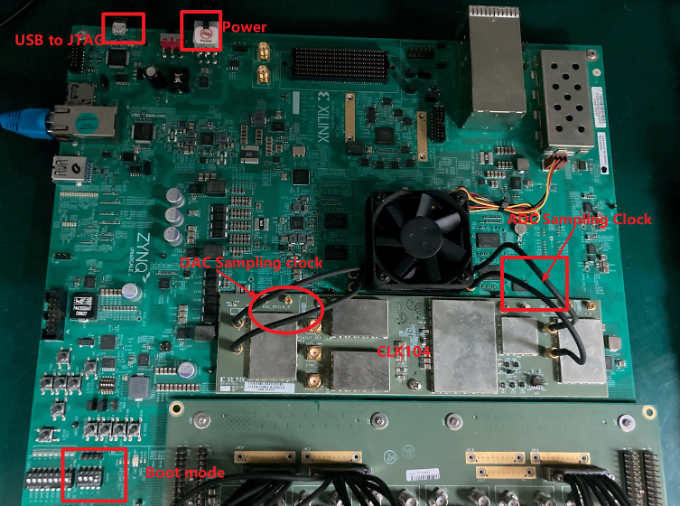

建议按照XTP587完成板子硬件环境setup:

2. 安装CLK104时钟板。

3. 使用出厂自带的CARLISLE连接线,将CLK104 ADC/DAC参考钟接到板上。

4. 设置启动模式为JTAG。

测试结果:

由打印的IP status对比可见,时钟成功配置,所有DAC和ADC Tile均进入到状态0xf。

附录:

此文章提供重建工程TCL脚本,用户可以下载附件,按照如下步骤重建Vivado工程:

1. 打开Vivado 2021.2。

-对Windows系统,双击桌面Vivado图标或到此目录寻找执行文件C:XilinxVivado2021.2invivado.bat。

- 对Linux系统,source/settings64.sh。

2. 在Vivado console中,将当前目录更换到下载的附件目录。Cd。

3. Source ./vivado_project.tcl。

Vitis工程需要用户自行创建,本文会提供测试源代码。

原文标题:开发者分享|第三代Zynq RFSoC器件射频数据转换器应用: 时钟设计-下

文章出处:【微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

-

ARM

+关注

关注

134文章

9188浏览量

369903 -

程序设计

+关注

关注

3文章

261浏览量

30490 -

Vitis

+关注

关注

0文章

147浏览量

7534

原文标题:开发者分享|第三代Zynq RFSoC器件射频数据转换器应用: 时钟设计-下

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

使用Vitis HLS创建属于自己的IP相关资料分享

基于ARM的BSP程序设计方案

ARM的位置无关程序设计在Bootloader中的应用

ARM处理器的位置无关程序设计

Xilinx Vitis能创建的模板软件工程

怎么在Vitis加速设计中为Kernel创建面积约束

在Vitis中调试ARM可信固件和U-boot

在Windows 10上创建并运行AMD Vitis™视觉库示例

在Vitis中创建基于ARM的BareMetal程序设计

在Vitis中创建基于ARM的BareMetal程序设计

评论