除了前面几篇文章讨论的内置数据类型之外,SystemVerilog还为工程师定义新的数据类型提供了一种机制。用户定义的数据类型允许从现有数据类型创建新的类型定义。

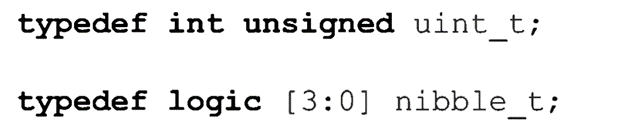

用户自定义类型是使用typedef关键字创建的。例如:

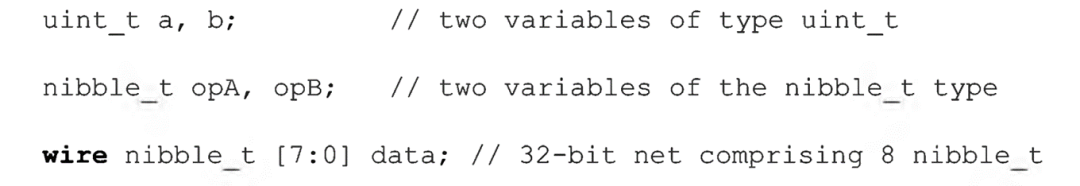

一旦定义了新的数据类型,就可以用来定义新数据类型的变量和网络:

用户自定义类型的命名约定

用户自定义类型名可以是任何合法标识符。在大型设计中,定义用户自定义类型的源代码和使用该类型的源代码可以由多行代码分隔,并且可以位于不同的文件中。如果用户自定义类型的名称与用于模块、网络或变量的名称相似,那么typedef定义和类型用法的这种分离可能会使代码难以读取和维护。

为了使源代码更易于阅读和维护,typedef名称应该使用一种命名约定,使名称明显代表用户自定义类型。两种常见的命名约定是在用户自定义类型名称中添加“_t”后缀或“t_”前缀。本文系列文章惯例使用“_t”后缀惯例。

局部typedef声明

用户自定义类型可以在模块或接口中局部定义。局部typedef声明类型只能在定义它的模块或接口中使用。构成总体设计的其他模块或接口不能引用该类型的用户自定义类型。

共享typedef定义-Shared typedef definitions

当用户自定义类型要在许多不同的模型中使用时,可以在包中声明typedef定义以供其他模块使用。

审核编辑 :李倩

-

源代码

+关注

关注

96文章

2945浏览量

66733 -

数据类型

+关注

关注

0文章

236浏览量

13618

原文标题:SystemVerilog(十)-用户自定义类型

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA算法工程师、逻辑工程师、原型验证工程师有什么区别?

labview数据类型的取值范围是多少

常见的遥感数据类型有哪些

ESP32-S3是否支持修改控制端点数据类型?

C语言数据类型有哪些

SystemVerilog为工程师定义新的数据类型提供了一种机制

SystemVerilog为工程师定义新的数据类型提供了一种机制

评论