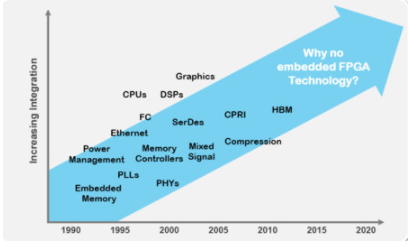

越集成越好。这在嵌入式领域比以往任何时候都更加真实。为了证明,请查看片上系统 (SoC) 格局。

在过去 20 年中,SoC 集成度稳步提高,最初包括嵌入式存储器和电源管理模块,现在集成了从模拟和混合信号 IP 到图形和数字信号协处理器再到安全和连接子系统的所有内容(图 1)。对于更高性能的应用,这一进程的下一步是启用具有硬件加速功能的 SoC,从而引入下一代 SoC IP——嵌入式现场可编程门阵列 (eFPGA)。

【图1 | 片上系统 (SoC) IP 集成的演进。]

加速向嵌入式 FPGA IP 发展

FPGA 于 1980 年代推出,其灵活性使其立即适用于需要晶体管-晶体管逻辑 (TTL) 集成和可编程 I/O 的设计,作为现成的特定应用标准产品 (ASSP) 和特定应用集成电路 (ASIC) 并不总是配备给定系统所需的端口。再加上随后几年不断增长的连接需求,这种灵活性使 FPGA 用于连接数据中心中的处理器阵列,也被部署为单独的协处理器,以计算各种信号处理应用程序中复杂的自定义并行工作负载。更广泛的使用和曝光导致 FPGA 密度、性能和成本的提高,并且该技术的市场从 1987 年的 1400 万美元激增到 2013 年的近 54 亿美元。

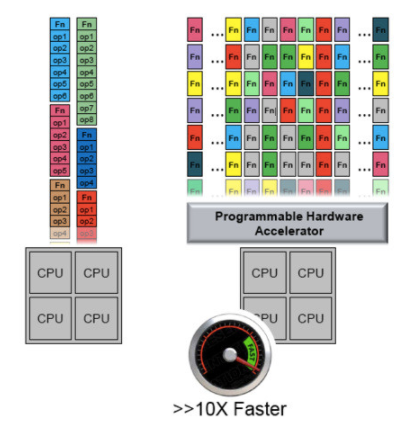

随着当今的数据中心和网络应用继续推动对更低延迟和更高性能的不懈需求,芯片制造商已开始研究将 FPGA IP 直接集成到其 SoC 设计中的好处。曾经被认为过于困难和过于昂贵,将可编程硬件加速块实现到 SoC 中的计算优势是不可否认的,因为 FPGA 不依赖于多核 CPU 的不可扩展的顺序处理范例,而是能够在一个单一的时钟周期(图2)。仅英特尔就提供了这种趋势的双重例子,因为 2015 年该公司收购了 FPGA 巨头 Altera 以保持其在数据中心市场的主导地位,

【图2 | 通过 FPGA IP 将可编程硬件加速块集成到 SoC 中,与传统的附加 CPU 串行处理相比,处理能力提高了 10 倍。]

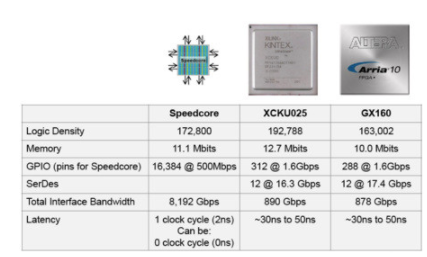

但为什么所有的乐趣都应该仅限于英特尔呢?它不是。最近,Achronix Semiconductor 发布了其 Speedcore eFPGA IP。

利用灵活性的力量

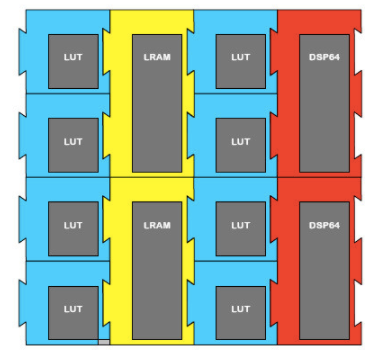

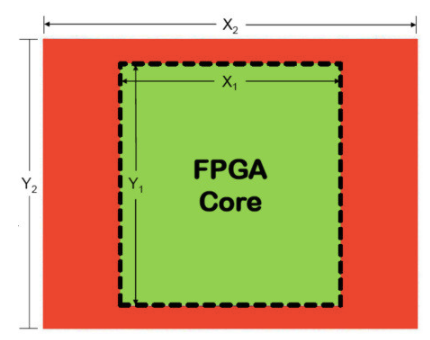

Speedcore eFPGA IP 已经酝酿了三年,其中大部分时间都在应对挑战,即制造一种具有内在灵活性的技术,而且足够坚固,可以在各种 SoC 设计中快速实施。为实现这一目标,Achronix 工程师采用了模块化架构方法,允许高效开发尺寸独特的 FPGA 内核结构,所有功能块均采用标准接口路由和单元尺寸(图 3)。因此,可以将 Speedcore IP 设想为支持多种时序收敛方法的“类似乐高”的 IP 组合、无需电源排序要求的共享或单独电源选项,以及构建可变宽度数据路径的能力。

【图3 | Achronix Speedcore 嵌入式 FPGA IP (eFPGA) 基于“类乐高”架构,允许 SoC 设计人员自定义查找表、DSP 和内存块、I/O 端口和电源的数量。]

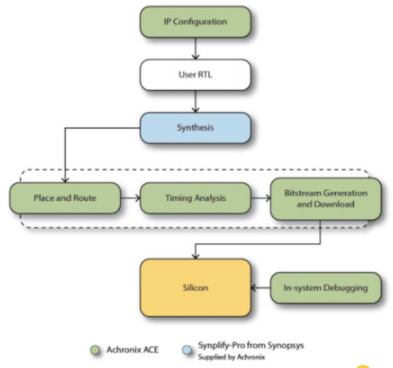

【图4 | Speedcore eFPGA IP 可使用 Achronix 的 ACE 设计工具进行配置,该工具支持常见的电子设计自动化 (EDA) 流程。]

虽然 FPGA 架构可以为 SoC 提供强大的马力,如前所述,但将其作为 IP 嵌入具有一些可能不会立即显现的辅助优势。这些都源于这样一个事实,即 Speedcore 等技术是作为 IP 而不是分立芯片实现的,从而降低了电路板尺寸、功耗、成本和延迟。

首先,就电路板尺寸而言,大约 50% 的典型 FPGA 占位面积专用于可编程 I/O、SerDes 连接器和接口控制器,所有这些都是可有可无的,因为必要的 I/O 作为核心 FPGA 的一部分存在使用直接导线连接到 SoC 的结构(图 5)。此外,还可以省去电源调节器、时钟发生器和单独的冷却设备等外围组件。

【图5 | 通过消除独立 FPGA 所需的 SerDes 连接器、接口控制器和其他组件,Speedcore eFPGA IP 可以减少电路板尺寸、延迟、功耗和成本。]

因此,印刷电路板 (PCB) 占用空间的减少、单独芯片的缺失以及其他支持组件的移除有助于降低整体系统成本(根据 Achronix 的数据,高达 90%)。此外,更少的设备加上性能的提高可以让处理任务更快地完成,这也有助于最大限度地降低功耗(该公司表示,功耗降低高达 50%)。

但回到性能方面,移除会增加延迟的 SerDes 连接器还允许直接从 FPGA 内核和主 CPU 构建宽寄存器接口路径,从而最大限度地减少与独立 FPGA 相关的通信瓶颈(图 6)。

【图6 | 在利用 eFPGA IP 的 SoC 设计中缺少 SerDes 连接器可以显着降低分立 FPGA 解决方案的延迟。]

FPGA IP 能否进入您附近的 SoC?

Speedcore eFPGA IP 目前面向需要大量并行处理的应用,例如 5G 基站的数字前端 (DFE)、软件定义网络 (SDN) 和高性能云计算,但随着数量的增加,我们能否期待在更深入的嵌入式应用中看到这种技术?

审核编辑:郭婷

-

FPGA

+关注

关注

1664文章

22545浏览量

640413 -

连接器

+关注

关注

107文章

16470浏览量

148092 -

soc

+关注

关注

40文章

4652浏览量

230507

发布评论请先 登录

max40660可以用于放大滨松H10720-20PMT吗?

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:特性、参数与应用

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:性能、规格与应用考量

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:性能、特性与应用

深入解析IGLOO2 FPGA和SmartFusion2 SoC FPGA:特性、参数与应用

探索IGLOO2 FPGA与SmartFusion2 SoC FPGA的电气特性与应用潜力

Microsemi IGLOO2 FPGA与SmartFusion2 SoC FPGA深度剖析

使用Aurora 6466b协议实现AMD UltraScale+ FPGA与AMD Versal自适应SoC的对接

搭建soc时候,可以内部接并行的flash IP,写了控制接口,转换接口,这可行吗?

Cadence受邀参加IP SoC China 2025

Altera Agilex 3/5 FPGA和SoC的功能特性

FPGA IP是否可以用于附近的SoC

FPGA IP是否可以用于附近的SoC

评论