一般情况下ILA和VIO都是用在chipscope上使用,VIO可以作为在chipscope时模拟IO。

譬如:

在使用chipscope时需要使用按键出发,但是没有设计按键或者板子不再身边,所以需要模拟按键输入还有其他信号的输出。

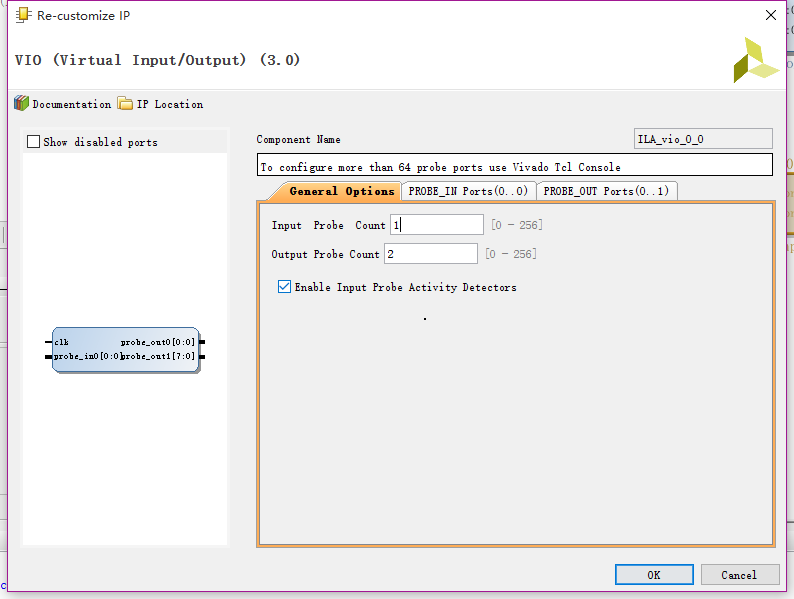

参数配置,配置输入探针数量和输出探针数量。分别可以设置0-256个。

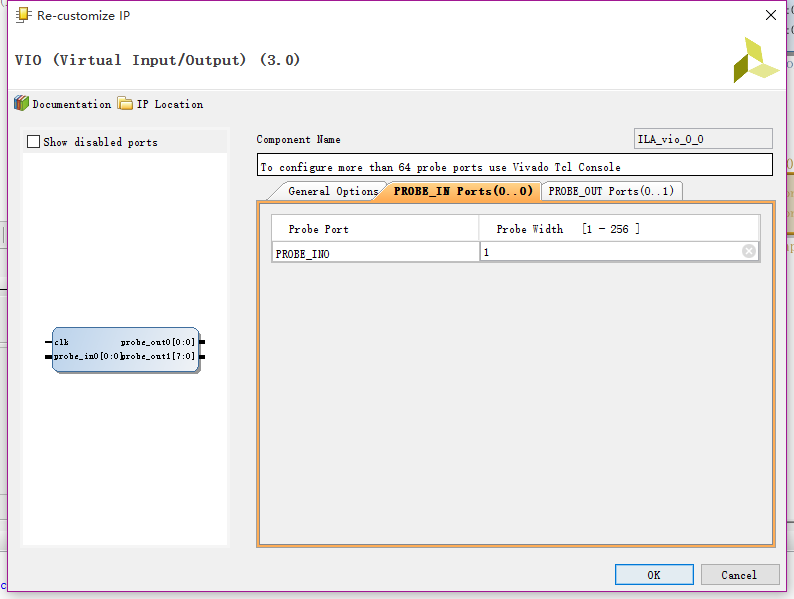

probe in ports参数配置,配置数据探针位宽

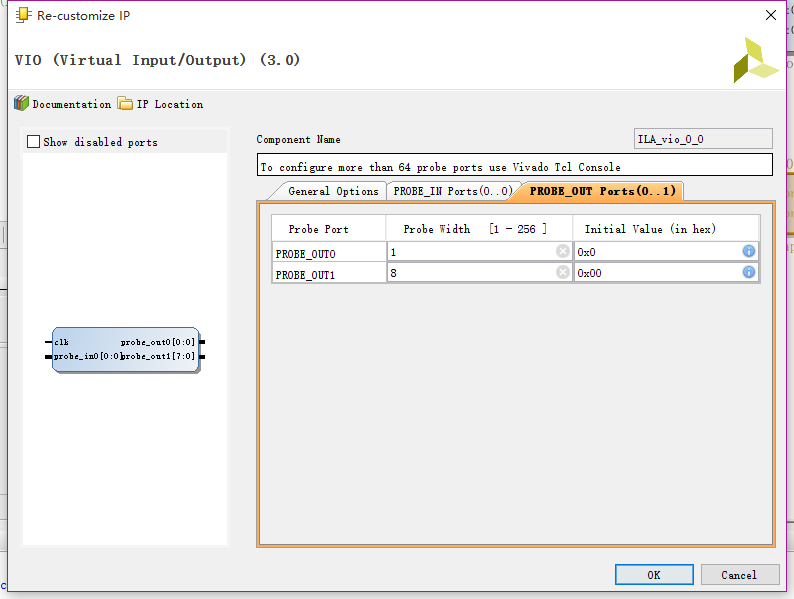

probe out port:参数配置输出探针的数据位宽,及初始化数据(in hex)

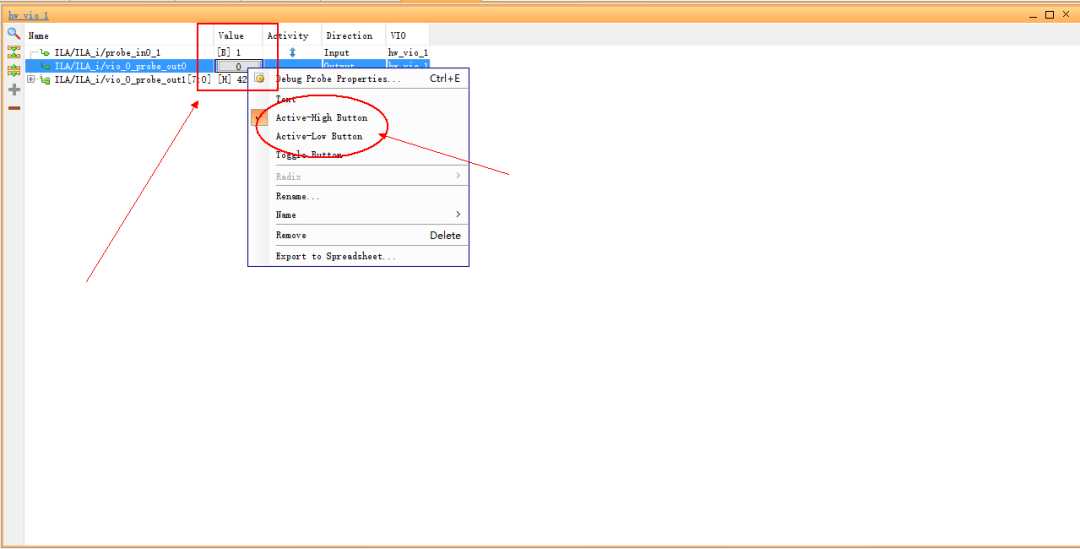

在hw_vio界面加入配置的输入及输出探针,并且对应的参数可以设置.

1、模拟的按键IO,可以设置成active_high buttom.

2、对于输出参数,可以设置成text

对于里面设置的值,就是触发后信号保持的状态数据

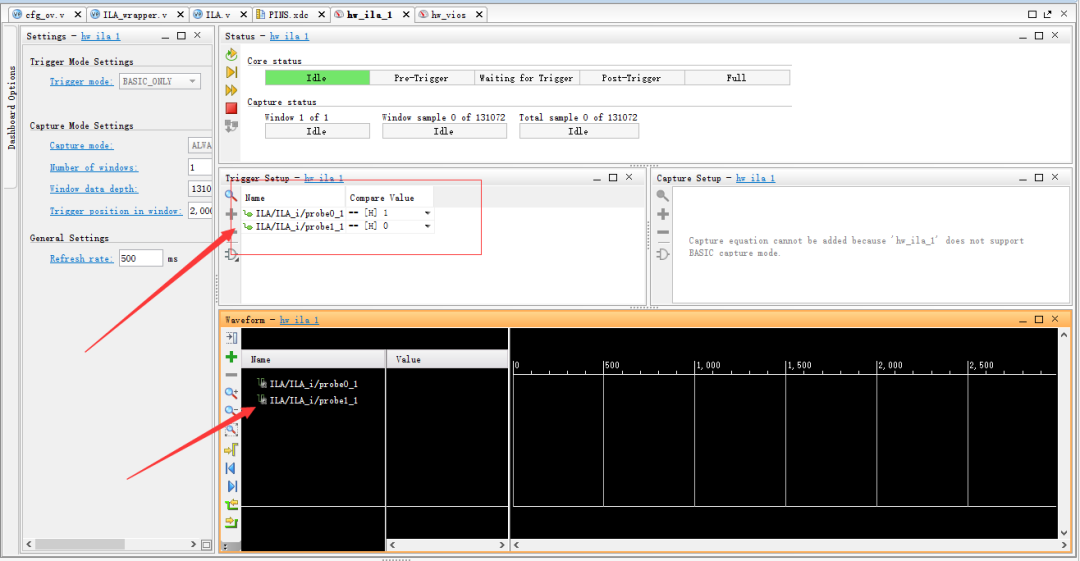

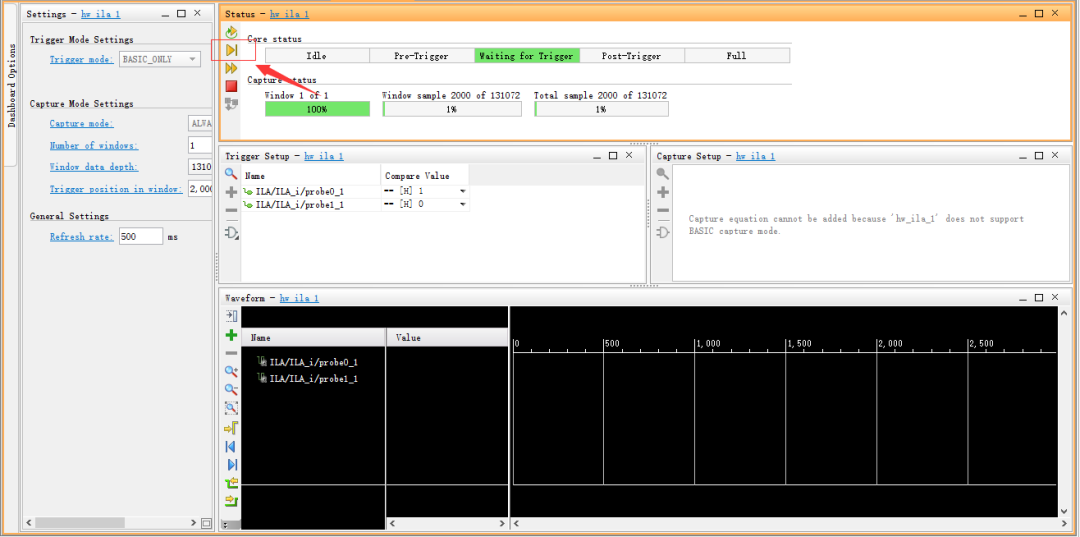

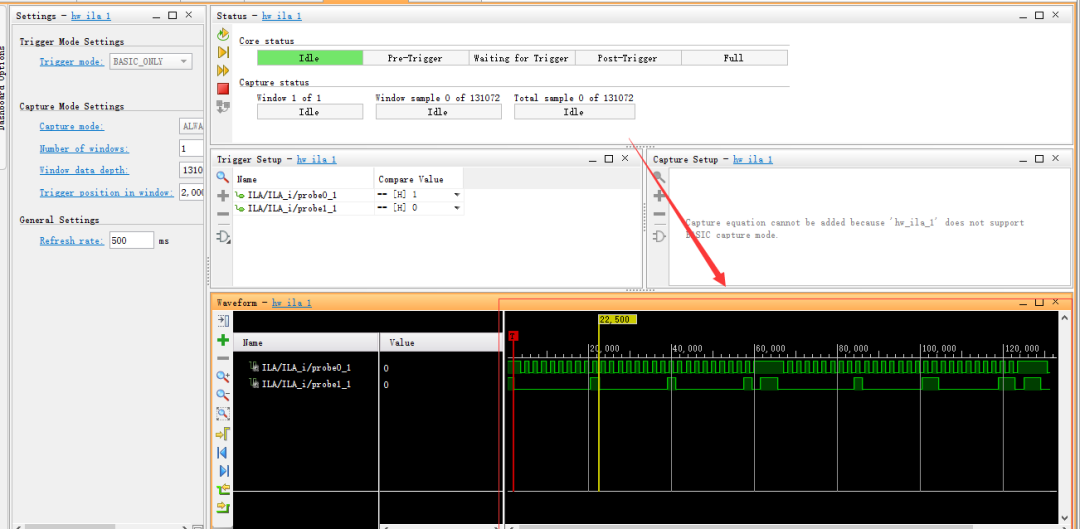

在hw_ILA界面,将ila的信号探针数据加入Trigger setup和waveform中。只要在

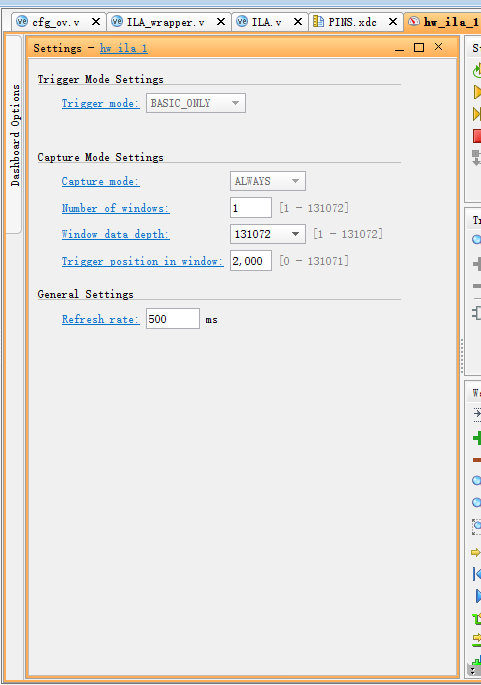

number of windows:指采样窗口个数。

window data depth:采样深度,要考虑能完整采样一帧数据以上,图上采样深度是128K = 131072 / 1024

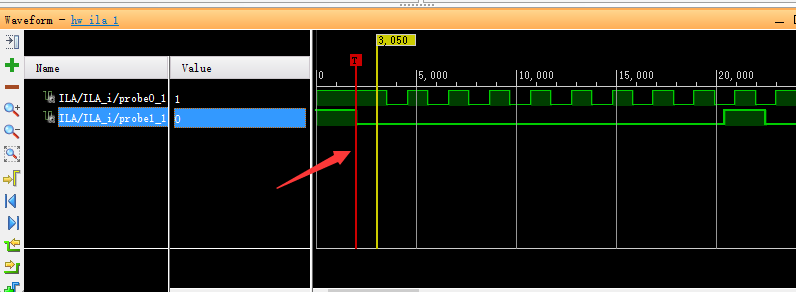

trigger position in window:窗口出发位置就是指红色那根T线。设置一个参数为的是能正常等待出发。如果设置这个值为0,那么就不需要任何触发按键或者触发源来触发。所以需要设定一个值

按启动运行按钮,让ila处于waiting for trigger模式,等待出发,然后再hw_vios上触发模拟复位按钮,

就会出发对应的信号。

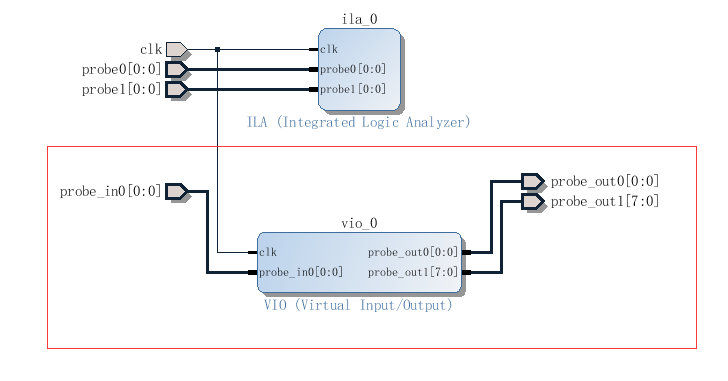

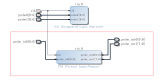

代码实例化如图所示。

ILA_wrapper ILA(

.clk ( ),

.probe0 ( ),

.probe1 ( ),

.probe_out0 ( ),

.probe_out1 ( ),

.probe_in0 ( )

)

-

VIO

+关注

关注

0文章

11浏览量

10196 -

Chipscope

+关注

关注

0文章

16浏览量

12013 -

模拟io

+关注

关注

0文章

5浏览量

2443

原文标题:vivado VIO (virtual input output)虚拟IO使用

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

XILINX FPGA Debug with VIO and TCL

求问为什么在使用chipscope的时候时钟连不上?

使用VIO IP在ISE Design SUite软件中调试时遇到以下错误该怎么办?

AD7982的VREF与VDD/VIO之间是否有时序要求?

Chipscope学习教程

Xilinx FPGA ChipScope的ICON/ILA/VIO核使用

SDK和ChipScope配合工作

VIO比chipscope有多大优势?

Vivado之VIO原理及应用

VIO在chipscope上的使用

VIO在chipscope上的使用

评论