作者:李玉童、张飞

Cadence 公司 DSG Product Validation Group

InterposerBus Routing with

Integrity 3D-IC

2.5D/3D-IC 目前常见的实现是基于中介层的 HBM-CPU/SOC 设计,Integrity 3D-IC 将以日和周为单位的手动绕线加速到秒级和分钟级,轻松满足性能、信号电源完整性与设计迭代的多重要求,为高带宽高数据吞吐量的机器学习、超算、高性能移动设备、端计算等应用提供最佳设计支持。

在迈向先进制程的进程中,硬件功能的扩展不断地受到挑战,使得超大规模计算中心和人工智能(AI)设计对运算效能和数据传输的要求不断地提高。先进系统单晶片(SoC)在尺寸上已经到了光罩的极限,因此需要找到创新的解决方案来延续摩尔定律,并且降低功耗、提高效能。

在同一封装中将晶片做 3D 立体堆叠,和使用硅中介层的多小晶片系统 2.5D 封装,已经成为新的解决方案。当然,这两种方式也面临着各自的挑战。

如今,许多设计使用硅中介层连接多个晶粒来实现 2.5D 整合。中介层的物理实现涉及晶片之间的布线(如 HBM 和 ASIC 之间)或晶片和封装基板之间的布线。空间拥塞和有限布线层数带来极大挑战。此外,片间互连通常须要经过比片上互连更长的距离,因此它们必须尽可能直线连接,减少转折及跳层次数,并且必须满足信号完整性和长距离走线特殊的要求。

传统手动布线为应对上述挑战需耗费海量人工时间,而 Cadence Integrity 3D-IC 能以更高的完成质量大大加速这一流程:

Cadence Integrity 3D-IC

自动布线解决方案的优势

极短的运行时间(以分钟为单位)

近乎 100% 的屏蔽率

均匀分布的线长

尽量少的过孔数量

1Integrity 3D-IC 平台

可以实现最佳自动布线

不同类型的产品对于 HBM 的数量和摆放位置有着不同的需求。无论 HBM 的摆放的位置如何,HBM 和 SoC 的连接都有如下共同的设计挑战。

设计挑战

1总线布线 – HBM 设计是为了满足高带宽高数据吞吐量的要求,为了使得高位宽的各个位数据同步到达,HBM 和中央 SoC/CPU/ASIC 的数据必须以物理总线模式连接。

2线长限制 – 晶粒间互联本来就很可能远长于晶粒内连线长度,所以要尽可能缩短布线长度。

3同层绕线 – 为了提高更好的信号均一特性以及减少跳层,需要尽可能多在同层绕线。

4灵活的信号线与屏蔽线配置 – 设计者有灵活配置信号线和屏蔽线的宽度以及间距甚至所用层的需求。

下图是一个比较常见的 2.5DIC HBM 和 SoC 平面布局图, SoC 居中布置,左右两边各放两个 HBM:

这些复杂的设计挑战使得后端工程师、封装工程师和系统设计工程师在使用传统工具进行中介层手动设计时不得不花费海量的时间和人力不断进行调整,而调整之后的结果也未必最佳,不得不进行大量的高时间成本和工具成本的设计迭代修正。一个典型的中介层设计常常需要数周之久。

为了解决传统工具手动设计中介层布线的痛点,Cadence 推出 Integrity 3D-IC 平台中介层全自动布线流程:

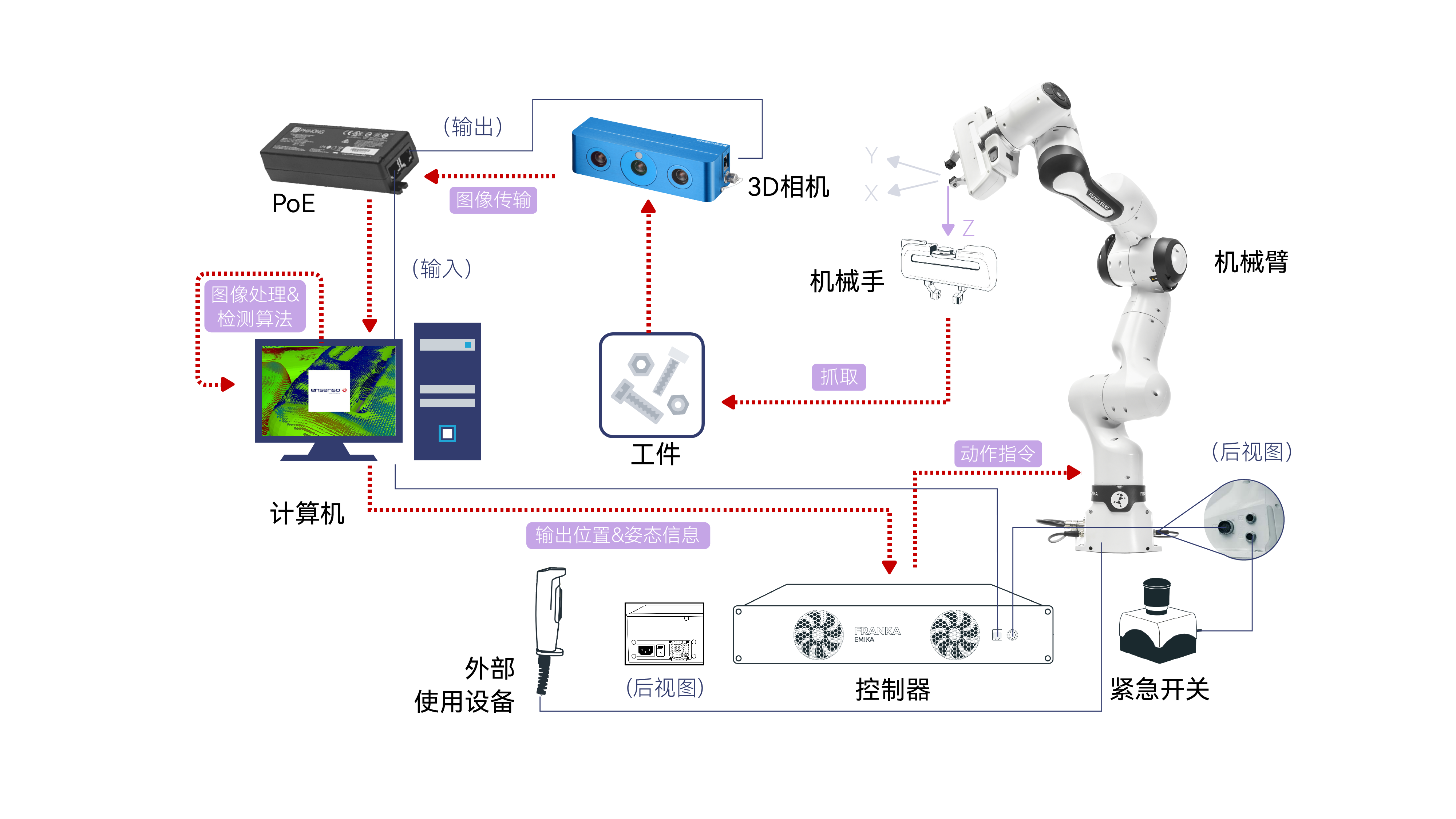

Integrity 3D-IC 可以方便的读入 Bump 摆放数据并以总线模式将来自不同晶片的 Bump 进行最佳布线连接。下图展示了针对中介层的 Integrity 3D-IC 设计流程,该流程已被广泛应用于各种 2.5D/3D-IC 设计流程中并已得到流片验证。

2Integrity 3D-IC 平台

提供简明直观的交互式用户界面

如前文所述,中介层设计中用户会根据实际产品对信号线和屏蔽线的宽度、间距、布线层提出各种各样复杂变化的定制化需求。

为此,Cadence Integrity 3D-IC 平台提供简明直观的交互式用户界面:

中介层自动布线的交互界面

1用户只需键入 Bump 区域范围和布线参数工具就会自动抓取指定区域的 Bump,并根据指定的参数,对 Bump 自动分组,并选取优化的布线组合。

2如果用户没有指定 Bump 区域,Integrity 3D-IC 会扫描整个芯片,把符合 HBM 形式的 Bump 全部抓取出来并自动分类。

3信号线的宽度和间距可以通过设计规则指定,也可以由用户直接指定。屏蔽线的宽度和间距可由用户界面指定,也可以由 Integrity 3D-IC 根据屏蔽参数在信号线中间自动计算预留空间以确保屏蔽的有效和完全。

此外批处理布线模式允许用户生成脚本文件,以便保存和复现。Integrity 3D-IC 还可以根据布线的资源自动计算宽度和间距,在需要的时候还可以考虑 45 度连接。最终通过超级命令 Route Design-Bump 将所有 Bump 连接布线自动完成。

3Integrity 3D-IC 平台

中介层自动布线实例

在主干(Trunk)部分,Integrity 3D-IC 严格地使用总线模式布线,并用同一层金属尽可能的延伸到 Bump 附近。为了减少过孔的使用,即使在 Bump 附近,Integrity 3D-IC 也是用同一层金属拐弯而不跳线,尽可能保证线上电阻和电容的均一性。在 Trunk 部分,屏蔽率是 100%,在接近 Bump 的布线,短线部分缺省不加屏蔽。用户可以选择是否要把高层的短线和引脚一起都加上屏蔽。

Trunk 部分的屏蔽率是 100%

Bump 区域布线

两侧 Bump 区域有偏移

当用户使用多于 6 个 HBM 时,由于 SoC 尺寸小。HBM 的 Bump 无法和 SoC 的 Bump 完全对齐。如果采用 90 度的折线拐弯,既浪费布线资源,又会造成线长差异。Integrity 3D-IC 检测到这种情况会自动采用 45 度布线方式:

45 度折线局部细节

虽然我们强烈推荐用户使用全自动布线以实现分钟级的快速布线,Integrity 3D-IC 也提供强大友好的编辑复制功能。但在一组 Bump 布线完成后,用户可以对这组布线进行眼图仿真,当 SI/PI 都达到指标后,用户可以选中这一组的线和过孔,通过灵活的平移、翻转、旋转的动作把线和过孔复制到另一组 Bump 上,Integrity 3D-IC 会自动对目标 Bump 完成同样的布线连接。

Cadence Integrity 3D-IC 能将日趋复杂的 2.5D/3D 中介层布线速度提高上万倍(周分钟),从而大大加快设计的迭代速度,为复杂电子系统的设计者们提供了无限优化的可能!

原文标题:3D-IC 设计之中介层自动布线

文章出处:【微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

3D

+关注

关注

9文章

2921浏览量

108131 -

IC设计

+关注

关注

38文章

1302浏览量

104355 -

Cadence

+关注

关注

65文章

931浏览量

142556 -

布线

+关注

关注

9文章

779浏览量

84471

原文标题:3D-IC 设计之中介层自动布线

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Cadence宣布收购Secure-IC

Cadence收购Secure-IC强化嵌入式安全布局

加特兰集成Cadence DSP,升级汽车成像雷达解决方案

Cadence与Samsung Foundry开展广泛合作

Cadence展示完整的PCIe 7.0 IP解决方案

剖析 Chiplet 时代的布局规划演进

Samsung 和Cadence在3D-IC热管理方面展开突破性合作

Cadence与Intel Foundry的战略合作取得重大成果

Cadence与台积电深化合作创新,以推动系统和半导体设计转型

解决方案|基于3D视觉技术的铝合金板件刷油烘干自动化上下料

3D-IC 以及传热模型的重要性

Cadence Integrity 3D-IC自动布线解决方案

Cadence Integrity 3D-IC自动布线解决方案

评论