无论是用作独立处理元件还是与辅助处理器结合使用,SoC FPGA 都提高了嵌入式处理的安全性。虽然可以构建具有执行监控和静态密钥存储的专用安全设备的嵌入式处理器模块,但在 SoC FPGA 中整合系统关键功能和安全特性可提供更高的安全性、灵活性和性能。

Linux 已成为嵌入式设计中裸机系统的日益流行的替代方案。随着 32 位计算成为一种商品,并且像 Yocto 这样的项目使得为嵌入式应用程序创建、开发和维护基于 Linux 的系统变得更加容易,它的受欢迎程度可能会增长。Linux 使 OEM 变得更像初创公司,其敏捷的硬件开发团队可以通过使用操作系统来抽象底层硬件细节来加快上市时间。尽管有好处,但如果没有适当的方法来启动其嵌入式处理器,Linux 系统可能容易受到 rootkit 的攻击。对于新兴的物联网而言,Rootkit 尤其成问题,它将产生数十亿个新的、可能不安全的端点。

通常,rootkit 会尝试访问特权 (root) 模式,同时躲避系统恶意软件检测工具。恶意软件还可能通过修改系统的启动过程来尝试将自身安装到持久状态。如果成功,感染将是永久性的或通过电源循环持续存在。从那里,恶意软件会做其作者想要做的任何事情,包括记录击键、形成僵尸网络、收集个人信息和启用未经授权的服务。一旦系统被感染,可能需要重新安装完整的操作系统。

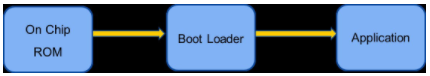

问题从嵌入式处理器开始,通常如图 1 所示启动。上电时片上 ROM 将从外部非易失性存储器中获取启动加载程序。引导加载程序是特定于应用程序的,并在其启动期间配置处理器以满足指定的应用程序要求。时钟、缓存、内存控制器和外围设备都已配置。一旦处理器被初始化,应用程序就会从外部非易失性存储器中取出,有时会被解压缩,然后复制到启动应用程序的快速外部易失性存储器中。

图 1:嵌入式启动过程。

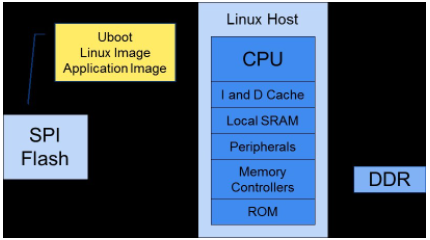

在引导过程中,恶意软件有机会尝试修改嵌入式系统的引导加载程序。图 2 显示了嵌入式 Linux 系统的简化典型框图。UBOOT、Linux 内核和应用层都存储在易于访问的非易失性存储器中。

图 2:嵌入式 Linux 系统。

保护启动过程的唯一方法是使用一个可以信任的实体来保护它,该实体始终以预期的方式运行。作为系统元素,此信任根支持系统、软件和数据完整性和机密性的验证,以及将信任扩展到内部和外部实体。它是创建所有进一步安全层的基础,并且它的密钥必须保密并且它遵循的过程是不可变的。在嵌入式系统中,信任根与其他系统元素一起工作,以确保主处理器仅使用授权代码安全启动,从而将信任区域扩展到处理器及其应用程序。使用加密技术,可信区域可以扩展到覆盖手头系统的所有关键元素,

虽然许多较新的处理器具有支持安全启动的特殊功能,但处理器芯片中对安全启动的内在支持远非普遍,并且通常需要多芯片解决方案。更好的解决方案是基于闪存的 FPGA,它提供了多芯片嵌入式系统中最好的信任根设备之一,显着提高了主嵌入式处理器运行的任何代码都是真实的保证水平。

基于闪存的解决方案本质上更安全(一旦它们被编程,关键信息永远不会离开芯片),今天基于闪存的 SoC FPGA 解决方案还提供了许多额外的高级安全功能,包括片上振荡器、加密服务加速器、安全密钥存储、真正的随机数生成器、安全嵌入式闪存 (eNVM) 中的片上启动代码存储以及高速串行外围接口 (SPI) 闪存仿真,以实现外部处理器的高速安全启动。 与早期解决方案相比,这些设备还具有更强的设计安全性,并包括差分功率分析 (DPA) 抗篡改措施。再加上嵌入式 Linux CPU,它们可以有效地防止恶意软件试图修改嵌入式系统的引导加载程序。

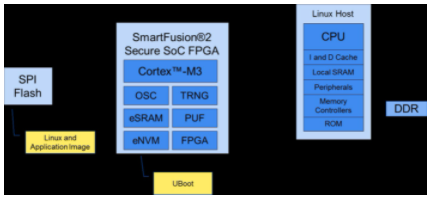

图 3 提供了一个可用于安全启动的基于闪存的 SoC 示例。Microsemi 的 SmartFusion2 SoC 中的 eNVM 用于存储 UBOOT,其 FPGA 结构可快速模拟 SPI 闪存。CPU 不知道这个 SoC 在它和 SPI 闪存之间。上电时,SoC 将 UBOOT 的 SPI 读取请求从内部 eNVM 定向到 CPU。然后 CPU 执行正常的 UBOOT 引导过程,然后从外部 SPI 闪存中获取应用程序映像的其余部分,在后一阶段,SoC 充当外部存储器的管道,并将应用程序映像传递给 CPU。SoC 及其内部 eNVM 只能使用经过验证的加密比特流进行编程,该比特流只能由 SoC 的 FPGA 开发环境构建。比特流文件格式是专有的,任何人都无法使用,并且由于 Cryptography Research Incorporated(现为 Rambus)许可的受专利保护的对策,可以抵抗 DPA 侧信道攻击。换句话说,恶意软件尝试写入闪存的唯一方法是拥有一个专为 SoC 设计的比特流,具有适当的加密和用户定义的密钥。

图 3: SmartFusion2 用于存储 UBOOT。

为确保安全的多阶段启动,在交付和执行之前验证代码至关重要。这确保不会发生可能破坏或损坏每个阶段的引导的妥协,并且可以使用对称或非对称密钥加密技术来完成。优选地,对每个先前阶段的持续反馈用于确认在引导加载期间没有发生篡改。如果所有防篡改 (AT) 监视器都确认环境安全,则每个阶段都可以继续执行。

如果需要,今天的 SoC FPGA 还可以独立提供运行时监控和纠正措施或惩罚。为此,所有应用程序代码都将位于 SPI 闪存中,并且可以选择加密。SoC 将对每个阶段的代码进行真实性检查,解密代码(如果需要),并在通过 MPU 到 FPGA SPI 接口请求时将其提供给主 MPU。为了增加安全性,引导加载程序代码将存储在 SoC FPGA 的 eNVM 中。

上电后,FPGA 将保持主 MPU 处于复位状态,直到它完成自身的完整性自检。准备就绪后,它将释放复位。MPU 将被配置为从接口引导到 FPGA(例如,通过其 SPI 接口)。作为 SPI 从机的 FPGA 将在 MPU 完成复位时将请求的 Phase-0 引导代码传送到 MPU。假设 MPU 本身不支持安全启动,挑战是将一些代码加载到 MPU 中,并高度保证它没有被篡改。

如果一切正常,引导过程将通过跳转到 MPU SRAM 中现在受信任的代码来继续。这将包含启动下一阶段所需的代码,并且可能包括现在受信任的 RSA 或 ECC 公钥。一旦 MPU SRAM 中的代码被信任,就可以采用额外的安全措施,例如使用公钥方法建立共享密钥,并使用该共享密钥加密 FPGA 和 MPU 之间传输的所有后续引导代码。此外,可以将系统的所有硬件组件以密码方式绑定在一起,因此如果没有原始系统的所有确切组件,任何一个都无法工作。

SoC 还可以提供对模块环境条件的实时监控,例如温度、电压、时钟频率和其他因素。FPGA 架构可以安全地配置为为外部篡改传感器和入侵检测器提供 I/O。这些可以被 SoC 感知,以防止受到已知漏洞攻击的漏洞,这些漏洞应用异常条件来提取关键信息。通过适当的设计可以实现更高的安全级别。

审核编辑:郭婷

-

传感器

+关注

关注

2552文章

51228浏览量

754691 -

处理器

+关注

关注

68文章

19348浏览量

230268 -

嵌入式

+关注

关注

5087文章

19145浏览量

306144

发布评论请先 登录

相关推荐

采用Xilinx FPGA的AFE79xx SPI启动指南

UID加密安全启动原理分析

识别IP地址威胁,构筑安全防线

亚马逊云科技如何追踪并阻止云端的安全威胁

工业控制系统面临的网络安全威胁有哪些

Linux启动流程基本分析

人为疏忽是对数据安全的最大威胁

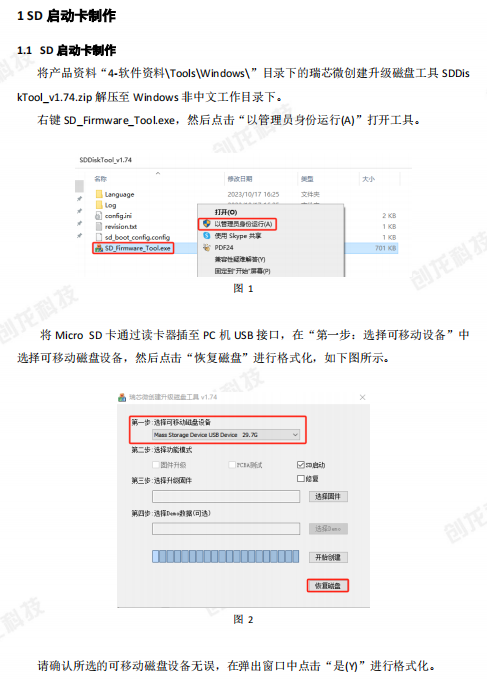

3562-Linux系统启动卡制作及系统固化

FPGA安全启动设计防止Linux rootkit威胁

FPGA安全启动设计防止Linux rootkit威胁

评论