随着雷达和无线通信系统中的信号处理从模拟转向数字,人们在开发先进的波束成形技术以实现新应用方面付出了巨大的努力。使用数字方法精确引导波束的能力,最常见的是快速傅里叶变换 (FFT),导致雷达和移动电信系统的设计方式发生了重大变化。

波束成形可以切换或自适应。例如,在切换波束成形中,移动电信基站从预先定义的波束选择中进行选择,每个波束都基于接收到的信号的强度以特定方向为目标。当用户相对于天线阵列移动时,信号被切换到阵列中的其他元件,这些元件定位得更好,以在特定方向上提供更强的信号。另一方面,自适应波束形成依赖于实时计算,允许基站在目标用户的方向上发射更多聚焦的波束,同时减少其他方向的输出,从而大大减少元素之间的干扰。

自适应波束成形设计需要非常高的处理带宽——每秒必须执行数十亿次乘法和累加操作。因此,接收系统抑制噪声源和干扰变得更加重要。同时,必须保持对天线阵列中每个元件的实时方向控制。为了实现这一点,有必要对每个天线元件接收到的信号进行数字化处理,同时使用元件级处理。由于需要繁重的计算负载,传统的 CPU 和 DSP 在自适应波束成形应用中可能会迅速负担过重。然而,性能更高的 FPGA 非常适合该任务,因为它们具有嵌入式 DSP 模块、并行处理架构和增强的存储器功能。

全球对移动宽带数据和语音服务不断增长的需求不断推动无线网络运营商扩展和升级其网络以提供更多容量。运营商同时试图最大限度地增加每个无线基站可以支持的用户数量,以降低其基础设施成本,同时保持对用户有吸引力的价格点。

由于可用无线频谱的数量有限,这项工作变得复杂,因此增加的流量会产生更多的干扰,通话质量也会受到影响,部分原因是天线技术的限制。全向天线通常用于在蜂窝塔上进行发送和接收。然而,这种传统方法(其中天线充当传感器,将电磁能转换为电能)效率不高,并且由于单个塔上存在大量信号而受到高度干扰,从而降低了整体连接性。

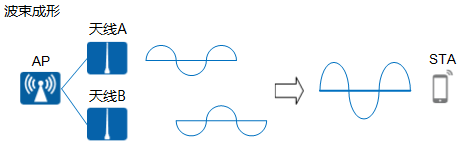

这种干扰可以通过使用在同一塔上组合在一起的定向扇区天线来减轻。这些自适应阵列天线或智能天线已越来越多地用于电信网络,以提高无线连接质量并提高整体容量。这是通过波束成形技术实现的,该技术通过使用先进的数字信号处理将来自基站的波束引导至各个用户。波束成形调整每个传入和传出信号的功率和相位,以创建沿特定方向传播的波束,同时减少非必要输出。这减少了单个信号对彼此造成的干扰量,并提高了所有连接的质量。

创新的自适应波束形成算法的出现导致在信号处理中使用浮点算法的增加,以通过实现实时目标跟踪来最大限度地减少干扰并提高雷达容量。这是通过使用 QR 分解 (QRD) 和权重反向替换 (WBS) 等算法同时创建多个点光束来实现的。这些算法有助于波束的自适应形成,同时减少噪声和干扰,但它们每秒需要大量的浮点运算。

由于许多雷达系统的尺寸、重量和功率限制,使用传统 CPU 或 GPU 选项并不是最佳方法,因为执行浮点计算所需的硬件数量增加。由于需要更多的内存、功率和空间,更不用说更高的成本、更复杂的系统设计和延长的集成时间,因此使用多个 CPU 对雷达系统的设计产生了重大影响。基于 CPU 的设计进一步受到有限的内存和接口选项的限制。

FPGA 在采用先进数字波束形成技术的雷达系统中提供了优于 CPU 和 GPU 选项的巨大优势,因为它们可以降低成本、复杂性、功耗和上市时间。由于其在自适应波束成形应用中处理高度并行浮点运算的卓越能力,FPGA 可以提高算法性能,同时显着降低功耗。

FPGA 也更高效,因为一个设备通过诸如 PCIe 和 Serial RapidIO 等 I/O 标准从天线阵列中每个元件捕获的信号中接收和处理大量数据。除了提供更高性能的处理之外,这样的系统还不需要安装在需要超过 1,000 W 的 VPX 机箱中的大量耗电的多核 CPU 板。流线型的单 FPGA 设计还受益于外部存储器和其他额外的单块电路板上提供的功能小于 80 W。

智能天线和自适应波束成形的使用,虽然几十年来在军事和国防应用中很常见,但由于与广泛部署相关的高昂成本,直到最近才在商业蜂窝网络中广泛使用。随着高性能、低成本 FPGA 和 DSP 的兴起,自适应波束成形在 2000 年代初进入了 3G 移动基础设施,该技术现在被广泛用于扩展 4G 网络。这为硬件和固件设计人员提供了新的机会,可以改进用于国防和商业应用的波束成形方法。

审核编辑:郭婷

-

FPGA

+关注

关注

1663文章

22494浏览量

638983 -

cpu

+关注

关注

68文章

11324浏览量

225836 -

gpu

+关注

关注

28文章

5266浏览量

136040

发布评论请先 登录

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:性能、规格与应用考量

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:性能、特性与应用

基于FPGA的DAQ系统|实现高性能数据采集的挑战

AI波束管理测试系统和信道模型简化实现方案

AMD 推出第二代 Kintex UltraScale+ 中端FPGA,助力智能高性能系统

AMD UltraScale架构:高性能FPGA与SoC的技术剖析

波束成形技术:从原理到实践,如何精准控制无线信号方向?

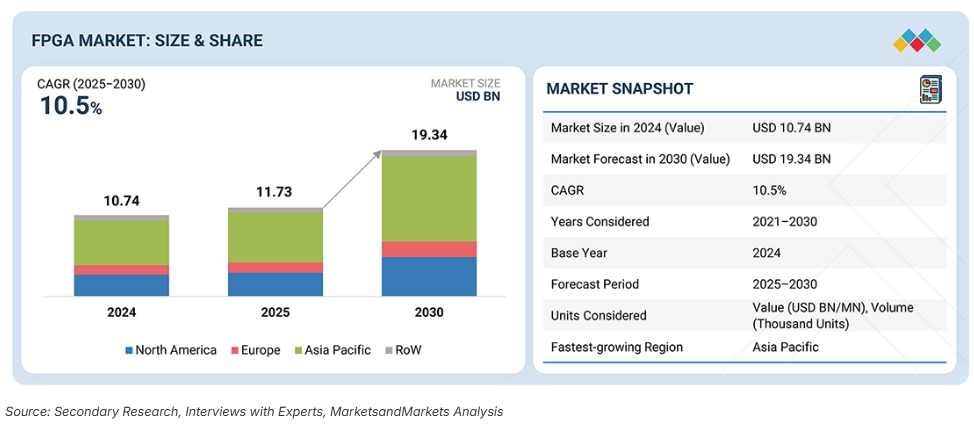

MarketsandMarkets FPGA行业报告,2026~2030 FPGA市场洞察

FPGA可以提供更好的波束赋形性能

FPGA可以提供更好的波束赋形性能

评论