虽然嵌入式市场中多核处理器的可用性并不是什么新鲜事,但今天的软件工程师可以找到各种同质设备以及复杂的异构片上系统 (SoC) 作为他们设计的选项。这种高水平的多核集成提供了许多好处,包括更小、更低成本、更低功耗和更高性能的最终产品。

在工具和框架领域取得了进步,一些产品增加了编程范式,以帮助缓解围绕这种复杂性的开发挑战。然而,如果软件架构师不能最大化多核处理器设备中每个计算元素的处理能力,那么高度集成的多核 SoC 所提供的价值就会被打折扣。

软件工程师通过确定特定多核设备上的功能的标准方法来寻求完整的多核权利。虽然市场上有比较简单的、通常是单核处理器的性能的标准基准,但它还没有这些标准的基准或方法来比较复杂 SoC 的多核性能(或多核权利),这使得软件架构师很难为他们的设计选择最好的处理器。

基准测试挑战

在处理器简单且计算性能是唯一关注点的时代,对 CPU 性能进行基准测试相对容易。随着处理器架构的发展,基准测试挑战也随之而来。根据 Merriam-Webster 的说法,基准的定义之一是“作为衡量或判断他人的标准的东西”。换句话说,基准测试不是绝对的,而是相对的活动。当处理器架构的优势和劣势存在显着差异时,其中存在根本挑战:知道如何规范这些差异以制定既公平又准确的衡量标准。在实践中,这个问题很少得到解决,最终用户会留下难以以直接方式比较的措施。

迄今为止,传统的基准测试已经很好地服务于嵌入式处理器市场,尽管其方式有限。这些基准测试易于理解且范围有限,可在不考虑整体系统复杂性的情况下测量 CPU 的整数或浮点计算能力。有时,作为此类基准测试的测试工具执行的软件内核是单一功能,可以通过使用内在指令或其他专门功能轻松优化,这会使收益难以在真正的客户应用程序中转化。因此,传统的基准值为嵌入式处理工程师在选择设备时提供了第一次通过的指标,并与潜在供应商合作。

然而,当今先进的 SoC 需要更全面的基准测试来揭示真正的性能和功能以及任何隐藏的瓶颈。由于单个芯片上集成了如此多的功能,因此对现实生活中的用例进行建模和测量变得越来越困难。因此,业界已经朝着针对特定应用领域(例如 Java 加速、Android 性能或 Web 浏览性能)的基准迈进。这种方法与综合基准测试不同,适用于具有明确定义的应用程序段的处理器,并为用户提供了对预期性能的相当准确的评估。

多核复杂性

对于部署在医疗成像、工业自动化、关键任务系统、通信基础设施和高性能计算等各种应用中的新一代嵌入式多核处理器而言,问题并不那么简单。架构复杂性与复杂的软件实现相结合,使问题更加复杂。SoC 架构内所有处理元件和系统总线的内部连接会影响设备的计算性能,并使其更难以测量和评估。

通过多核实现,多个线程可以在不同的内核上并行执行,而不仅仅是在单个内核上执行多任务。并行路径数量和调度可能性的增加使得建模应用程序行为和测量性能变得更加困难。

此外,多核系统引入了另一个维度:可扩展性,或者说随着使用越来越多的内核,架构的可扩展性如何。可扩展性不仅在为当前应用程序选择合适的架构方面很重要,而且在规划未来增长或产品组合扩展方面也很重要。众所周知的行业事实是,应用程序加速不会与内核数量成比例地线性增加,因为性能在某些时候会下降,并且在某些情况下实际上会随着内核数量的增加而降低。这主要是由于内核数量增加所遇到的访问瓶颈,以及额外的同步需求。加速还取决于软件的分区方式以及它可以在多大程度上利用增加的并行性。

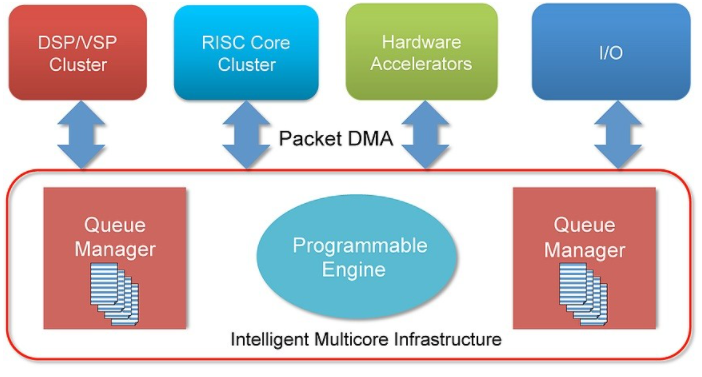

但是假设理想的软件实现,关于多核设备架构仍有很多话要说(见图 1)。高性能设备结合了多项创新技术,可有效地在系统中移动数据,从而使内核保持忙碌,而不会在访问停顿上浪费时间。高带宽芯片级互连和专用加速器创建了处理引擎孤岛,这些引擎以最少的核心干预工作,并且不会造成内存瓶颈。类似地,具有内置直接内存访问 (DMA) 的链式硬件队列充当迷你装配线,减轻中断的核心并安排这些处理任务。

图 1: Texas Instruments 的 KeyStone 多核 SoC 架构使用数据包 DMA 通信路径在所有 SoC 处理元件和 I/O 上并行调度任务,从而提供可扩展性。

构建块以获得更好的基准

随着芯片供应商采用截然不同的方法来提高多核效率,因此更需要设计可用于测量和比较可扩展性和性能的多核基准。这些基准测试应该易于移植,以便它们可以在裸机或常用操作系统上运行。由于增加了复杂性和复杂性,因此遵循模块化方法非常重要,这样可以使用基本构建块创建复杂的工作负载。在最低级别,基准测试应该包含可以参数化以改变计算与内存访问比率的处理内核。来自不同应用领域的代表性算法可用于创建其中一些内核。

内核也应该是可配置的,这样它们就可以在不同级别的资源争用下并行运行在不同的内核上。然后可以将这些内核的组合编织成复杂的工作负载拓扑,模拟各种特定于应用程序的场景。随着行业和多核应用程序的发展,可以设计更多工作负载并将其添加到现有基准测试的全部内容中。这些基准的输出应该是一个易于比较的分数,它反映了在特定数量的核心上完成给定工作负载所花费的时间。

毫无疑问,多核处理器支持新功能,并极大地改善了现有嵌入式产品的性能、功耗和成本。正如本期《嵌入式计算设计》中的文章所反映的,这个市场保持着兴奋和前景。令人着迷的是,虽然业界利用了部分多核基准测试机制,但没有主流的、市场接受的多核基准测试策略到位,尤其是在这样一个注重成本的经济时代。在做出最终选择之前,工程师和管理人员经常面临在多台设备上实施自己耗时的基准测试工作的艰巨任务。

很难不问为什么在多核市场上有如此聪明和创新的工程师会出现这种情况。也许这个以多核为特色的特别版将呼吁采取行动,以建立一个可行的、市场接受的多核基准测试策略,这不仅有利于使用此类设备的嵌入式工程师,也有利于多核 SoC 制造商。

作者:Debbie Greenstreet,Atul Verma

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19169浏览量

229155 -

soc

+关注

关注

38文章

4122浏览量

217950 -

操作系统

+关注

关注

37文章

6742浏览量

123192

发布评论请先 登录

相关推荐

CPU单核性能与多核性能的区别

多核CPU的优势是什么

电压测量仪表的主要性能有哪些?

针对特定内核使用PFlash,是否会影响多核应用程序的性能?

一文解析嵌入式多核异构方案,东胜物联RK3588多核异构核心板系列一览

TC3x多核使用与TC2x多核使用相比是否有任何限制?

risc-v多核芯片在AI方面的应用

多核架构高性能电机控制芯片

兆芯开先KX-7000处理器现身Geekbench,多核性能接近8代i5

多核异构通信框架(RPMsg-Lite)

YY3568多核异构(Linux+RT-Thread)--启动流程

对测量多核性能的追求

对测量多核性能的追求

评论