另一组片上系统验证方法依赖于使用经过验证的硅片、新的和未经测试(可能尚不可用)硅片的虚拟原型以及 FPGA 原型在硬件上执行实际软件。正如我们从这个角度看到的那样,有时会使用所有三种方法。

据最佳估计,90 nm 芯片设计背后的软件开发工作已经超过了硬件开发工作。对 2011 年的预测是,不到 40% 的整体芯片开发成本将用于硬件。软件现在主导着项目周期,并决定了芯片何时可以投入批量生产。结果,软件验证的重要性增加了,软件在硬件验证过程中扮演了不可或缺的角色。

将硬件和软件结合在一起

今天,工程师使用三种基本技术在硬件表示上执行软件。在衍生设计中,部分软件可以使用上一代芯片进行开发。这种方法通常最适用于分层软件架构中较高的软件部分,特别是对于独立于硬件的应用程序。

虚拟原型提供了设计周期中最早的解决方案,因为它们可以在架构确定后立即实施。这些原型是片上系统 (SoC)、电路板、I/O 和用户界面的预寄存器传输级别 (RTL)、寄存器精确和功能齐全的软件模型。它们执行未经修改的生产代码,并使用 USB 等外部接口作为虚拟 I/O 近乎实时地运行。

因为虚拟原型本质上是软件,所以它们提供了高度的系统可见性和控制,包括多核调试。它们还可以作为半导体和系统制造商之间协作的工具。自 Open SystemC Initiative Transaction Level Model (TLM) 2.0 API 标准化以来,SystemC 已成为使用可互操作的事务级模型开发快速虚拟原型的合适基础设施。

在 RTL 完成并使用功能验证技术达到稳定状态后,可以使用 FPGA 原型。原型是 SoC、电路板和 I/O 实现未修改的 ASIC RTL 代码的硅前、功能齐全的硬件表示。经过优化实施,它们可以在连接外部接口和激励的情况下几乎实时运行,并结合 RTL 仿真提供比实际芯片更高的系统可见性和控制。与传统的硬件/软件覆盖相比,FPGA 原型提供了更高的速度水平,后者将 RTL 仿真与周期精确的处理器模型相结合。

根据所需的准确性、速度和所需的可用时间,不同的技术为软件开发和软件驱动的硬件验证提供最合适的解决方案。混合产品通常允许设计人员利用多种产品的优势。例如,可以通过处理器和外围设备的快速事务级模型来增强 RTL 仿真,以提高仿真速度和验证覆盖率。或者,在混合使用模式下处理设计问题的虚拟原型和 FPGA 原型结合了基于软件和硬件的执行,提供了比单独产品更好的解决方案。

从实际项目中学习

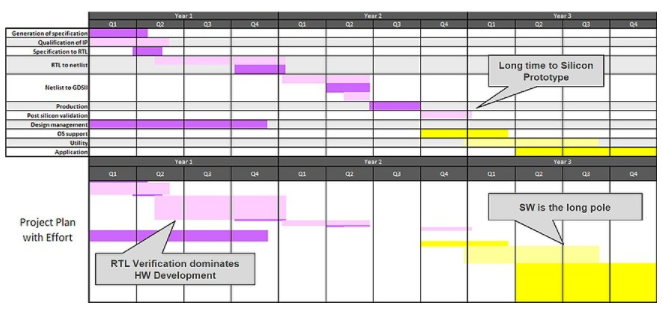

为了更好地理解这个问题,Synopsys 和 International Business Strategies 分析了包括复杂硬件和软件在内的 12 个项目的项目工作量和经过的时间。图 1 显示了分析的 12 个项目的示例。上半部分显示了不同开发阶段的时间线;底部显示了每个阶段的总体项目工作量的百分比。

图 1:在对 12 个项目的分析中,RTL 验证占用了 21% 的硬件/软件开发工作量。

RTL 验证平均占整体硬件/软件工作量的 21%,或仅硬件工作量的 38%。此外,RTL 验证消耗了从需求到 GDSII 所用时间的大约 55%。验证在流片的整个流程中以不同的变体继续进行,而且在 IP 认证上花费的大部分精力也可以被认为是另一种形式的验证。因此,验证很容易达到硬件开发中经常提到的 70% 的数字。

从硬件从规范到流片的开发时间来看,移植操作系统平均需要大约三分之一的时间,开发实用软件大约需要一半时间,三分之二的时间用于移植操作系统。开发应用软件。在工程样品可用时开始软件开发的全系列开发过程将使项目进度再增加半年到四分之三的时间。除非项目是并行开发的,否则软件开发会延迟大量交付硬件的能力。

虽然在项目开始后从需求到流片有 17% 的时间可以使用稳定的规范(虚拟原型的先决条件),但从需求到流片需要将近 70% 的时间才能达到稳定的 RTL(先决条件)用于硬件原型。虚拟和硬件原型在非常不同的时间可用,因此适用于非常不同的开发阶段。

提高验证效率

如果在 SoC 设计周期的早期提供虚拟原型用于软件开发,它可以不断发展以满足不同的需求。软件驱动验证的三种主要使用模型在 RTL 中利用虚拟原型与信号级仿真的集成:

1. 当一个 RTL 块可用时,它可以在虚拟原型中替换它的 TLM。然后可以在此版本的原型上验证软件,作为验证硬件和软件的一种方式。知道使用了真实的系统场景会增加验证的信心。此外,鉴于尽可能多的系统在事务级别进行模拟,验证的模拟速度更快。

2. 虚拟原型还可以作为运行实际系统软件的测试台组件,为 RTL 验证测试台开发和硅后验证测试提供先机。虚拟原型可用于生成系统激励来测试 RTL,然后验证虚拟原型和 RTL 功能是否相同。用户可以在TLM嵌入式定向软件测试上进行高效开发,也可以用于系统集成测试。结果,验证测试用例开发的生产力提高了。

3. 由于虚拟原型的某些部分被验证为等同于它们相应的 RTL,虚拟原型可以成为参考可执行规范。因此,用户获得了针对事务级别和 RTL 的单一黄金测试平台。

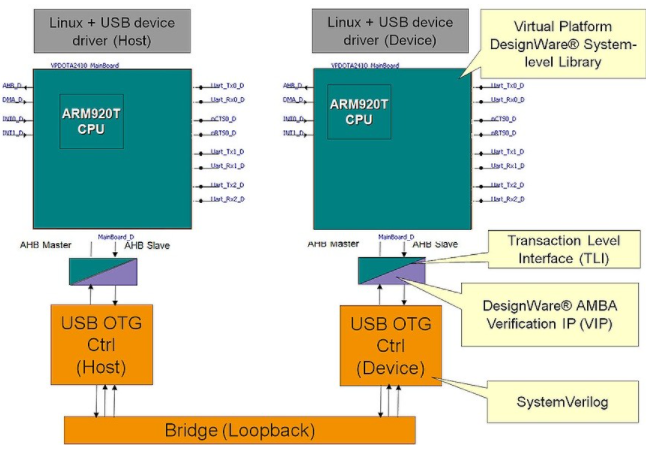

图 2 显示了 Synopsys Innovator 虚拟原型开发环境中的 USB On-The-Go 示例和分别使用事务级处理器模型和嵌入式软件的 USB 验证环境。

图 2:在 USB 验证环境中,事务级处理器模型通过 USB 连接到 RTL。

即使在项目开始时没有虚拟原型,硬件组件的虚拟化也可以帮助从 RTL 验证环境开始逐步提高验证效率。

在事务级别用虚拟处理器模型替换系统中片上处理器的 RTL 表示可以显着提高仿真速度,从而缩短验证周转时间。在几个客户示例中,更换单个处理器模型将仿真速度提高了 32 倍。

为了在功能 RTL 验证中加入软件驱动程序以执行实际产品测试用例,只需对适当的子系统进行建模并将其连接到 RTL 仿真。这可以像从库中添加事务级处理器模型一样简单,通过简单的总线模型将其连接到正在验证的外设的 TLM,然后将其连接到 RTL,如图 2 所示。

混合原型

为了通过提高仿真速度和系统中嵌入式软件的执行来进一步提高验证效率,可以使用硬件原型。鉴于虚拟原型和硬件原型在项目的根本不同阶段都可用,混合原型提供了一个可行的解决方案,让开发人员可以利用这两个世界的优势。

虽然虚拟原型在设计流程的早期就可用——通常仅在规范稳定后几周——它们通常并不代表 FPGA 原型可以展示的完整实现细节。相比之下,FPGA 原型在相当高的速度下运行完全准确,但在设计流程的后期可用,尽管在硅片从生产中返回之前还很长时间。

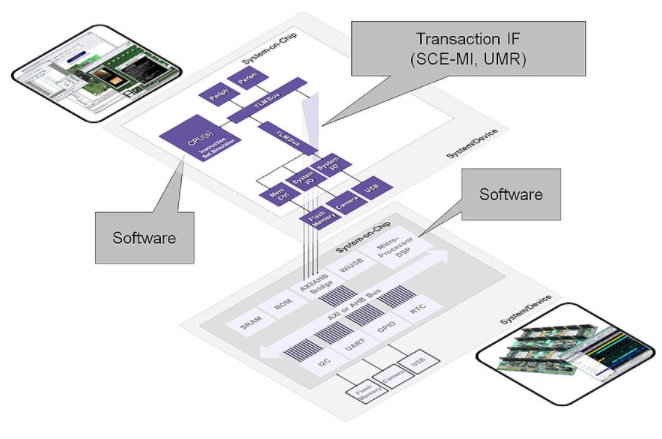

图 3 显示了混合 TLM 和硬件原型的原理图。几种混合使用模型结合了虚拟原型和 FPGA 原型的优点,包括重用实际 RTL 而不是重新建模和加速硬件和软件的整体执行。

图 3:虚拟原型和 FPGA 原型的混合使用模型结合了虚拟原型和 FPGA 原型的优点。

未来更智能的验证

由于验证对项目工作和时间表以及软件对项目成功的影响越来越大,考虑到嵌入式软件的智能验证变得越来越重要。

使用虚拟原型,无论是自下而上的 RTL 验证,还是自上而下的虚拟原型验证,都可以逐步提高验证效率。通过使用处理器和外围设备的虚拟化事务级模型增强传统 RTL 仿真,可以提高验证效率。这提高了仿真速度,并允许直接执行 TLM 参考模型作为测试台的一部分。在自上而下的流程中,可以通过重用现有的虚拟原型及其模型来提高验证效率,这可以通过简单地将正在验证的 RTL 替换为 TLM 直到 RTL 可用,从而为验证场景开发提供先机。虚拟原型随后成为 RTL 验证的参考。

虚拟原型和 FPGA 原型的混合以及 RTL 仿真和事务级模型的混合允许开发人员利用各个解决方案的综合优势。对验证效率的直接影响很大程度上源于更快的模拟执行,这反过来又可以加快验证周转速度。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19265浏览量

229684 -

FPGA

+关注

关注

1629文章

21729浏览量

603050 -

嵌入式

+关注

关注

5082文章

19111浏览量

304872

发布评论请先 登录

相关推荐

嵌入式软件驱动的硬件验证

嵌入式软件驱动的硬件验证

评论