随着最终产品功能的提高,对多核处理器提供的更高处理能力、更低成本和强大的功率性能的需求也在不断增长。

多核的故事实际上是关于系统集成的。内核数量的增加反映在外围设备、总线结构和多级存储器集成度的提高上。一般来说,多核处理器根据其架构分为两类:同构多核处理器和异构多核处理器。

同质多核处理器具有两个或多个相同的可编程内核,它们共享外围设备和内存。异构处理器具有多个独特的处理元素,每个元素都针对特定功能量身定制,并且每个内核可能只能选择性地访问外围设备和内存。这两种类型的多核处理器都产生了巨大的潜在性能提升。架构师可以根据最终应用的需求定制设计,并在性能、灵活性和功耗之间取得平衡。

使用同构或异构多核系统的开发人员通常会面临两类问题:同步和时序以及理解性能。

多核设备中的每个处理元件都执行设备功能的一部分。再加上改进的编码、打包和集成实践,同步运行、步进和暂停等传统调试技术在多核系统中非常有效。然而,当线程交互时,经常会出现与时间或同步相关的问题。

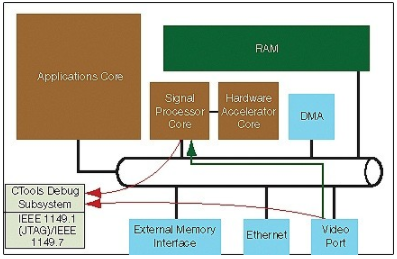

多核设备在处理元素之间总是存在依赖关系。很多时候,一个处理元素必须等待另一个处理元素的结果,如果它们不同步,两个线程之间的切换将不正确或效率低下。但是,可能会导致更微妙的问题。例如,在面向帧的处理方案中,一个新的帧可能会因为处理没有及时完成而丢失。虽然这可能不会导致应用程序崩溃,但它可能会降低应用程序处理结果的质量。这些问题很难隔离,因为它们是内核、总线结构和共享外设相互作用的结果。深入了解处理元件和外设之间关系的芯片级工具是优化和调试多核系统的关键(参见图 1)。

在嵌入式系统中,停滞的处理元件不仅会降低性能,还会影响功耗。为了最大限度地提高性能并降低功耗,开发人员必须尽量减少每个处理元件在数据准备就绪时的等待时间。当空闲时,可以关闭处理元件。

元素级别的性能对于理解如何在多核设备的内核之间划分线程至关重要。在关键接口处测量的性能进一步帮助开发人员识别系统瓶颈。这将有助于确定是否可以采取更多措施来优化内核、总线结构和外围设备的使用。有了这些知识,降低功耗的机会就变得显而易见了。

优化多核设备将是未来开发人员面临的最大挑战之一。展示多核设备巨大处理潜力的能力需要深入了解处理元件和外围设备之间的同步和时序,以及了解处理元件和关键接口的性能。新的多核处理器还需要强大的芯片级工具,让开发人员能够利用其潜在性能。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19225浏览量

229527 -

存储器

+关注

关注

38文章

7470浏览量

163699 -

总线

+关注

关注

10文章

2875浏览量

88027

发布评论请先 登录

相关推荐

MES解决方案的选择指南

解决方案丨EasyGo新能源系统实时仿真应用

发酵设备远程监控运维系统解决方案

什么是开关设备温升预测预警解决方案

工厂配电设备运行监控系统解决方案

提升25% | 自连光伏优化解决方案

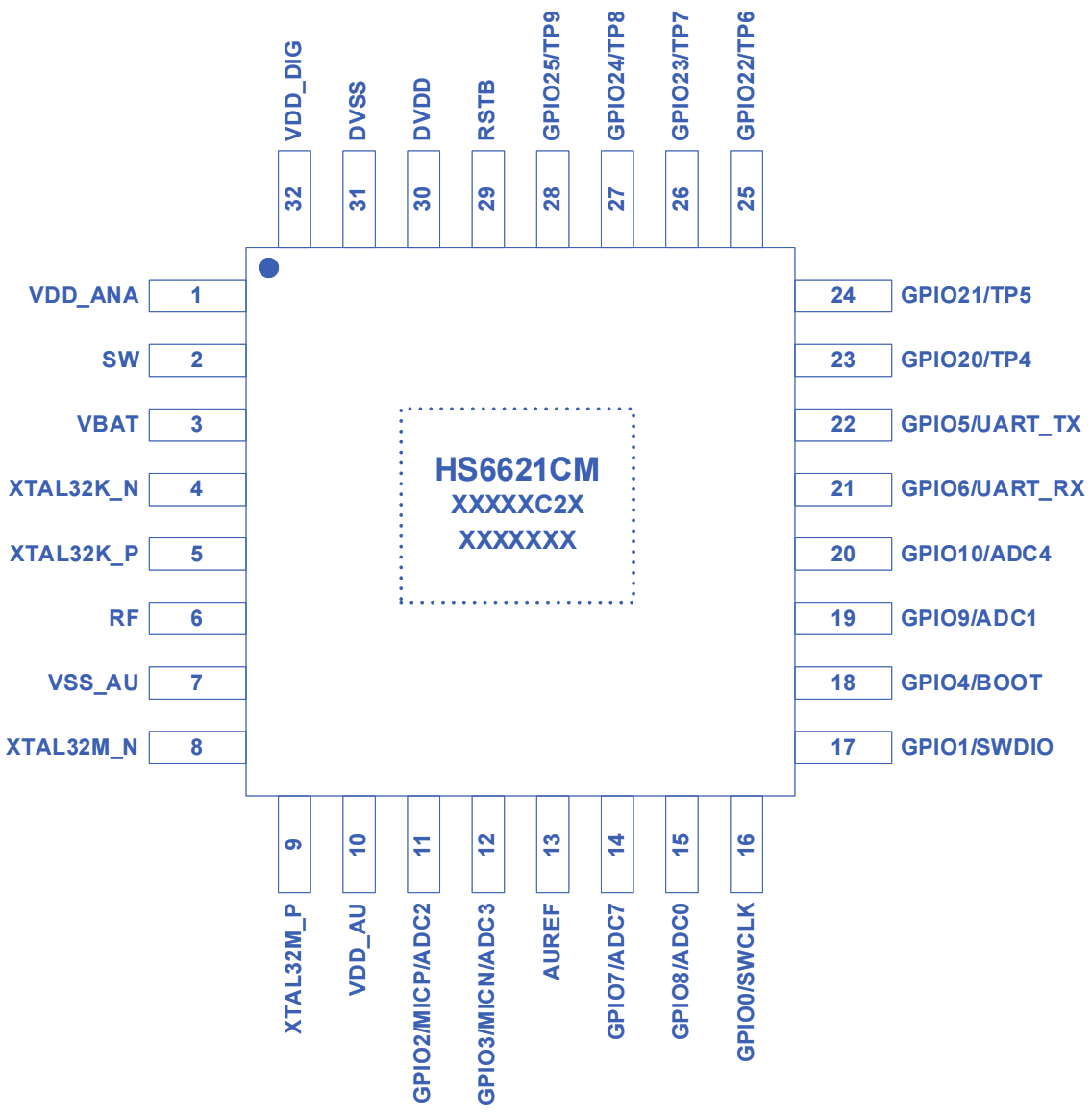

功耗优化的片上系统(SoC)解决方案,引领低功耗蓝牙与2.4GHz应用新潮流

优化多核设备的解决方案

优化多核设备的解决方案

评论