除非在系统设计中加入有效的安全性,否则嵌入式系统很容易成为黑客、安全漏洞和恶意攻击的牺牲品。如今,安全性是一个更大的问题,因为新的专有技术和有价值的 IP 被用作竞争壁垒。到目前为止,实现传统安全的技术一直很麻烦、过时且成本高昂。然而,当前趋势鼓励设计人员在 FPGA 中嵌入最高级别的安全性,以实现更高效、成本更低的设计。

符合美国国家标准与技术研究院 (NIST) 联邦信息处理标准 (FIPS) 197 的 FPGA 支持使用 256 位高级加密标准 (AES) 和非易失性密钥的配置比特流加密。AES 是当今可用的最先进的加密算法。用户定义的 AES 密钥可以编程到存储在 FPGA 设备中的 256 位非易失性密钥中。

选择正确的加密算法和选择适当的密钥存储是两个重要的设计考虑因素。AES 支持 128、192 和 256 位的密钥大小,并取代了具有 56 位密钥和 64 位数据块大小的数据加密标准 (DES)。AES 等较大的密钥大小等同于提高安全性,并且比三重 DES (3DES) 更快地加密数据。实际上,3DES 使用三个密钥对文档进行了三次加密。

加密将电子数据转换为通常称为密文的难以理解的形式;解密密文将数据转换回其原始形式或明文。AES 算法是一种对称分组密码,可对 128 位块中的电子数据进行加密/加密和解密/解密。在该算法中,对称密钥用于加密和解密,并且块密码以块为单位处理数据。对称密钥分组密码加密算法在许多行业中都有使用,因为它们提供了高安全保护和效率、易于实施和快速的数据处理速度。

密钥存储的选择是第二个最重要的设计考虑因素。密钥存储在易失性或非易失性存储器中,具体取决于芯片供应商。一旦关闭易失性存储的电源,密钥就会丢失,除非将外部电池连接到芯片作为备用电源。另一方面,非易失性密钥存储为设计人员提供了更大的灵活性。

例如,FPGA 中的嵌入式非易失性密钥可以在板上或板外进行编程。安全密钥存储在 FPGA 内的多熔丝中。多晶保险丝是非易失性和一次性可编程的,这意味着这种存储方法更可靠,因为不需要外部备用电池。

可靠性差是电池对易失性存储造成的最大问题。电池寿命受温度和湿度水平的影响。电池没电了,钥匙就丢了。因此,无法再配置设备,必须将设备退回供应商进行维修和重新加载密钥。此外,电池备份成本更高,因为它更难制造,需要更多组件、电路板空间和工程工作。

电池通常无法承受高温回流工艺,必须在之后焊接到板上,这会产生额外的制造步骤。易失性密钥存储还需要在将密钥焊接到板上后将其编程到设备中。

因为非易失性存储是一次性可编程的,所以密钥是防篡改的。这在易失性存储中是不可能的,因为可以移除电池并且可以使用常规加密配置文件对 FPGA 进行配置。

将安全性设计到系统中

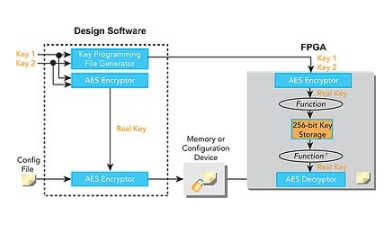

图 1 显示了如何使用 Quartus II 设计软件在 Altera 的 Stratix III FPGA 中实现安全性。第一步是将安全密钥编程到 FPGA 中。设计软件需要 256 位用户自定义密钥(密钥 1 和密钥 2)来生成密钥编程文件。然后通过 JTAG 接口将包含 Key 1 和 Key 2 信息的文件加载到 FPGA 中。

图1

接下来,内置在 FPGA 中的 AES 加密引擎生成用于在第三步稍后解密配置数据的真实密钥。通过加密密钥 1 和密钥 2 创建的真实密钥随后由专有功能处理,然后存储在 256 位非易失性密钥存储中。

第二步,配置文件被加密并存储在外部存储器中。设计软件需要两个 256 位密钥(密钥 1 和密钥 2)来加密配置文件。Quartus II AES 加密引擎通过使用密钥 2 加密密钥 1 来生成真实密钥。真实密钥用于加密配置文件,然后将其加载到外部存储器中,例如配置或闪存设备。

第三,配置FPGA。在系统上电时,外部存储设备将加密的配置文件发送到 FPGA。FPGA 中的 256 位非易失性密钥经过专有函数的逆处理,生成真正的密钥。AES 解密引擎然后使用真实密钥解密配置文件并配置自己。

安全入侵

作为设计过程的一部分,系统设计人员必须识别和理解不同类型的安全漏洞,包括复制、逆向工程和篡改,如表 1 所示。

复制涉及在不了解其工作原理的情况下制作相同的设计副本。可以通过从存储器件中读取设计或在上电时将配置文件从存储器件发送到 FPGA 时捕获配置文件来完成复制。然后,窃取的设计可用于配置其他 FPGA。这种方法构成了知识产权盗窃的主要形式,并可能导致重大的收入损失。

逆向工程需要分析配置文件以在寄存器传输级别或以示意图形式重新创建原始设计。然后可以修改重新创建的设计以获得竞争优势。这是一种比复制更复杂的 IP 盗窃形式,通常需要大量的技术专长。这也是时间和资源密集型的,有时比从头开始创建设计需要更多的工作。

篡改涉及修改存储在设备中的设计或用不同的设计替换它。被篡改的设备可能包含能够导致系统故障或窃取敏感数据的有害设计代码。

大多数非易失性 FPGA 具有允许回读配置数据以进行调试的功能,如图 2 所示。设计人员通常可以为器件设置安全位。如果未设置安全位,则允许回读,并且可以直接获取配置数据。但是当设置了安全位时,回读被禁用。在设置安全位时进行回读攻击的一种方法是检测安全位在 FPGA 中的位置并停用它们以启用回读。

图 2

设置入侵屏障

一些 FPGA 使攻击者几乎不可能从高度安全的嵌入式设计中窃取 IP。特别是,检测和禁用安全位可能很困难,因此为设计人员提供了更大的防复制能力。以下讨论解释了设计人员如何设置这些安全防御。

存储安全密钥的多晶硅保险丝隐藏在数百个其他多晶硅保险丝中的金属层之下。通过简单的目视检查几乎不可能确定特定保险丝的功能。用于其他功能的多晶硅熔丝的编程状态可能因器件而异。

这种随机性使得识别哪些保险丝存储安全密钥变得更加困难。此外,即使识别出存储安全密钥的多熔丝,也不会透露用于解密的真实密钥,因为它是在存储之前由专有功能处理的。在不知道真正密钥的情况下,无法解密设计。

因此,这些 FPGA 可以抵御回读攻击,因为它们不支持配置文件回读。这可以防止在配置文件在 FPGA 中解密后尝试读回配置文件。此外,无法通过将安全密钥编程到另一个 FPGA 并使用加密配置文件对其进行配置来复制这些设计。将安全密钥编程到 FPGA 中需要两个 256 位密钥。因为 AES 用于生成真实密钥,所以几乎不可能从安全密钥生成密钥 1 和密钥 2。

即使没有加密,从配置文件对设计进行逆向工程也是困难且耗时的。FPGA配置文件包含数百万比特,配置文件格式是专有和保密的。要对设计进行逆向工程,需要对用于揭示从配置文件到设备资源的映射的 FPGA 或设计软件进行逆向工程。

对这些 FPGA 进行逆向工程比对 ASIC 进行逆向工程更困难。标准工具无法对这些 FPGA 进行逆向工程,这些 FPGA 是在 65 纳米先进工艺技术节点上制造的。事实上,仅对一个 FPGA 逻辑块进行逆向工程可能会花费大量时间和资源。配置比特流加密使逆向工程更具挑战性。找到解密配置文件的安全密钥就像复制它一样复杂;因此,从头开始创建具有竞争力的设计可能比尝试对诸如此类的安全 FPGA 设计进行逆向工程更容易、更快捷。

非易失性密钥是一次性可编程的,以防止篡改。FPGA 使用密钥编程后,只能配置使用相同密钥加密的配置文件。尝试使用未加密的配置文件或使用错误密钥加密的配置文件来配置 FPGA 会导致配置失败。无论是在设计、外部存储器和 FPGA 之间的传输过程中,还是在远程通信系统升级过程中,配置失败都表明可能存在篡改。

设计方案比较

除了上述 FPGA 安全系统外,设计人员可用的其他设计选项包括基于 SRAM 的 FPGA,仅限于 3DES 加密、基于闪存的 FPGA 和基于反熔丝的 FPGA。表 2 描述了每种情况下的攻击成本。

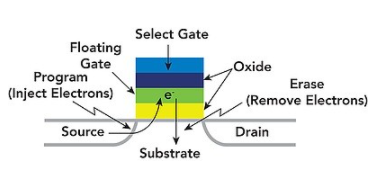

非易失性 FPGA 在断电时保留其配置。揭示器件配置的一种方法是探测或检测每个非易失性单元的可编程状态。对基于闪存的 FPGA 的两种侧通道攻击是电子发射检测和晶体管阈值电压变化。

通过电子发射检测的攻击首先涉及移除设备的封装以暴露裸片。接下来,将该设备放置在真空室中并通电。然后攻击者使用透射电子显微镜来检测和显示发射。至于第二种技术,由于浮栅中的电子积累,晶体管的阈值电压会随着时间而变化。这导致晶体管的阈值电压逐渐升高。

除了这两种侧信道攻击之外,另一个流行的版本,功率攻击,涉及测量 FPGA 的功耗以确定设备正在执行的功能。至于对基于闪存的 FPGA 的回读攻击,所需的工作量因供应商而异,并且取决于设备中安全位的保护程度。此外,探测每个基于闪存的 FPGA 的浮动门需要大量的时间和精力,因为在编程后门不会发生物理变化。被氧化物隔离的状态由选择栅极和衬底之间的浮栅上电子的存在或数量决定(参见图 3)。

图 3

此外,对闪存 FPGA 配置文件进行逆向工程并不容易,因为必须首先获取配置文件。这是一项难以完成的任务,因为攻击者必须在逆向工程之前执行复制。对设计人员来说,同样重要的是要知道篡改基于闪存的 FPGA 很容易,因为该设备是可重新编程的。因此,如果需要考虑篡改,则必须使用防篡改机制。

编程状态探测也用于攻击基于反熔丝的 FPGA。技术包括聚焦离子束 (FIB) 技术和扫描电子显微镜 (SEM)。FIB 用于显微镜成像和设备横截面,而 SEM 涉及使用光栅型扫描的显微镜成像,以检测从表面发射的二次电子。分析基于反熔丝的 FPGA 的编程状态非常耗时,因为有数百万个反熔丝链接和一小部分已编程。

改进的风险管理策略

设计人员必须估算总安全成本并进行权衡,以确定适合设计中设备的安全级别。为了实现高水平的安全性,设计人员必须分析潜在威胁,考虑给定一组特定漏洞的攻击概率,并设置有效和适当的防御措施。FPGA 提供了多种可靠的安全方案,使设计人员能够实施成本更低的风险管理策略。

审核编辑:郭婷

-

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

寄存器

+关注

关注

31文章

5336浏览量

120230 -

sram

+关注

关注

6文章

767浏览量

114675

发布评论请先 登录

相关推荐

aes技术在物联网中的应用前景

aes算法在移动应用中的应用场景

aes加密的常见错误及解决方案

aes在云存储中的应用实例

蓝牙AES+RNG如何保障物联网信息安全

高压真空开关具有哪些保护功能

开源物联网技术--AES加密功能技术分享

用于具有AES硬件加密功能的TM4C129器件的共享密钥引导加载程序

是否可以调用内置函数来使用AES和12位密钥加密缓冲区?

请问如何在非操作系统sdk中使用WPA2-PSK(AES)配置SoftAP?

基于FPGA的AES256光纤加密设计

基于 FPGA 的光纤混沌加密系统

AES加密协议是什么?AES加密协议的应用

基于FPGA的可编程AES加解密IP

具有内置AES的FPGA保护系统设计

具有内置AES的FPGA保护系统设计

评论