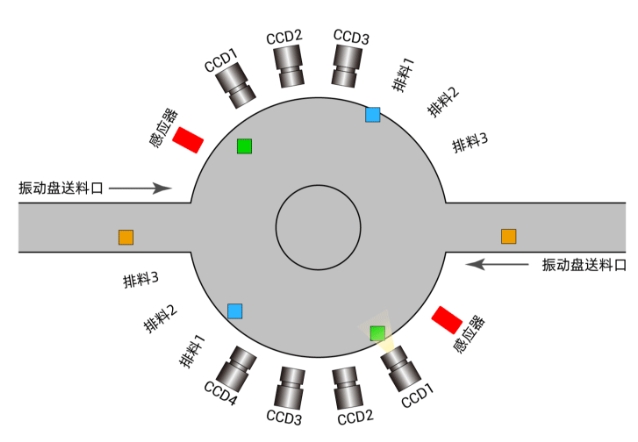

作为我们关于仪器发展的特色部分的一部分,这里有一个关于直接集成到电路中的芯片仪器的观点。使用 PCIe 开关芯片和支持软件中的集成仪器,确定 PCI Express(PCIe 链路是否正确启动并快速诊断系统问题)现在变得容易得多。

任何从事电子系统业务相当长的时间的人都已经看到了系统设计、互连和调试方式的若干范式转变。一个显着的变化是并行总线消失,取而代之的是串行化、虚拟化和交换连接。

几十年前,几乎电路中的每个节点都可以用示波器轻松探测。仅在五年前,人们还可以指望一种可用逻辑或协议分析仪监控的并行总线。今天,比单个片上系统 (SoC) 更大的系统由多个类似 SoC 的组件组成,这些组件通过高速串行总线互连,可能通过数据包交换机。没有隐藏在表面贴装技术组件下或埋在内部 PCB 层中的少数可见互连迹线无法触摸,因为害怕海森堡。

集成仪表的案例

如果要在几分钟到几小时(而不是几天到几周)内完全调试复杂的系统问题或解决更简单问题的根本原因,系统互连交换机现在还必须充当逻辑和协议分析器。交换机还应该能够评估物理层的信号完整性,以全线速运行外部链路,并注入各种错误以评估系统检测和从此类错误中恢复的能力。考虑到当今系统封装的高度集成和限制,这些措施是为这些目的连接外部测试设备所面临的几乎无法克服的挑战所必需的。

PCIe Gen 2 的 5 Gbps 速度给组件开发人员及其客户带来了额外的挑战,而正在开发的 Gen 3 规范将加剧这些挑战。较高的频率总体上降低了时序和信号裕度,使物理层更容易受到现实世界传输线环境的非理想性的影响,甚至对微创探测也不利。

为了克服物理层损伤,SERDES 设计人员利用了接收均衡的概念。使用均衡,信号完整性眼图张开仅在均衡器的输出端才有意义地观察到,隐藏在组件内部。这只能在集成仪器的帮助下完成。

加速产品上线

经验丰富且成功的设计团队长期以来实施的功能使他们能够调试产品开发过程中出现的问题。借助当今可用的晶体管密度,设计人员可以将逻辑分析功能与关键任务功能集成在一起,而且通常不会影响成本。即使是查看数百万门 ASIC 中逻辑节点的一小部分的能力,对于快速找到组件或系统级错误的根本原因也具有不可估量的价值。

虽然这些高级功能曾经仅供工厂使用,但现在通过提供高级界面的软件向客户开放。该接口使客户无需了解电路实现的详细知识以了解结果,同时保护制造商的知识产权。同时,集成分析工具的范围正在从单个组件的焦点扩展到系统范围的问题。

虽然集成仪器在整个开发周期中都很有用,但在考虑初始电路板启动所涉及的问题时,它的价值最容易被理解。当一个系统或子系统由围绕一个中央 PCIe 分组交换机的多个 SoC 组成时,该交换机是第一次上电后关注的焦点。链接出来了吗?信号完整性是否符合预期和要求?枚举和后续配置成功了吗?数据包流模式是否标称?越早回答这些问题,团队就能越早将墨菲扔给他们的东西归零,并朝着成功的产品发布迈进。借助由供应商提供的支持软件支持的集成仪器,这些答案很容易获得。

使用内部逻辑分析仪

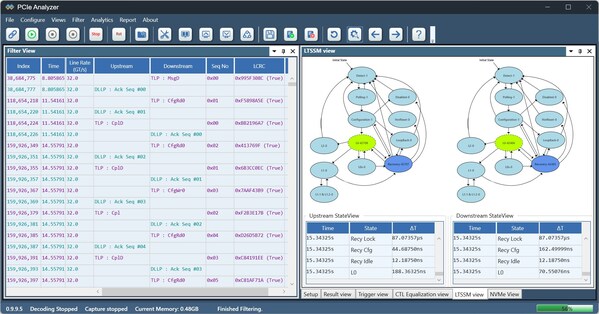

为新板供电时的首要任务是确定 PCIe 链路是否已启动。PCIe 开关通常为每个端口提供链路状态输出,可控制 LED 以进行视觉指示。如果链路没有出现,跟踪 PCIe 规范中定义的链路训练和状态状态机 (LTSSM) 的转换非常有帮助。

甚至带有简单集成逻辑分析仪的交换机也可以配置为在链路训练周期中捕获端口 LTSSM 到内部跟踪存储器的每次转换并为其加上时间戳。之后,可以通过 I2C 或 PCIe 读取轨迹,并借助随附的软件进行分析。这种跟踪通常可以快速区分互操作性问题、制造问题和信号完整性问题。

如果跟踪 LTSSM 无法确定答案,则可以首先将内部逻辑分析仪指向 SERDES、串行到并行转换器、弹性缓冲器、解扰器等的输出,以尝试查明故障。

虽然集成逻辑分析仪可以提供深入探究 ASIC 内部的能力,但只有那些靠近外部接口或按照行业标准要求构建的寄存器或状态机对最终用户才有意义。

优化链路性能

一旦每个链路建立起来,就有必要估计信号完整性的眼图张开度并对其进行优化。高级 SERDES 允许借助内置自测 (BIST) 功能测量眼图张开的宽度。这是通过有时使用专利技术来完成的,该技术将采样点从眼睛中心偏移,然后确定这是否会导致误码。链路处于环回模式,并使用内部误码率测试逻辑测试误码率。调试处理器可以逐步设置 SERDES 均衡器和驱动强度选项,报告效果最佳的选项,甚至将它们烧录到可选的串行电擦除可编程只读存储器 (EEPROM) 中,以便在下一个上电周期自动加载。

可以提供对该测量和参数优化过程提供一定程度自动化的软件(参见图 2)。

图 2

通过将调试处理器连接到交换机的 I2C 总线,工程师可以边带访问所有交换机的内部寄存器。开发人员可以在应用程序运行时手动查看和戳,以检查其进度或执行脚本,将实际交换机配置状态与预期状态进行比较。

调试处理器可以配置可用的性能监视器,然后在应用程序运行时实时显示收集的统计数据,以实时指示其运行状况。纯粹为了方便起见,可以通过调试端口提供对下游设备、控制和状态寄存器的类似访问。当以这种方式使用时,调试处理器的作用类似于服务器中使用的管理或服务处理器,实际上,它们的功能可以组合起来。

经过功能调试后,压力测试和错误注入是产品开发的两个必要环节。交换机的正常数据路径很容易修改为锻炼器。作为第一步,交换机留出一部分缓冲存储器,允许软件在其中构建数据包,然后在选定的链路上传输数据包。更高级的实现包括计数、循环和分支机制,以支持更复杂的数据包流并将伪随机元素添加到错误注入中。

将交换机的某些部分作为练习器操作时,所涉及的端口不再充当交换机。因此,此功能不像 PCIe 交换机中的其他开发加速功能那样不显眼。尽管如此,可以执行错误注入并在高达 x16 Gen 2 链路上生成全线速数据包流的组件的简单可用性对产品验证社区来说是一个巨大的福音。

实施嵌入式仪器

在 PLX Technology,将这些功能集成到 PCIe 芯片中是出于降低制造成本和促进内部调试和验证工作的自私愿望。很快就很明显,这些功能可能对客户更有价值,因为它可以加速他们的产品开发过程。由于技术正在向更高的互连速度发展,PLX 认为集成仪器正迅速变得必不可少,尤其是对于 PCIe 开关。

实施 SERDES 眼图测量功能需要与 SERDES 和 SERDES BIST 知识产权供应商密切合作,然后设计团队努力利用所提供的功能。

实现片上逻辑分析的设计方法需要寄存器传输级 (RTL) 工程师提供来自每个主要模块的关键状态的可选探针输出,其方式与插入验证断言所需的方式大致相同。这种内部标准化允许脚本开发部分自动化将馈入触发逻辑和跟踪存储器的探针总线添加到 RTL 层次结构中。标准化还减少了利用这些数据并将其中的至少一部分塑造成对最终用户有用的形式所需的软件工作量。

随着技术的发展,集成的仪器仪表和支持软件工具显示出巨大的潜力并变得更加用户友好。对于 PCIe 开关供应商和客户来说,这代表了一个新的和有希望的方向,一个可以消除系统开发过程中主要的痛苦和延迟来源。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19134浏览量

228916 -

嵌入式

+关注

关注

5063文章

18990浏览量

302471 -

寄存器

+关注

关注

31文章

5305浏览量

119904

发布评论请先 登录

相关推荐

[XILINX] 正点原子ZYNQ7035/7045/7100开发板发布、ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2!

Prodigy Technovations推出功能强大的PCIe Gen5协议分析仪

SILVER 跨接式连接器具有哪些产品特性?-赫联电子

具有集成开关的 TPS53316 高效5A降压稳压器数据表

同星智能PCIe接口卡系列产品TP1026P正式发布!

具有集成仪表的PCIe开关可加快产品开发

具有集成仪表的PCIe开关可加快产品开发

评论