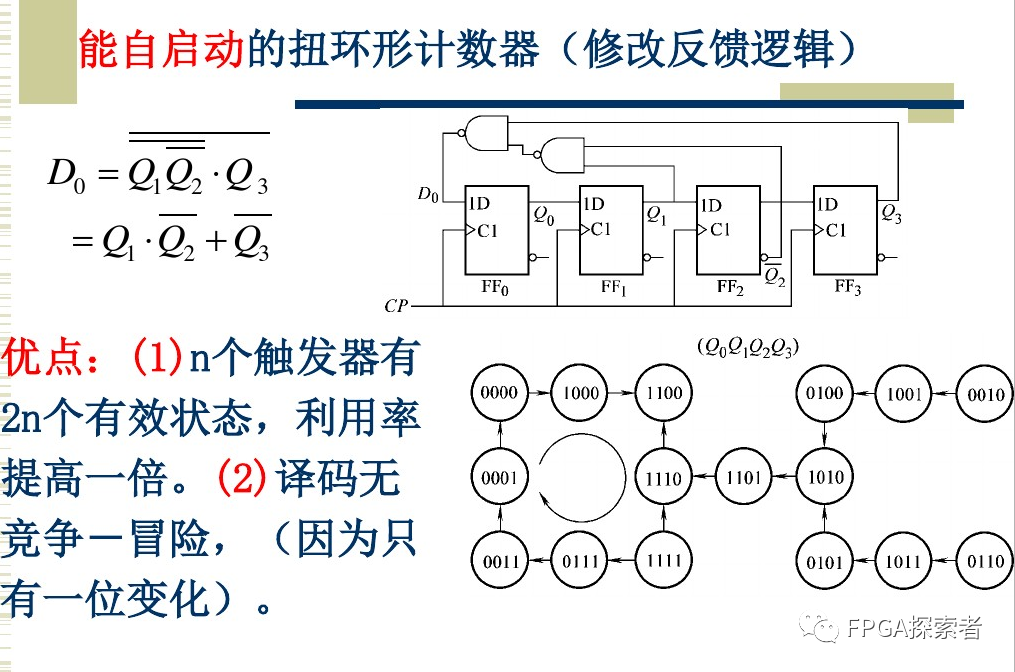

问题:实现 N 位 Johnson Counter。

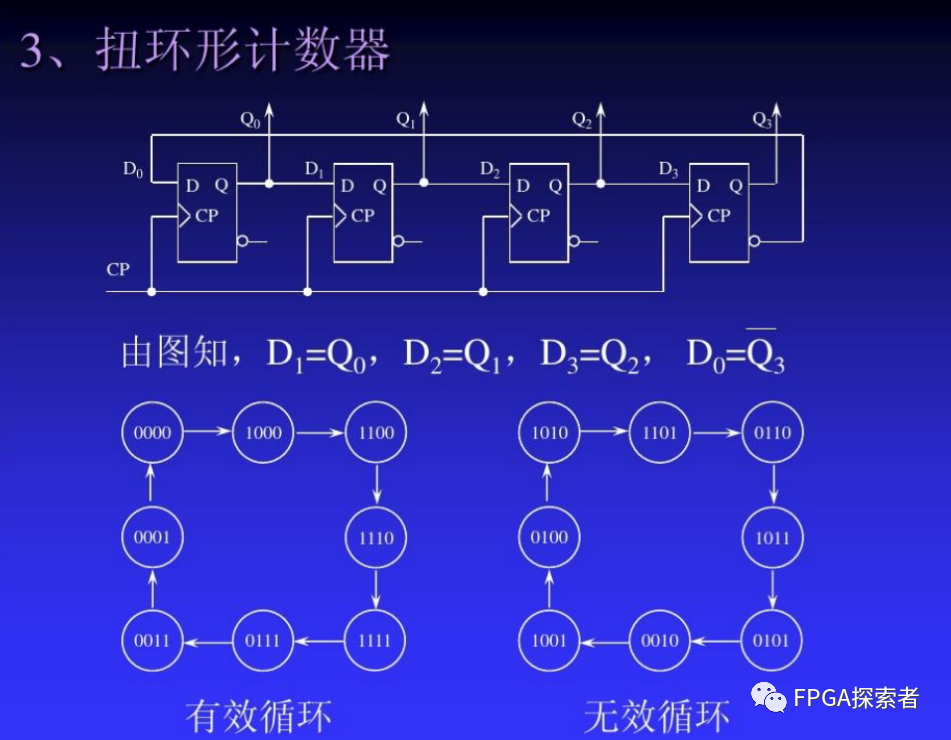

当 N = 4 时,输出应该是

0000 -> 1000 -> 1100 -> 1110 ->

1111-> 0111 ->0011-> 0001 ->

0000 ->...

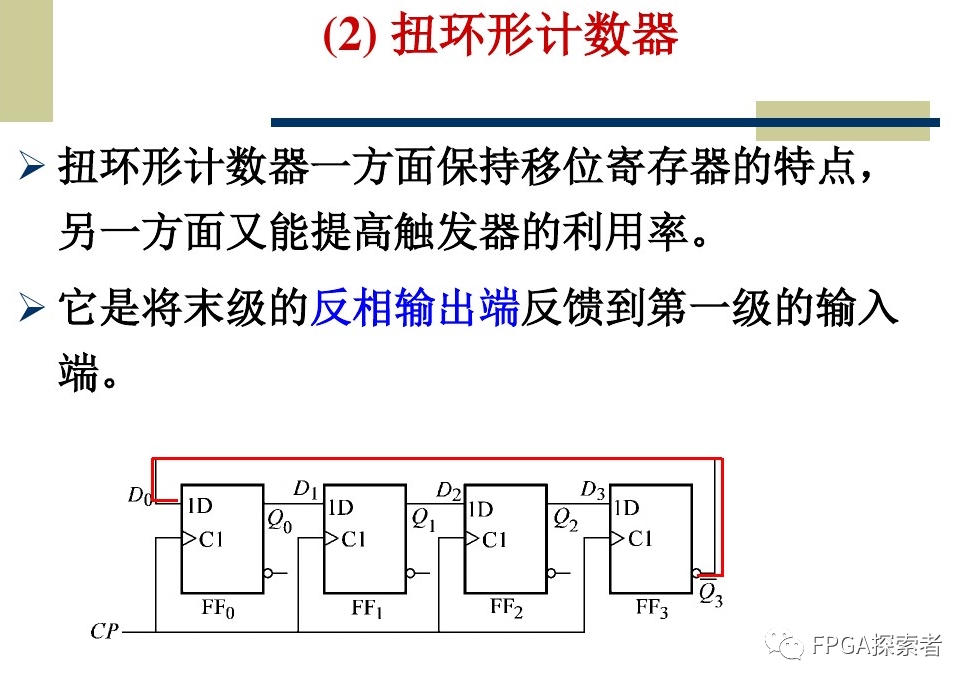

如下图所示,扭环形(约翰逊)计数器最后一个触发器的输出取反~Q3,然后输入回第一个触发器的输入 D(0)= ~Q(N-1),其余触发器的输入来自前级的输出 D(i+1) = Q(i)。

D(0)= ~Q(N-1)

D(i+1) = Q(i)

Johnson 约翰逊计数器Verilog 实现

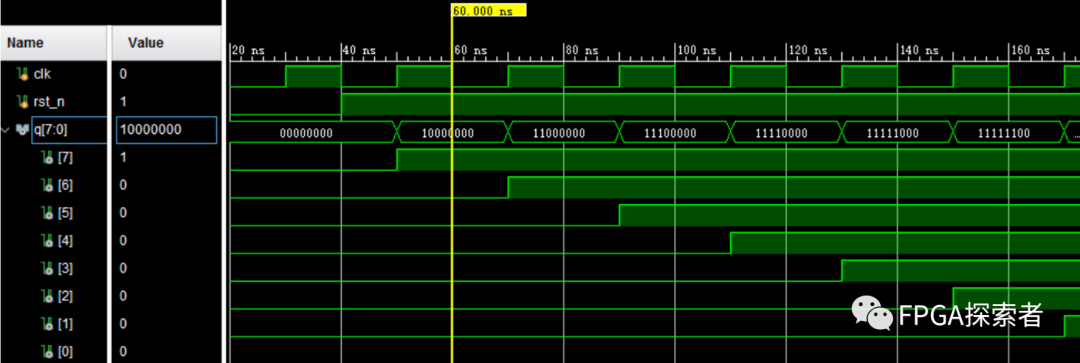

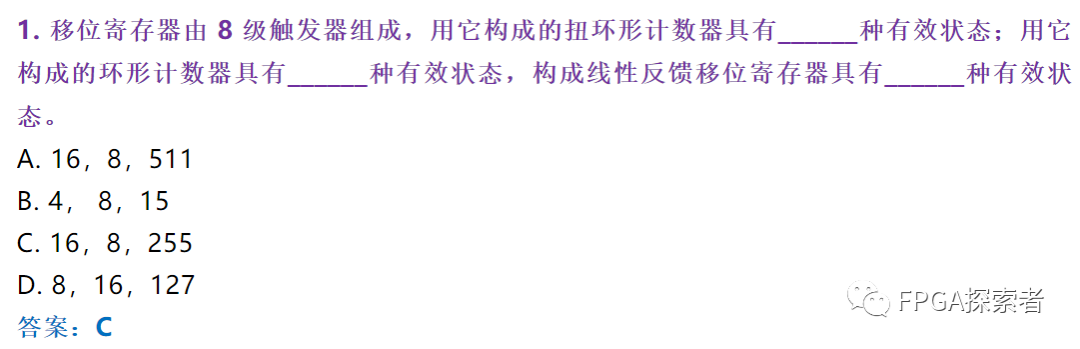

用Verilog HDL写一个8-bit的Johnson计数器,N = 8。

module johnson#(parameter N=8)(input clk,input rst_n,output reg [N-1:0] q);always @ (posedge clk,negedge rst_n)beginif(!rst_n)q<= {N{1'b0}};elseif(!q[0])q <= {1'b1,q[N-1:1]};elseq <= {1'b0,q[N-1:1]};endendmodule

仿真图:

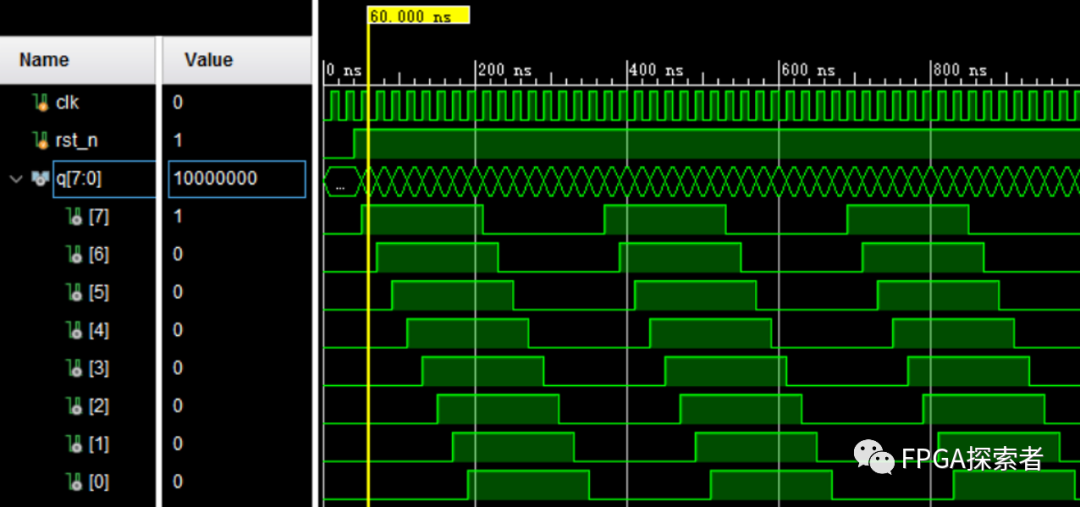

第二种:

module johnson#(parameter N=8)(input clk,input rst_n,output reg [N-1:0] q);always @ (posedge clk,negedge rst_n)beginif(!rst_n)q<= {N{1'b0}};elseq<= {~q[0], q[N-1:1]};endendmodule

Johnson 约翰逊计数器

(1)扭环形计数器,约翰逊计数器,每次状态变化时仅有一个触发器发生翻转,译码不存在竞争冒险,在n(n≥3)位计数器中,使用2n个状态,有2^n-2n个状态未使用;

(2)环形计数器,正常工作时所有触发器中只有一个是1(或0)状态,计n个数需要n个触发器,状态利用率低;

(3)n个寄存器的线性反馈移位寄存器LFSR可以产生的最长的随机序列是2^n−1长度(即m序列)。LFSR常被用来生成m序列,也可产生和校验CRC。

审核编辑 :李倩

-

FPGA

+关注

关注

1629文章

21729浏览量

602998 -

Verilog

+关注

关注

28文章

1351浏览量

110074 -

触发器

+关注

关注

14文章

2000浏览量

61132

原文标题:FPGA/数字IC笔试题——Verilog实现 N 位 Johnson Counter【约翰逊计数器】【扭环形计数器】

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

智能雷击计数器的综合行业解决方案

雷击计数器的概述与应用分析

Johnson约翰逊计数器Verilog实现

Johnson约翰逊计数器Verilog实现

评论