执行概要

就 FPGA 而言,可在设备的可编程逻辑中例化一个或多个软核处理器,从而使设计人员能够将可编程微控制器和/或微处理器核添加到自己的设计中。

现在,基于 FPGA 的软核处理器的性能在嵌入式市场中变得越来越重要。工业和军用等市场中那些运行复杂工作负载的嵌入式应用需要能够配备多种支持易用工具的高性能软核处理器来加速软件开发。

RISC-V 不但能够满足这些市场的性能需求,还能提供一条持续实现技术模块或知识产权模块(IP 模块) 升级、不断获得先进工具的途径。发展壮大中的 RISC-V 生态系统也带来了广泛的软件兼容性、更好的工具和编译器支持,以及标准的调试环境。

通过将英特尔 FPGA 中使用的软核处理器迁移到开放标准,以及与知名 RISC-V 解决方案提供商 Ashling 合作,英特尔可使用户获得由现代集成开发环境 (IDE)、编译器、调试器和操作系统组成的多元生态系统的支持。

英特尔 RISC-V 策略

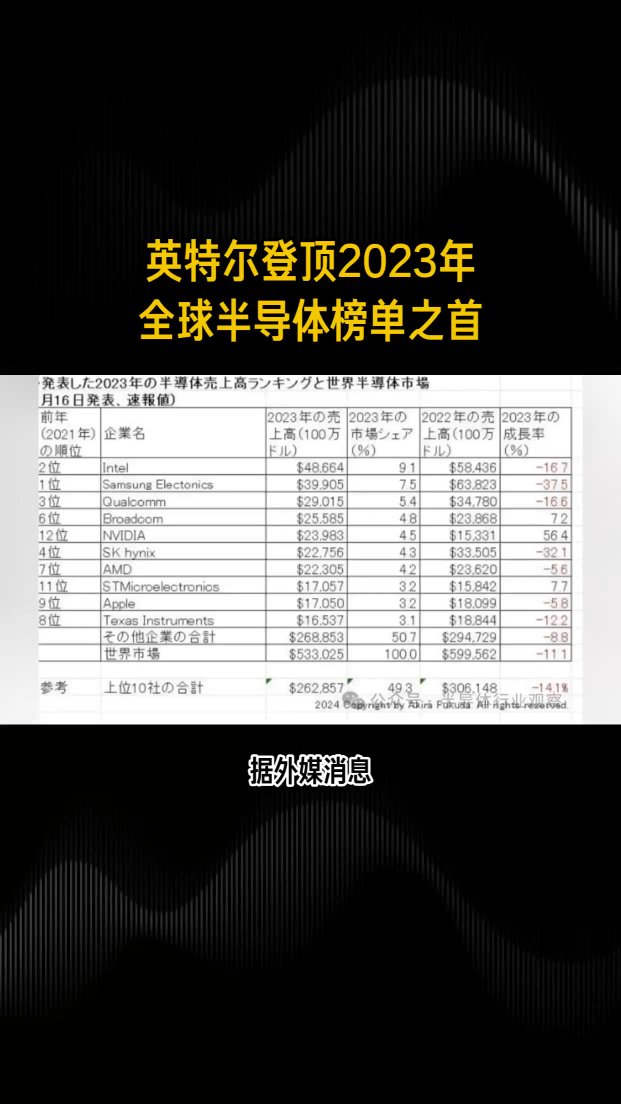

英特尔是微处理器行业的开拓者。早在 50 多年前的 1971 年就打造了首款商用微处理器英特尔 4004。1978 年,英特尔创造了 x86 架构,这是早期面向基于微处理器计算的指令集架构 (ISA) 之一。现在,x86 指令集架构已经发展成为世界上通用计算应用广泛使用的架构。自 x86 指令集架构问世以来,英特尔将 40 多年的时间都投入到开发成功的指令集架构、建立卓有成效的合作关系以及发展高生产力水平的生态系统上,这些业界都有目共睹。

除了微处理器产品外,英特尔的可编程解决方案事业部还开发了大容量高性能 FPGA。这些设备为用户提供了多种选择,包括可配置的嵌入式 SRAM、高速收发器、高速输入/输出 (I/O)、逻辑块和路由。内置的 IP 模块与出色的软件工具相结合,有效缩短了 FPGA 开发时间、降低了功耗和成本。

2022 年 2 月,英特尔成为全球开放硬件标准组织 RISC-V International 的活跃成员。开放的 RISC-V 生态系统提供了现代计算不可或缺的开放式、模块化构建基础。加入 RISC-V 后,英特尔展现出自身的领导力,开展了多项活动,为所有行业利益相关者扩大了 RISC-V 生态系统的潜力。

基于 RISC-V 策略,英特尔与 RISC-V 生态系统内各大合作伙伴通力合作,这些合作伙伴包括 Ashling、晶心科技、Esperanto Technologies、SiFive 和 Ventana Micro Systems。

英特尔计划投入多笔资金,加强 RISC-V 生态系统建设并帮助推动 RISC-V 进一步落地。在英特尔的组织下,这些投资将帮助那些具有开创性的 RISC-V 公司通过在以下活动及其他方面开展合作,更快实现创新:

技术协同优化

优先晶圆共乘服务

支持客户设计

建立开发板

不断发展软件基础设施

例如,英特尔计划提供一系列经过验证的基于 RISC-V 的内核,这些内核的性能已针对不同的细分市场进行了优化。英特尔将通过与各大提供商合作,优化面向英特尔制程工艺的 IP 模块,以确保 RISC-V 能够在从嵌入式内核到高性能内核的各种内核类型的英特尔 芯片上运行良好。RISC-V 产品将提供三种类型:

基于英特尔 技术制造的合作伙伴产品。

获得差异化 IP 模块许可的 RISC-V 内核。

采用英特尔先进封装技术和高速芯片到芯片接口的 RISC-V 小芯片构建模块。

英特尔对 RISC-V 的投资,再加上 RISC-V 社区的支持,将加速开放式 RISC-V 模块和其他交付产品的开发进程。此外,英特尔晶圆代工服务 (IFS) 部门还将赞助一个开源软件开发平台。该平台支持自由开展实验,生态系统、大学和联盟的合作伙伴均可从中受益。这项代工服务策略将提供广泛的面向英特尔制程工艺优化的技术。英特尔晶圆代工服务能够提供面向 x86、Arm和 RISC-V 全部三大行业主流指令集架构优化的技术。而且,英特尔已经看到代工客户对支持更多 RISC-V IP 模块产品的强劲需求。

英特尔 eASIC 设备:

从 FPGA 到 ASIC 的捷径

为了适应各种业务和开发模式,英特尔还提供了先进的英特尔 eASIC 设备和 ASIC 选择方案。英特尔 eASIC 设备属于结构化 ASIC,这是一种介于 FPGA 和标准单元 ASIC 二者之间的中间技术。而标准单元 ASIC 则可以利用英特尔晶圆代工服务创建。该服务是一种完全垂直化的独立代工业务,旨在帮助满足全球对半导体不断增长的需求。

英特尔 eASIC 设备性能介于 FPGA 和 ASIC 实现之间。使用英特尔 eASIC 设备,既可以保持与 FPGA 实现相同的主频,又能够降低功耗,还可以在保持散热/功耗预算不变的同时提高性能。与标准单元 ASIC 相比,英特尔 eASIC 设备上市时间 (TTM) 更快,一次性成本投入 (NRE) 更低。相比之下,标准单元 ASIC 则能以更低的功耗提供更高的性能。一旦一种设计的英特尔 FPGA 实现得到验证,该设计就可以固化成为成本和功耗更低的英特尔 eASIC 设备或性能更高、功耗进一步降低的 ASIC。开发人员还可能会从该设计的英特尔 FPGA 实现开始,随后迁移到英特尔 eASIC 设备,然后再次迁移到完整的ASIC(图 1)。

英特尔提供从 FPGA 到英特尔 eASIC 设备和 ASIC 的迁移路径,以减少成本、降低功耗、提升性能。

英特尔的 RISC-V 策略既支持基于英特尔 FPGA 开发 RISC-V,也支持后续部署到英特尔 FPGA、英特尔 eASIC 设备和ASIC(包括英特尔晶圆代工服务提供的 ASIC)。除了英特尔之外,其他公司较难提供从 FPGA 到英特尔 eASIC 设备再到ASIC 这些能够减少成本、降低功耗、提升性能的迁移路径。

RISC-V 对于FPGA 客户的价值

RISC-V 是一种开源硬件指令集架构,始于 2010 年。不同于大多数其他指令集架构,RISC-V 是在开源许可下提供的。RISC-V指令集规范定义了 32 位和 64 位寻址空间变体。指令集具有可变宽度和可扩展等特点,为解决广泛用例而设计。

除了具有开源指令集架构这一属性外,RISC-V 的成功还可以归因于其实现模块化、可扩展性、稳定性、效率和性能的设计宗旨。RISC-V 是一种“白板”设计,没有传统或反向兼容方面的限制或约束,因此能够为未来开放式计算设计的自由和创新铺平道路。得益于多方参与者的加入,RISC-V 正借助目前可用的多种开源架构实现方案推动多项创新。

商业企业要求指令集架构即使对部署多年的产品也仍保持稳定性。为了解决这一问题,2015 年 RISC-V 基金会 (RISC-VFoundation) 成立,负责制定、维护和发布 RISC-V 定义。为更好地发挥作用,这家非盈利性组织于 2020 年更名为 RISC-V International。

RISC-V 正迎来指数级增长。据 RISC-V International 报告1 ,“承诺加入 RISC-V 和对 RISC-V 的投资持续飙升。2021 年,RISC-V 成员人数增长了 130%,达到 2,478 名成员,其中包括 18 名高级成员”。随着数十亿芯片部署就绪,从嵌入式汽车到超大规模人工智能 (AI)、从 5G 到高性能计算 (HPC) 等,RISC-V 在各行各业以及各种实现方案中得到广泛的商业应用。

RISC-V 的开源性质开启了通过开放标准合作来实现处理器创新的新时代。多方参与者正在推进实现方案的创新,使广泛的开源生态系统迅速崛起。该生态系统涵盖复杂的硬件设计和验证工具、丰富的软件开发工具套件、操作系统 (OS) 和实时操作系统 (RTOS) 端口等。硬核和软核 RISC-V 处理器的激增也为应用在不同实现方案之间的移植和应用的长期维护提供了极大的便利条件。人们会看到,从一开始就是为充分利用 RISC-V 架构的优势而开发的应用将大量涌现。

就 FPGA 而言,可在设备的可编程逻辑中例化一个或多个软核处理器,从而使设计人员能够将可编程微控制器和/或微处理器核添加到自己的设计中。同样,对于在芯片中直接集成了一个、两个或四个 Arm 硬核处理器的英特尔 片上系统 (SoC) FPGA来说,必要时可在设备的可编程逻辑中例化更多软核处理器。

自 2004 年推出以来,英特尔的 32 位 Nios II 处理器一直是使用英特尔 FPGA 和 SoC FPGA 的设计人员选择的软核处理器。多年来,Nios II 处理器积累形成了由开发人员、工具、软件和软件 IP 模块组成的大型生态系统。

现在,英特尔已推出基于开源 RISC-V 指令集架构、面向英特尔 FPGA 的新一代软核处理器 Nios V 处理器。Nios V 处理器家族的第一款产品是 Nios V/m(“微控制器”版)。英特尔计划增加更多 Nios V 处理器变体,包括一个“通用”版、一个“应用类”版和一个“Linux”版,其中“Linux”版是能够运行 Linux 内核的 64 位处理器。此外,英特尔还会加大对包括 Zephyr、FreeRTOS 和Linux 在内的广泛操作系统的支持。

利用 Nios 处理器中的 RISC-V 将会极大拓展当下广泛的 Nios 生态系统,为基于 FPGA 的系统开发人员提供更大的灵活性、更出色的性能。Nios V 处理器采用与 Nios II 处理器相同的简单设计流程,可通过英特尔 Quartus Prime Pro Edition Software 获得。让现有基于 Nios II 处理器的设计的创建者特别感兴趣的是,他们可以把设计快速、轻松地移植到 Nios V 处理器。

由于 RISC-V 指令集架构内已实现多项架构升级,与现有的软核处理器相比,Nios V 软核处理器能提供更好的性能。此外,RISC-V 还有一个关键优势,那就是软件可移植性和稳定性。举例来说,开发人员可以利用软核版 RISC-V 在 FPGA 中开始一项设计,所编写的任何在初始 RISC-V 软核上运行的软件今后都可以在任何其他 RISC-V 核上运行。

RISC-V 另一个非常重要的优势是,广泛的开源生态系统迅速崛起。这一生态系统涵盖硬件设计和验证工具、软件开发工具(例如编译器和调试器)、操作系统 (OS) 和 RTOS 端口等。

英特尔大力投资 RISC-V 的一个例证是,英特尔通过与知名的RISC-V 工具供应商和 RISC-V International 成员 Ashling 合作,向 FPGA 客户提供面向 RiscFree 集成开发环境和统一调试器的完整开源工具解决方案。

RiscFree 对于 FPGA

和 ASIC 客户的价值

如今的 SoC 和系统级封装 (SiP) 设计正变得越来越复杂,这是因为芯片设计人员需要将更多的功能集成到单一的器件和单一的封装中,以满足市场对于更多功能、更高性能和更低功耗的需求。由于制程工艺的改进出现瓶颈,设计人员只得不断采用多核设计。此外,他们还将多种异构处理器架构(如 RISC-V、Arm和 x86)整合到同一 SoC 或 SiP 中。

促使 RISC-V 获得成功的一个主要因素是,不同的公司和实体可以将指令集架构作为自己独特的差异化实现方案(例如不同的数据宽度、管道宽度和管道架构)的基础。这使 RISC-V 处理器能够以广泛的形式出现,从面向边缘微控制器应用的基于 32 位 FPGA 的软核处理器到面向云端高性能计算应用的基于 64 位 SoC 的硬核处理器,无所不包。

Ashling 的 RiscFree 集成开发环境和统一调试器为全部 RISC-V实现提供支持。自推出以来,RiscFree 工具链稳步在嵌入式工具市场拿下市场份额,在 RISC-V 市场上更以其易用性、广泛的功能和插件式架构而表现抢眼。

RiscFree 可以针对上述设备使用单一调试探针,从单一软件环境提供全面开源的多核(同构和异构)调试解决方案,为 ASIC 客户带来附加价值。RiscFree 完全支持 Nios V 处理器,同样也可为 FPGA 客户带来附加价值。

就英特尔 FPGA 而言,RiscFree 包括一个开源的、基于 Eclipse 的集成开发环境、编译器、调试器和跟踪程序。这种单次安装程序开箱可用,可为基于 RISC-V 指令集架构的所有 32 位和 64 位Nios V 软核处理器提供 RiscFree 软件开发和调试支持。

除了自定义集成和支持向 Nios V 处理器扩展外,RiscFree 还支持英特尔 Agilex 、英特尔 Stratix 10、英特尔 Arria 10和英特尔 Cyclone 10 GX 设备,以及后续的更多产品系列。

Ashling 与英特尔合作的价值

自 1982 年以来,Ashling 一直是重要的嵌入式开发工具和服务提供商,有着 30 余年的嵌入式系统工具开发经验。作为 RISC-VInternational 的长期成员,Ashling 始终密切关注 RISC-V 的发展,尤其重视调试标准及跟踪标准。作为跟踪技术委员会 (Tracecommittee) 的副主席,Ashling 参与制定了第一批定义 RISC-V 实时跟踪的标准。

与 Ashling 合作,英特尔便有了自己的工具提供商,可确保其所有 Nios V 处理器的工具需求均能得到满足,包括由集成开发环境、编译器、调试器及 Nios V 处理器和 Arm 处理器跟踪支持组成的完整开源工具链。

两家公司已计划保持长期合作,因此,随着英特尔 Nios V处理器家族的发展壮大,工具链也会随之发展,以确保能够充分支持新产品和新功能。

Ashling 与英特尔团队在工程设计方面的合作将确保 Ashling 软件开发与英特尔 FPGA 开发工具链紧密耦合,例如:

01项目管理器和构建管理器包括 Make 和 Cmake 支持,可快速导入、构建和调试英特尔 Quartus 软件创建的应用框架。

02Nios V GCC 编译器工具链完全整合到 RiscFree 集成开发环境中,可以为使用 Nios V HAL API 接入硬件的 newlib和 picolibc 运行时库提供支持。

03RiscFree 提供运行时调试功能,可以支持英特尔 FPGA Download Cable II (USB Blaster II)、Nios V 和 Arm 处理器内核寄存器虚拟化,以及对 Nios V 和 Arm 两种处理器内核的实时片上和片下跟踪。

04RiscFree 还为 Zephyr、FreeRTOS、uC/OS-II 以及完整的目标(多核/多 Hart)Linux 内核等各种 OS 和 RTOS 解决方案提供感知调试能力,同时也支持设备驱动程序和应用调试。

05RiscFree 支持面向 Nios V 处理器的自定义指令和扩展。

在很多同时采用 Arm 和 RISC-V 处理器内核(硬核和/或软核)的开发环境中,必须运用多种调试器,一种用于 Arm 处理器,一种用于 RISC-V 处理器。经过比较,单个 RiscFree 实例支持调试任意数量的异构或同构内核;例如,同时调试英特尔 FPGA Arm硬核和 Nios V 软核。

英特尔与竞争对手

多数竞争对手只提供闭源的专有解决方案,而英特尔则能让您全面获得开源 RISC-V 生态系统的支持。解决方案目前支持 RISC-V开发,后续还支持部署到英特尔 FPGA、英特尔的结构化 ASIC 和英特尔晶圆代工服务提供的 ASIC。

在 Ashling 及其 RiscFree 集成开发环境和统一调试器的支持下,英特尔作为开放式生态系统的合作伙伴,可以利用其 RISC-V 开发人员目前可用的易用开源工具,支持完整的跨越 FPGA、英特尔 eASIC 设备和 ASIC 的自定义逻辑连续体。

总结

除了向全球供应强大的微处理器,英特尔还开发了先进的 FPGA。FPGA 经过配置可以执行多种功能,包括例化一个或多个软核处理器。这些软核处理器的性能在嵌入式市场中变得越来越重要。

RISC-V 是一种开源硬件指令集架构。RISC-V 定义为一种“白板”设计,没有传统或反向兼容方面的限制或约束,其设计宗旨就是要实现模块化、可扩展性、稳定性、效率和性能。因此,RISC-V 正迎来指数级增长。

英特尔加入全球开放硬件标准组织 RISC-V International,积极发挥领导作用,致力于为所有行业利益相关者扩大 RISC-V 生态系统的潜力。

英特尔现已发布了基于开源 RISC-V 指令集架构、面向英特尔 FPGA 的新一代软核处理器 Nios V 处理器。除了面向 FPGA的软核 Nios V 处理器,英特尔还将提供面向英特尔 eASIC 设备和 ASIC 的硬核 RISC-V 实现方案。此外,英特尔还提供从FPGA 到英特尔 eASIC 设备和 ASIC 的迁移路径。除了英特尔之外,其他公司较难提供从 FPGA 到英特尔 eASIC 设备再到ASIC 这些能够减少成本、降低功耗、提升性能的迁移路径。

英特尔的合作伙伴 Ashling 是 RISC-V International 的长期成员,Ashling 的 RiscFree 集成开发环境和统一调试器为全部RISC-V 实现提供支持。自推出以来,RiscFree 工具链便凭借其易用性、广泛的功能和插件式架构,在包括 RISC-V 市场在内的嵌入式工具市场得到广泛应用。

Ashling 的 RiscFree 能够针对上述设备使用单一调试探针,从单一软件环境提供全面开源的多核(同构和异构)调试解决方案,为英特尔的 FPGA 和 ASIC 客户带来附加价值。

英特尔计划加大投资力度,以加强 RISC-V 生态系统建设并推动 RISC-V 进一步落地。在英特尔的组织下,这些投资将帮助具有开创性的 RISC-V 公司通过在技术协同优化、优先晶圆共乘服务、支持客户设计、建立开发板和发展软件基础设施这些方面开展合作,更快实现创新。

原文标题:白皮书丨英特尔携手知名RISC-V工具提供商Ashling,着力扩展多平台RISC-V支持

文章出处:【微信公众号:英特尔FPGA】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21743浏览量

603563 -

英特尔

+关注

关注

61文章

9969浏览量

171812 -

RISC-V

+关注

关注

45文章

2283浏览量

46177

原文标题:白皮书丨英特尔携手知名RISC-V工具提供商Ashling,着力扩展多平台RISC-V支持

文章出处:【微信号:英特尔FPGA,微信公众号:英特尔FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

世纪大并购!传高通有意整体收购英特尔,英特尔最新回应

英特尔推出全新英特尔锐炫B系列显卡

英特尔CEO Gelsinger宣布退休

刚刚!英特尔最新回应

从运动员到开发者: 英特尔以开放式AI系统应对多重挑战

英特尔加速AI PC发展,预计到2028年占据80%市场份额

英特尔CEO:AI时代英特尔动力不减

BittWare提供基于英特尔Agilex™ 7 FPGA最新加速板

英特尔旗下FPGA公司Altera正式亮相

英特尔成立全新独立运营的FPGA公司Altera

英特尔旗下Altera正式独立运作,FPGA市场将迎来怎样的巨变?

英特尔成立Altera新公司,专注FPGA端到端解决方案

英特尔eASIC设备:从FPGA到ASIC的捷径

英特尔eASIC设备:从FPGA到ASIC的捷径

评论