介绍

TiN硬掩模(TiN-HM)集成方案已广泛用于BEOL图案化,以避免等离子体灰化过程中的超低k (ULK)损伤。随着技术节点的进步,新的集成方案必须被用于利用193 nm浸没光刻来图案化80 nm间距以下的特征。特别是,为了确保自对准通孔(SAV)集成,需要更厚的TiN-HM,以解决由光刻-蚀刻-光刻-蚀刻(LELE)未对准引起的通孔-金属产量不足和TDDB问题。由于结构的高纵横比,如果不去除厚的TiN,则Cu填充工艺明显更加困难。此外,使用TiN硬掩模时,在线蚀刻和金属沉积之间可能会形成时间相关的晶体生长(TiCOF)残留物,这也会阻碍铜填充。在线蚀刻之后的蚀刻后处理是该问题的一个解决方案,但是N2等离子体不足以有效地完全抑制残留物,并且中提出的CH4处理可能难以对14 nm节点实施,因此有效的湿法剥离和清洁提供了更好的解决方案。

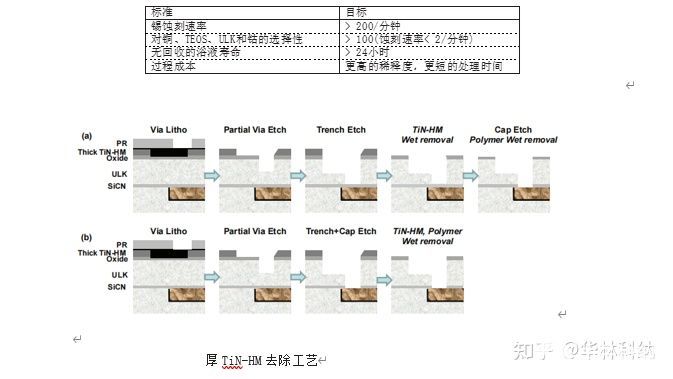

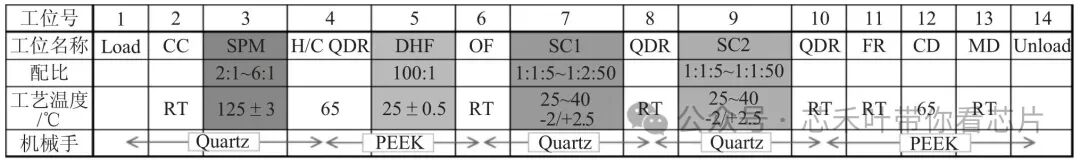

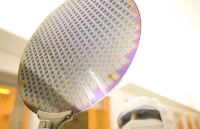

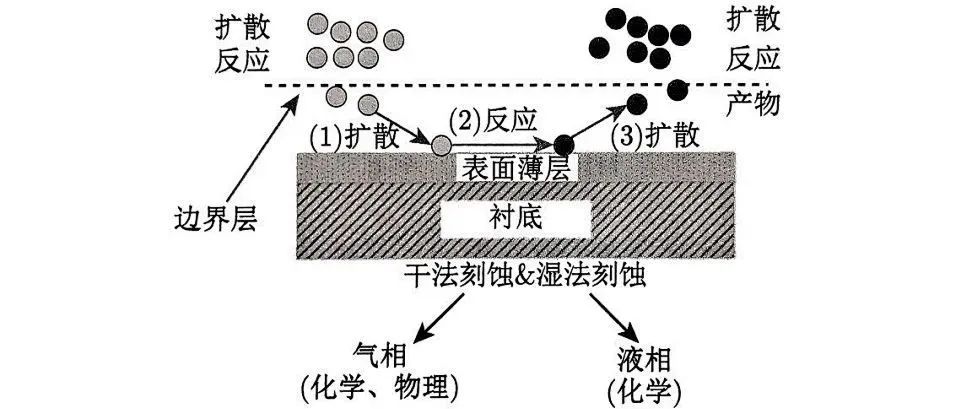

我们华林科纳开发了利用无铜暴露的SiCN保留方案去除厚TiN-HM的方法,并显示出良好的电气和可靠性性能,但仍有降低工业挑战成本的空间。在本文中,我们通过使用一体化湿法方案图1作为解决这些问题的替代方法,展示了厚锡-HM去除工艺,重点关注实现大规模生产的以下标准(如表1所示)。

结果和讨论

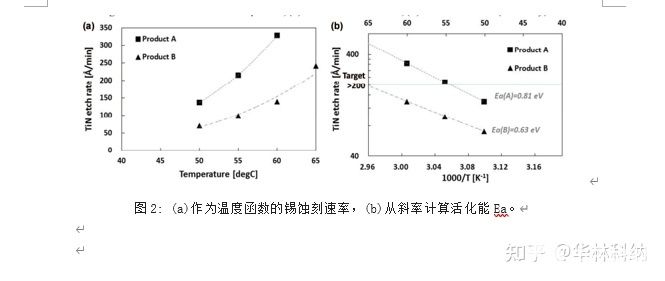

首先,为了达到目标值(> 200/min),研究了每种产品的锡蚀刻速率的温度依赖性。图2显示了锡蚀刻速率和从每个斜率计算的活化能(Ea)的结果。发现产品A和B分别需要超过55℃和65℃才能达到目标。活化能Ea(A)和Ea(B)分别表现出0.81eV (= 78.2 kJ/mol)和0.68eV (= 65.6 kJ/mol),对于10 C,锡蚀刻速率上升约2.4和2.0倍一般情况下,温度从50°C上升到60°C。由于两种产品的活化能相似,这无法解释观察到的蚀刻速率差异。应该考虑其他参数,例如反应物和副产物的浓度、静电效应和在锡表面的吸附/解吸机制。

随后,研究了作为温度函数的TEOS和铜蚀刻速率,以确认蚀刻选择性,如图3所示。对目标内的TEOS或铜蚀刻速率没有影响(< 2ω/min)。图4示出了在晶片处理后没有化学回收的情况下,锡和铜的蚀刻速率作为浴寿命的函数(仅混合槽再循环回路)。产品A和B都没有显示出蚀刻速率随浴寿命的显著变化,这表明了良好的热稳定性。

决定TiN-HM去除率的因素包括TiN薄膜性质(特别是Ti:N:O比率)、可用氧化剂、与其他配方成分(腐蚀抑制剂、蚀刻剂等)的相互作用、温度和pH值。TiN的溶解需要氧化剂将Ti3+转化为Ti4+以及Ti4+络合剂来克服表面氧化物/氮氧化物钝化膜[7]。本研究中考虑的两种配方都利用碱性pH值和添加氧化剂H2O2来驱动TiN-HM溶解反应,此处显示了其中的一个示例:

ti3 ++ 3/2h2o 2+4oh-[TiO 2(OH)3]-+2 H2O(1)

对于产品A,氧化剂以高比例(9:1)加入,这提供了过量的过氧化氢,有助于保持Ti4+以络合物如[Ti(O2)(OH)3]形式的溶解度。为了在具有高H2O2浓度的混合物中保持高的锡蚀刻速率和TEOS/铜相容性,配方的pH值必须在整个浴寿命中保持相对稳定,并且保护金属和电介质表面的抗氧化组分是必不可少的。产品A就是这样设计的。蚀刻剂是同类中最热稳定抗氧化的,在特殊添加剂中,一种通过电子耗尽结构防止氧化,而另一种通过最可能的氧化分解机理中活化络合物的应变构象保护。

最后,通过使用在最小成本条件下加工的产品A,在14 nm节点BEOL图案化晶片上证实了TiCOF晶体去除和Cu线填充效率。如图5所示,在50℃和55℃下观察到非常好的TiCOF晶体生长去除效率(100%)。此外,图6示出了通过锡去除工艺实现了优异的Cu线填充,并且可以实现优化的工艺(条件2)以完全防止在金属化步骤期间形成Cu空洞。

结论

针对14 nm BEOL技术节点开发了具有蚀刻后残留物清洗的厚TiN-HM湿法去除工艺,该工艺能够同时进行通孔/沟槽轮廓控制和通孔底部的铜聚合物去除,以改善铜填充。最佳候选产品能够实现工业化目标(高锡蚀刻速率、对金属和电介质的高选择性、高温下24小时的浴寿命)。除了优异的Cu线填充之外,通过使用14nm节点BEOL图案化结构,还实现了TiCOF晶体生长去除效率而没有CD损失。

审核编辑:符乾江

-

传感器

+关注

关注

2578文章

55567浏览量

794257 -

半导体

+关注

关注

339文章

31279浏览量

266789

发布评论请先 登录

集成电路制造中常用湿法清洗和腐蚀工艺介绍

湿法刻蚀工作台工艺流程

晶圆湿法刻蚀技术有哪些优点

半导体湿法腐蚀工艺中,如何选择合适的掩模图形来控制腐蚀区域?

湿法刻蚀的工艺指标有哪些

湿法腐蚀工艺处理硅片的原理介绍

半导体湿法工艺用高精度温控器吗

湿法刻蚀sc2工艺应用是什么

半导体湿法flush是什么意思

光阻去除属于什么制程

光阻去除工艺有哪些

一文详解湿法刻蚀工艺

TiN硬掩模湿法去除工艺的介绍

TiN硬掩模湿法去除工艺的介绍

评论