引言

随着对多功能移动消费电子设备需求的增加,半导体芯片互连密度的复杂性不断增加。传统的芯片到封装集成(CPI)使用引线键合将键合焊盘互连到封装引线。随着芯片规模向原子级发展,采用硅通孔(TSV)技术的芯片间互连成为一种极具吸引力的潜在解决方案,可实现更高的性能和更低的制造成本。穿过硅芯片的垂直电互连可以缩短芯片间互连的长度,并实现更紧凑的CPI互连结构。在TSV制造中,硅中具有受控侧壁轮廓的高深宽比结构对于纳米和微米尺度的微电子器件非常重要。

关键词:硅通孔,等离子蚀刻

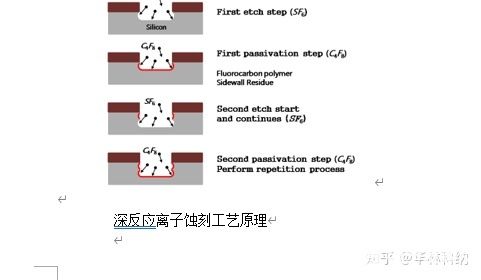

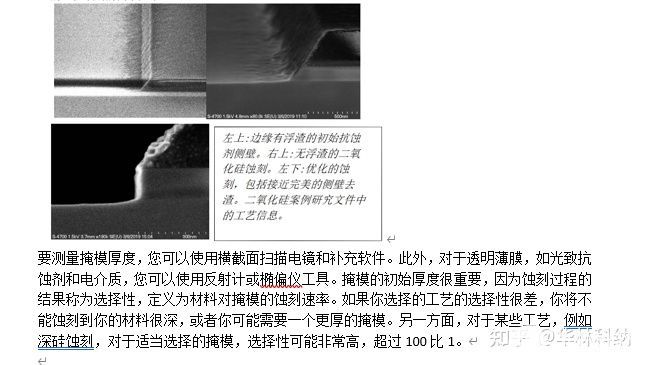

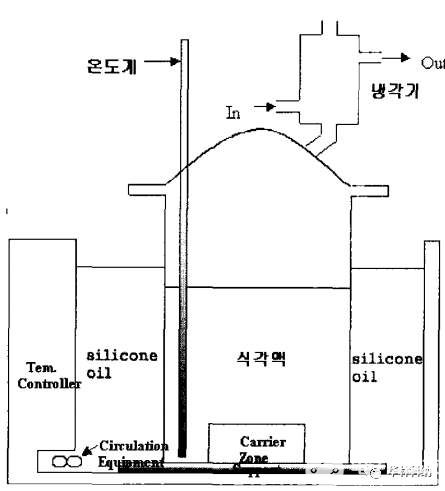

TSV互连技术包括深度硅蚀刻用于通孔形成、绝缘衬垫层沉积和用导电金属填充通孔。通过等离子体蚀刻可以获得垂直和深的硅通孔蚀刻,但是这仍然是一种具有挑战性的复杂制造工艺。深硅通孔蚀刻需要高能离子轰击,以提供足够的动能来破坏晶片上硅原子的化学键,以及高活性自由基的直接化学反应,从而形成挥发性蚀刻副产物。深通孔区域中的离子充电可能导致硅蚀刻的局部化。反应性自由基可以增加硅通孔的蚀刻速率,但是它也增加了tsv的横向蚀刻速率。增加的离子轰击会导致通孔蚀刻掩模的腐蚀,质量差的蚀刻掩模会导致粗糙的侧壁轮廓。最近的研究采用碳氢化合物和氢氟碳化合物(HFC)气体化学,通过形成侧壁钝化来改善TSV蚀刻剖面,并防止蚀刻掩模腐蚀。

在这项研究中,我们调查了不同类型的影响

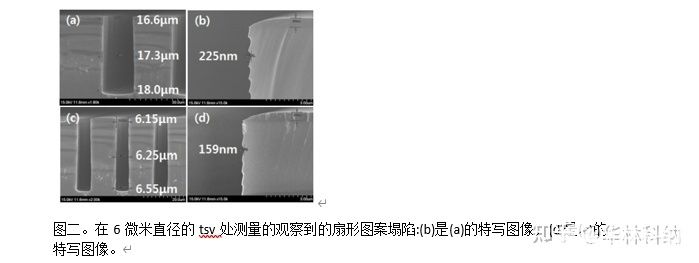

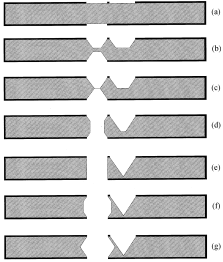

TSV蚀刻中的蚀刻掩模以及tsv中的侧壁轮廓的影响。我们首先用传统的光刻胶(PR)掩模检查了TSV的侧壁轮廓,并研究了两种类型的硬掩模对tsv侧壁轮廓的影响。研究的TSV蚀刻材料是光致抗蚀剂、二氧化硅和铝。随着掩模的图案尺寸变窄,蚀刻深度和蚀刻速率趋于降低。

结果

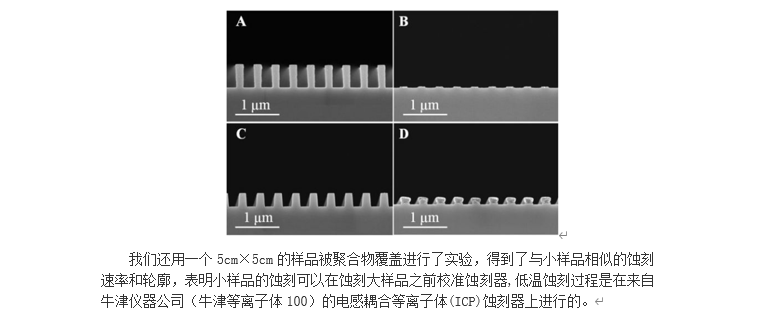

使用三种不同蚀刻掩模的蚀刻轮廓结果:光刻胶、氧化物和金属。评估不同类型的蚀刻掩模所考虑的因素是底切、残留和蚀刻速率。

氧化物掩模(硬掩模1)

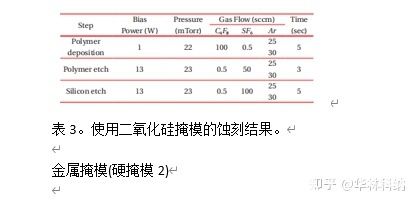

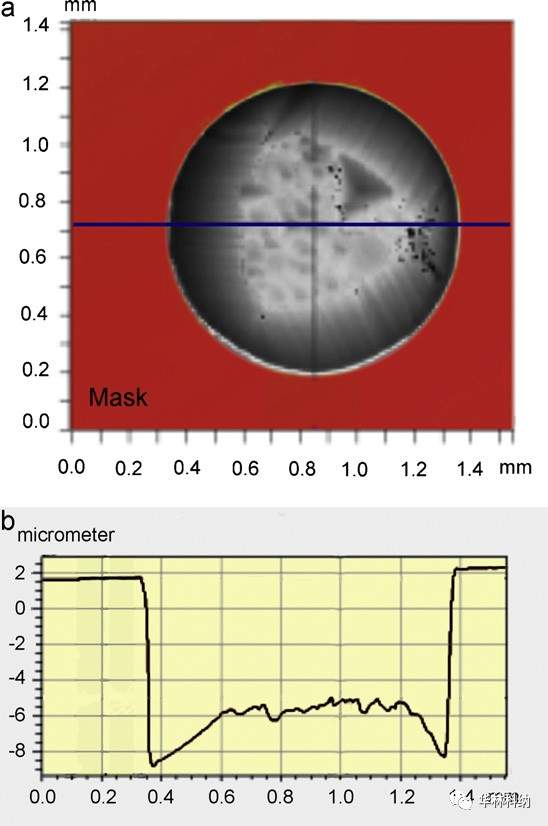

光致抗蚀剂是用于较大直径的tsv的有用的蚀刻掩模材料,但是可能不适合用于塌陷扇形的较小尺寸的通孔。为了进一步研究用于较小尺寸TSV图案化的光致抗蚀剂的替代物,我们研究了硬掩模材料。第一种候选材料是二氧化硅(SiO2),蚀刻后的TSV剖面的几何特征如表3所示。直径大于20微米的tsv超出了本实验的范围。以前在ARDE也观察到较大尺寸的TSV蚀刻,因为不管蚀刻掩模材料的类型如何,通孔直径都在减小。

就采用二氧化硅硬掩模的硅蚀刻速率而言,成功证明了TSV蚀刻掩模低至3微米直径tsv的潜力。我们在直径为2微米的TSV中观察到非均匀蚀刻的TSV剖面,这被称为负载效应。

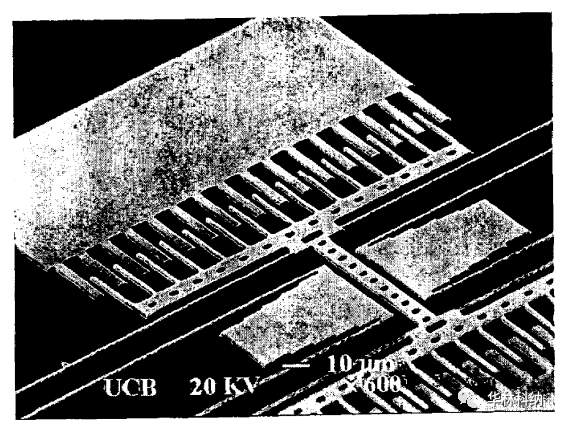

在半导体制造中使用的金属候选物中,通常选择铝,因为它们易于制造并且与常规制造工艺步骤兼容。在需要铜金属互连来减少互连延迟之前,铝已经广泛用于金属互连。在许多半导体产品中,它仍然用于后段制程(BEOL)互连和焊盘。虽然在传统的半导体制造工艺中不使用金属蚀刻掩模,但是我们对这种用于成功制造tsv的更精细特征的耐用且可靠的蚀刻掩模感兴趣。表4显示了使用金属硬掩模的通孔蚀刻结果。随着图案尺寸变得越来越小,也观察到了ARDE,如先前用不同的候选掩模进行的实验所示。

比较表3和表4中所示的蚀刻速率,两种类型的硬掩模在各种尺寸的tsv中显示出相似的蚀刻速率。与硬氧化物掩模不同,金属掩模显示出改善的底切和扇形塌陷,并且蚀刻轮廓总结在表4中。图6示出了在2个微米直径的TSV中的TSV蚀刻轮廓。

结论

在这个实验中,我们华林科纳半导体研究了用于制造更精细尺寸的硅通孔(tsv)的蚀刻掩模材料。传统上用作硅蚀刻掩模的光致抗蚀剂可能不适合使用Bosch工艺的TSV制造的更精细的特征,并且我们建议对更精细的tsv使用硬掩模以减少底切和塌陷的扇形的数量。铝中的硬金属掩模提供了直径小至2微米的tsv的优良侧壁轮廓。二氧化硅硬掩模在制造小于20微米、直径小至几微米的tsv时是有用的,但是氧化物掩模下的底切问题仍然存在。不考虑蚀刻硬掩模材料,观察到来自离子遮蔽的ARDE。

审核编辑:符乾江

-

半导体

+关注

关注

334文章

27367浏览量

218755 -

蚀刻

+关注

关注

9文章

414浏览量

15387

发布评论请先 登录

相关推荐

一种用非金属掩模层蚀刻碳化硅的方法

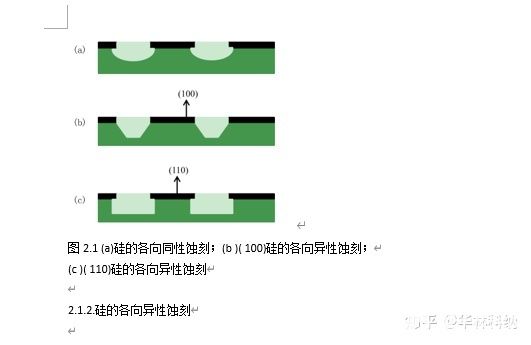

使用KOH各向异性蚀刻Si的光学器件的单掩模微制造(下)

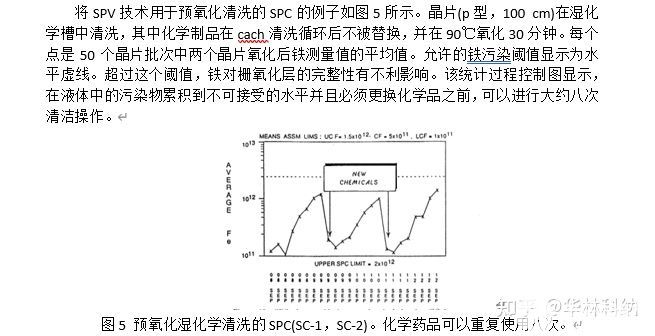

硅湿法蚀刻中的表面活性剂

掩模曝光剂量的精细控制工艺设计

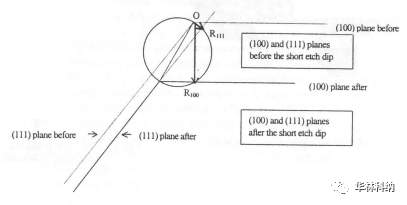

氢氧化钾在凸角处的蚀刻行为

各向同性和各向异性工艺如何用于改善硅湿蚀刻

详解单晶硅的各向异性蚀刻特性

采用湿蚀刻技术制备黑硅

不同掩模材料对400nm沥青光栅蚀刻特性的影响

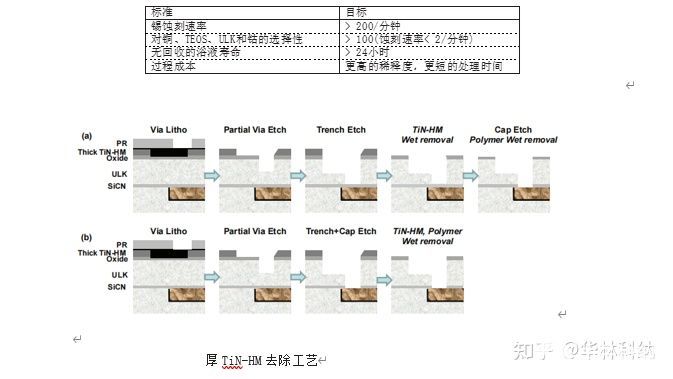

TiN硬掩模湿法去除工艺的介绍

一种穿过衬底的通孔蚀刻工艺

使用硬掩模进行更精细的硅通孔蚀刻

使用硬掩模进行更精细的硅通孔蚀刻

评论