引言

我们华林科纳描述了一种与去离子水中铜的蚀刻相关的新的成品率损失机制。在预金属化湿法清洗过程中,含有高浓度溶解氧的水会蚀刻通孔底部的铜。蚀刻在金属化后残留的Cu中产生空隙,导致受影响的阵列电路中的高电阻和功能故障。去离子水中的溶解氧浓度必须最小化,以防止铜的蚀刻。

介绍

与铝互连相比,铜互连具有更高的电阻率和可靠性,因此在微电子行业获得了广泛认可。然而,存在许多与铜金属化相关的产量问题,尤其是在湿法化学清洗期间的稳定性方面。在与化学机械抛光(CMP) 或通孔蚀刻相关的湿法清洗后(即在蚀刻停止移除之前)[5],经常会观察到铜的腐蚀或蚀刻。

已经报道了三种不同类型的铜互连腐蚀;光腐蚀、电偶腐蚀和化学腐蚀。要发生腐蚀,至少需要两个反应;阳极反应和阴极反应。在阳极,金属表面被氧化,形成金属离子和电子;

铜(s) d Cu2+ + 2e- (1)

在阴极,电子被几种可能的电子消耗

此外,阳极和阴极之间必须有电连接,并且必须有电解质与阳极和阴极都接触。

铜互连的腐蚀通常取决于图案。当Cu电连接到衬底中的p型Si区时,在光的存在下观察到光腐蚀。连接到p型硅(阳极)的铜比连接到n型区域(阴极)的铜处于更正的电位,使其更容易受到腐蚀。光允许电流流过硅并完成具有电解质的电化学电池,提供腐蚀发生所需的电荷载体,在等式和中)。

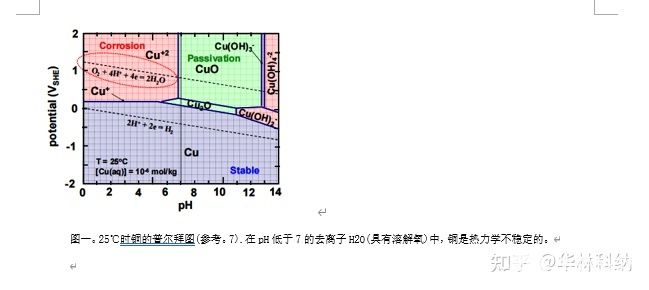

铜的蚀刻通常与去H2O冲洗有关。起初,这似乎是一个令人惊讶的结果,因为迪H2O

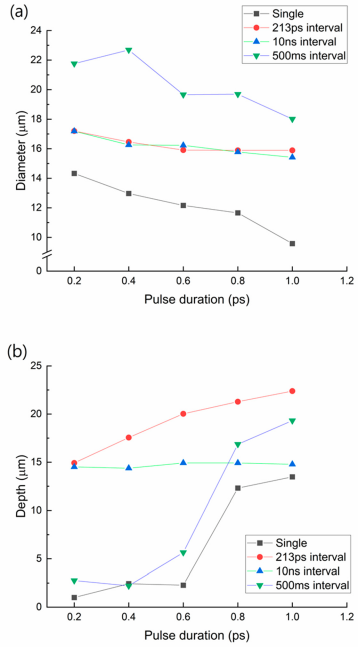

通常被认为是一种无害的清洁处理。然而,在电化学文献中,众所周知,在氧气存在下,铜在H2O中是热力学不稳定的(图1)。如果去H2O中存在氧,它会消耗铜溶解产生的过量电子(分别为方程式2b和1),从而使铜腐蚀继续进行。铜在去离子水H2O中的腐蚀速率取决于溶解氧浓度、温度和pH值,溶解氧浓度为200至300 ppb时的最大腐蚀速率。在去离子H2O中使用溶解氧被认为是提高化学机械抛光后清洗效果的一种方法(即更有效地去除表面的铜污染物)。然而,去离子H2O中的高氧浓度会在CMP后清洗过程中造成腐蚀。通孔蚀刻后DI H2O冲洗液中铜的蚀刻也与“清洗液中的氧气”的存在有关。

实验

样品采用0.13 m CMOS工艺制造,在FSG电介质中采用过孔优先双镶嵌Cu。金属化前的预清洗包括稀HF和去离子水冲洗。

在完全集成的逻辑芯片上检测到电气故障。使用扫描链方法定位产品芯片中故障的电位置。扫描链嵌入在逻辑电路中,以测试电路的小子集。添加额外的测试引脚,为电路的关键部分提供输入和输出。当在扫描链中检测到故障时,故障区域相对较小,因此可以通过分层技术容易地检测到。

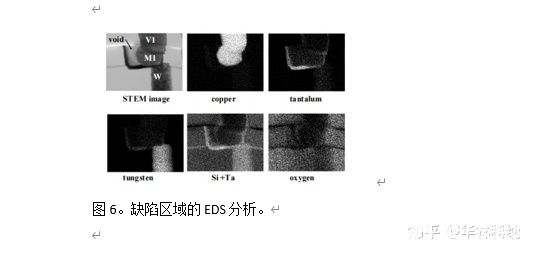

不合格的芯片被分层,然后通过扫描电子显微镜(SEM)、透射电子显微镜(TEM)和扫描透射电子显微镜(STEM)进行分析。使用能量色散谱(EDS)分析了STEM中失效结构的化学成分(JEOL,2010F)。TEM样品制备包括剥离至V1,用SiO2覆盖以保护表面,然后使用聚焦离子束(FIB)研磨从感兴趣的区域提取薄样品(150 nm)。

讨论

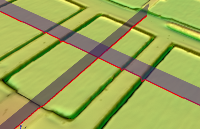

湿法清洗过程中铜的蚀刻是专用阵列电路所独有的。没有这种阵列的其他电路具有高产量(图2)。因此,特殊阵列中的下层硅会导致腐蚀。这一点通过运行一些晶片得到了证实蚀刻不足。自动光学显微镜检查显示在M1中没有空隙,表明如果M1是浮动的,就不会发生铜的蚀刻。

已知水中溶解的氧气会增强铜的腐蚀(图1)。因此,研究了M1铜中空隙的形成作为去离子水冲洗中O2浓度的函数。自动光学显微镜检查显示,可以通过最小化去离子水中的O2含量来消除空隙。这通过在具有高百分比的特殊阵列的扫描链上的电测量来证实(图8)。这也是特殊阵列中M1铜的蚀刻显然与水冲洗中的高O2浓度有关。

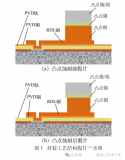

然而,确切机制仍不清楚。至少有两种可能;电偶腐蚀和结强化腐蚀(图9)。

由于水中氧气浓度较高,预计铜相对于钽衬里的电偶腐蚀会增强。所有表现出腐蚀的M1图案都具有最小宽度的线,因此钽和铜暴露在通孔底部的预清洗中。对于这种机理,铜是阳极,钽是阴极。O2的作用是消耗Ta阴极的电子(图9中的方程式(2b)和反应(a))。然而,还有许多其它部分接地的过孔,其中的M1金属不会被腐蚀,因此Si中的底层结肯定也起了作用。

下面的硅结的作用类似于光腐蚀中的结的作用。连接到p型结的Cu处于比连接到n型区的Cu更低的电位(因此更高易受腐蚀),如果向结施加偏压的话。向结施加偏压的一种方法是用光。

然而,即使在没有光的情况下也观察到M1铜的蚀刻,这表明光蚀刻不是机理。更可能的机制是O2在连接到n型区域的Cu处消耗电子,从而偏置结。

结论

我们华林科纳描述了一种新的成品率损失机理,它与去离子水中铜的腐蚀有关。在预金属化湿法清洗过程中,含有高浓度溶解氧的水会蚀刻通孔底部的铜。蚀刻在金属化后残留的Cu中产生空隙,导致受影响的阵列电路中的高电阻和功能故障。去离子水中的溶解氧浓度必须最小化,以防止铜的蚀刻。

审核编辑:符乾江

-

半导体

+关注

关注

334文章

27367浏览量

218789 -

蚀刻

+关注

关注

9文章

414浏览量

15389

发布评论请先 登录

相关推荐

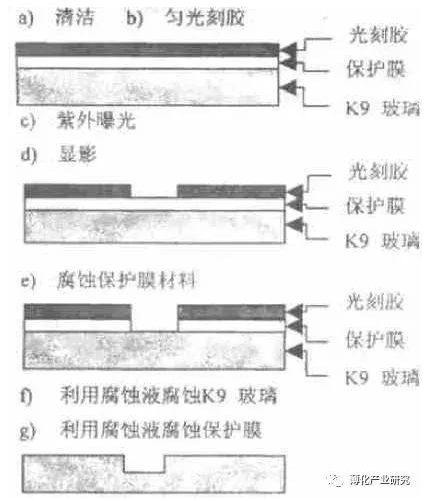

芯片湿法蚀刻工艺

上海伯东IBE离子束刻蚀机介绍

PCB设计中填充铜和网格铜有什么区别?

PCB设计中填充铜和网格铜有什么区别?

湿法蚀刻的发展

铜互连,尚能饭否?

基于光谱共焦技术的PCB蚀刻检测

利用贝塞尔光束、超短双脉冲激光和选择性化学蚀刻研究玻璃通孔(TGV)

关于两种蚀刻方式介绍

东京电子在日本东北部投巨资研发领先四代的大容量存储器

影响pcb蚀刻性能的五大因素有哪些?

电偶腐蚀对先进封装铜蚀刻工艺的影响

铜在去离子水中的蚀刻研究

铜在去离子水中的蚀刻研究

评论