摘要

本文以高速系统的信号/电源完整性分析和EMC分析的为基本出发点,着重介绍了高速PCB的信号和电源完整性分析的基本要领和设计准则,通过EDA分析工具实现PCB的建模与参数提取;通过电磁场分析工具完成网络参数定量分析,从最基本的设计方法入手,提出了高速PCB的信号/电源系统设计参数优化方案,指出了信号/电源完整性仿真设计和EMC设计的内在联系,最后介绍了利用EDA仿真工具和EMC测试验证相结合解决单板PCB设计的EMI问题的成功范例,希望本文总结的经验能给予正在从事高速系统仿真的设计开发人员和EDA设计人员解决此类问题的基本思路与方法。

引言

当今的高速PCB设计领域,由于芯片的高集成度使PCB的布局布线密度变大,同时信号的工作频率不断提高,信号边沿(Tr)的不断变陡,由此而引发的信号完整性和电源完整性问题给EDA设计人员和硬件开发人员带来前所未有的挑战,信号/电源完整性问题处理不当同时会带来一系列的EMC问题,给产品的可靠性造成危害。目前,基于Cadence公司SQ的板级与系统级互连仿真已经在广泛应用,在硬件设计流程中引入了SI/PI/EMI的仿真分析环节。信号完整性与电源完整性分析做的较成功的PCB,电磁兼容性(EMC)也明显改善。

信号/电源完整性分析通过对PCB的信号互连与电源分配系统(PDS)分析,使用EDA与电磁场分析软件找出PCB的噪声点并加以抑制,通过PCB的优化设计改善层间噪声与电源层和地线层之间的阻抗。降低信号的反射和串扰;改进信号的回流路径,降低电源分配系统阻抗,同步开关噪声,消除PCB上关键点和关键频率的谐振,合理放置去耦电容改善电源地的阻抗与谐振,使用屏蔽过孔等措施减小PCB的边缘辐射。

随着信号的Tr变快,产品的EMC问题成为EDA设计的最大难点。EMC问题由来已久,涉及面较广,随着信号速率的提高和芯片尺寸的减少,传统的EMI设计方法显得力不从心。解决EMC问题和解决其它SI问题显著的不同点在于EMC更依赖于测试,或者是仿真与测试过程两者的融合,不同类型的EMI包括来自于信号互连的连接器,电缆,PCB的连线以及边缘辐射等。

电源和信号完整性对EMI的性能有着直接的影响,从PCB设计阶段控制EMI,能起到事半功倍的作用。我们通常采用下列几种方法来分析并改进信号和电源完整性,从而减小EMI辐射。

1.减少电源地平面间噪声-电源完整性分析

2.优化电源地系统阻抗-电源完整性分析

3.降低串扰和反射-信号完整性分析

4.改善同步开关噪声-信号完整性分析

5.减少边缘辐射-信号完整性/电源完整性分析

一、关于电源完整性仿真的电容建模

1、非理想旁路电容的定义:

在电源系统的设计中,我们经常用到以下的三类电容:

1)旁路电容:主要作用是给交流信号提供低阻抗的回流路径;

2)去耦电容:增加电源和地的交流耦合,减少交流信号对电源的影响;

3)滤波电容:用于电源滤波电路中,消除电源纹波;

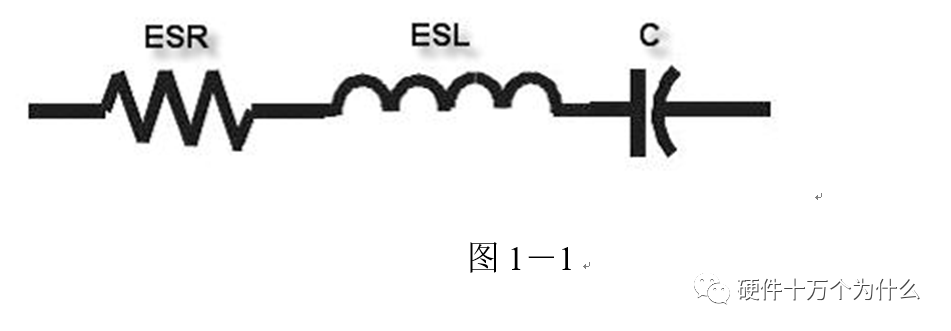

在电源完整性仿真中,我们主要研究对象是非理想化的旁路电容。对于理想的电容来说,不考虑寄生电感和等效串联电阻的影响,那么我们在电容设计上就没有任何顾虑,电容的值越大越好。但实际情况却与理论分析相差很远,并不是电容越大对高速电路越有利,反而在高频段往往采用小电容,电容的材料和制造工艺也有要求。要理解这个问题,我们首先必须了解实际电容器本身的特性,在频率很高时,电容不再被当作理想的电容看待。电容的寄生参数的影响不能忽略。考虑到电容具有一定的物理尺寸,以及起连接作用的安装焊盘和过孔,其寄生参数包括一个串联电感和串联电阻,由此得到如图1-1的电容模型。

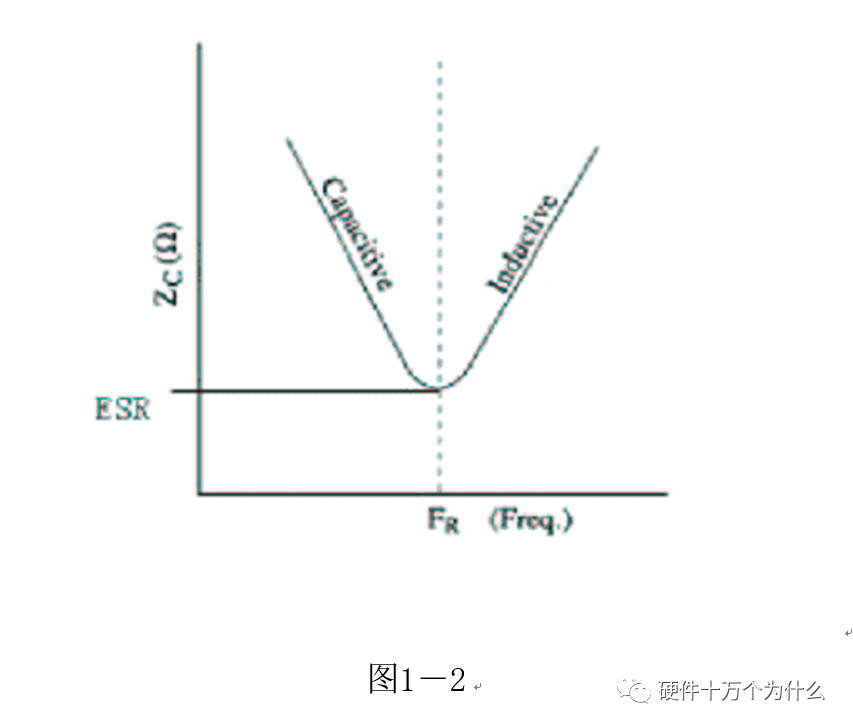

对电容的高频特性影响最大的则是ESR和ESL,我们通常采用图1-1中简化的电容模型。电容也可以看成是一个串联的谐振电路,当它在低频的情况(谐振频率以下),表现为电容性的器件,而当频率增加(超过谐振频率)的时候,它渐渐的表现为电感性的器件。也就是说它的阻抗随着频率的增加先增大后减小,等效阻抗的最小值发生在串联谐振频率处,这时候,电容的容抗和感抗正好抵消,表现为阻抗大小恰好等于寄生串联电阻ESR,变化曲线如图1-2所示:

从谐振频率的公式可以看出,电容大小和ESL值的变化都会影响电容器的谐振频率。由于电容在谐振点附近的阻抗最低,所以设计时尽量选用FR和实际工作频率相近的电容。如果工作的频率变化范围很大,则可以混合使用不同容值和FR电容,即同时选择一些FR较小的大电容和FR较大的小电容。

2、PI仿真电容及分布参数的建模:

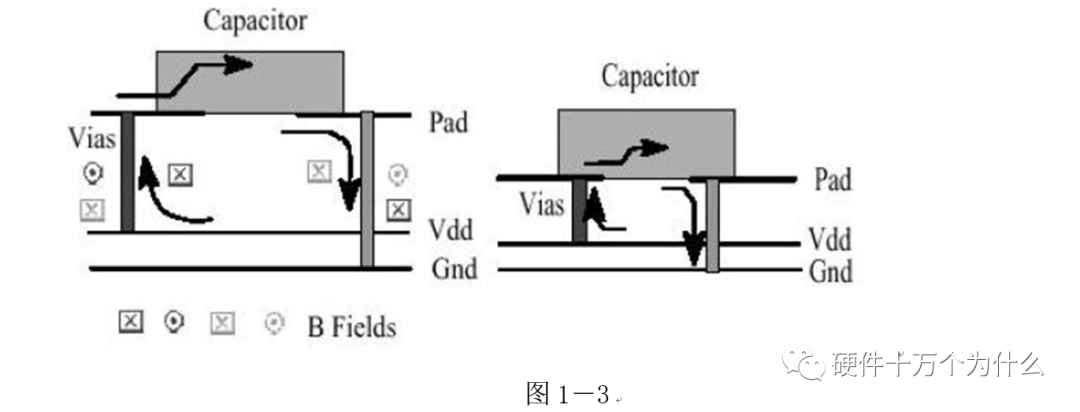

非理想旁路电容由ESR、C、ESL、引线和过孔等几部分组成,见图1-3所示。

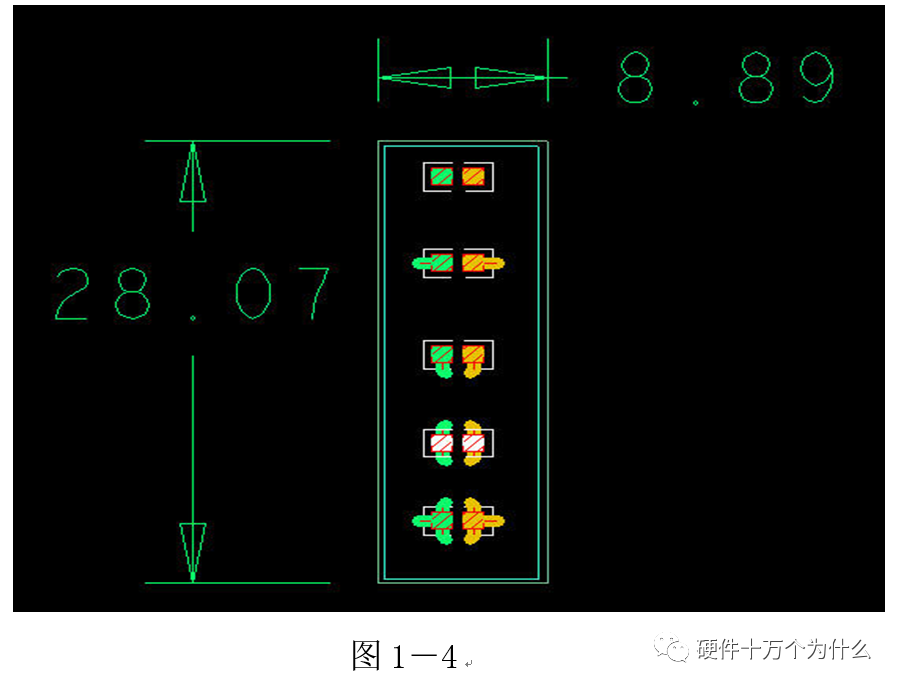

在高速PCB设计中,我们常用的电容引线方式有以下几种,为定量分析各种引线方式的影响和建模的需要,我们从正在设计中的单板中提取了用于分析的样板,见图1-4所示。

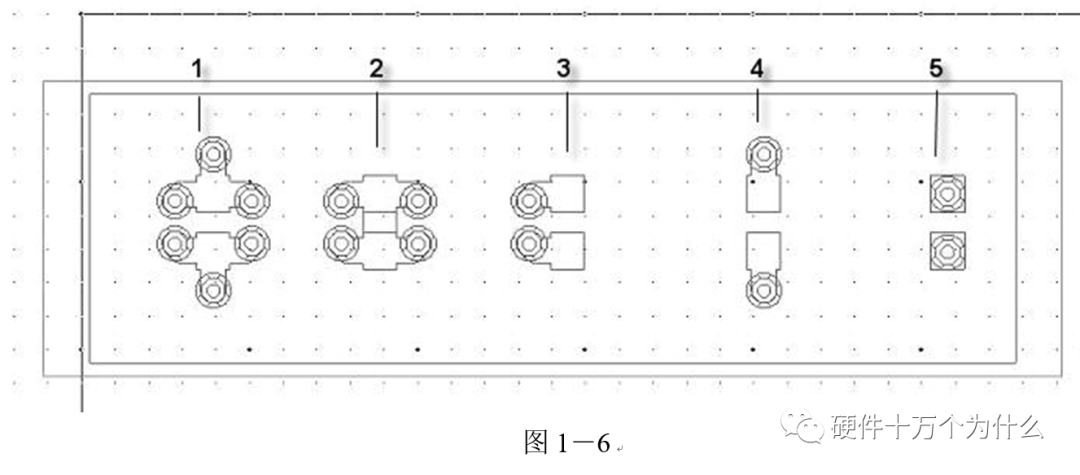

常见的电容的引线方式有以下5种,如图1-6所示,其中第5种在焊盘上开孔目前工艺不推荐,在此只作分析,首先,我们分别计算了VCC_3.3V到电容管脚的引线和过孔的电感,

得到以下5组数据(单位:亨利):

L001 2.82101E-010

L0022.70197E-010

L0038.36196E-010

L0049.23669E-010

L0053.65286E-010

为了尽量减小引线电感,在设计中我们可以优先采用第2种引线方式,其中第4种引线方式在传统的PCB设计中广泛采用,由于这种引线方式会带来较大的引线电感,建议在高速PCB设计中尽量不要采用。

接下来,我们对电源/地的回路作进一步分析,提取了第二种引线方式的SPICE子电路,得到的结果如下:

VCC3.3V到电容PIN1的子电路为:

.subcktcap_2_via_vcc 1 2 3

C0014 3 1.27114E-010

V0011 5 DC 0

L0015 6 1.39697E-010

R0016 4 0.00663062

V0024 7 DC 0

L0027 8 1.39697E-010

R0028 2 0.00663062

.ENDScap_2_via_vcc

电容PIN2到GND的子电路为:

.subckt cap_2_via_gnd 1 2 3

C0014 3 1.28742E-010

V0011 5 DC 0

L0015 6 2.75467E-010

R0016 4 0.00513052

V0024 7 DC 0

L0027 8 2.75467E-010

R0028 2 0.00513052

.ENDScap_2_via_gnd

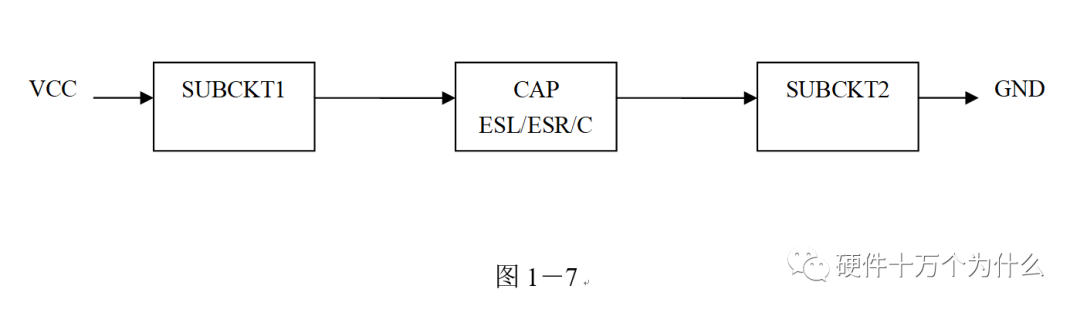

通过以上过程,我们得到了回路所有构件的RLC参数,由此我们可以建立以下电流回路,如图1-7所示。

VCC3.3V -----子电路1----- pin1-----电容(C/ESL/ESR)----- pin2 -----子电路2 ----- GND

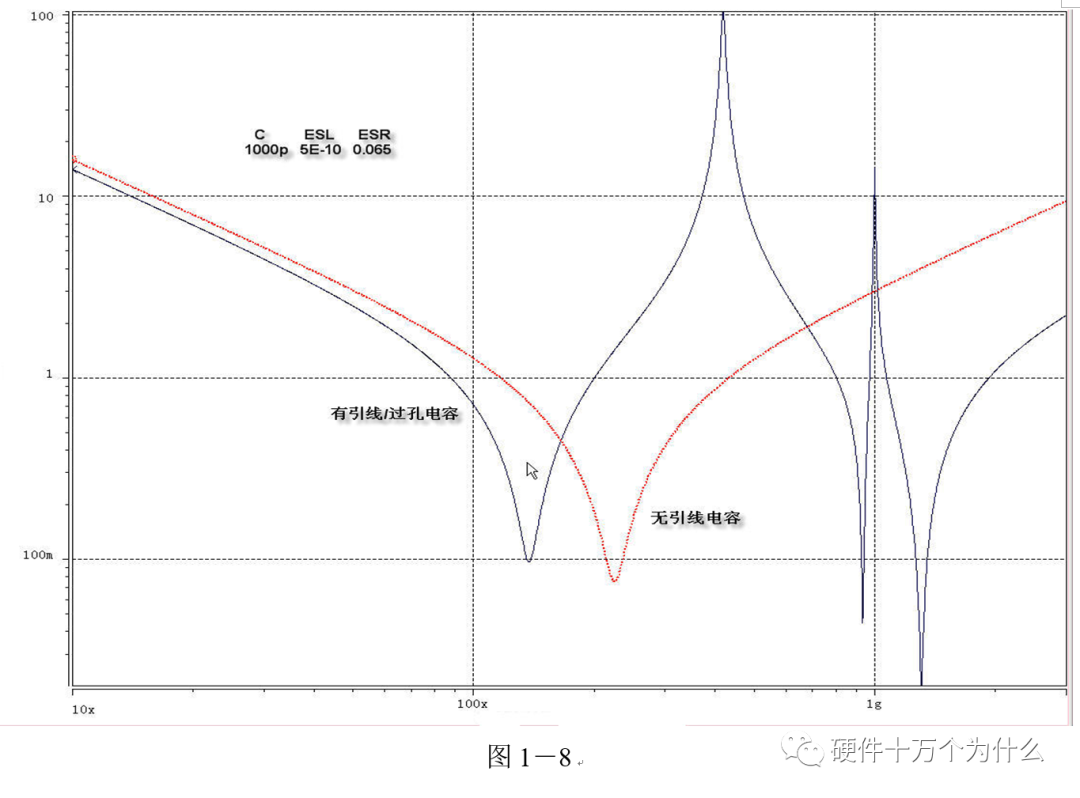

定义各部分子电路的连接关系,我们可以得出电容和引线/过孔对结果的影响,取电容值为:1000pf;ESL=5E-10;ESR=0.065(AVX),得到无引线电容和考虑过孔与引线电容的频率响应曲线如图所示,其中红色曲线为无引线电容的阻抗-频率曲线,蓝色曲线为有引线/过孔的阻抗-频率曲线,我们可以得出分析结果如图1-8所示。

1)由于引线及过孔的分布参数存在,电容的谐振点会向低频率漂移;

2)由于在电源地之间加入了电容、引线及过孔,会带来新的谐振点,在设计中必须充分加以考虑。

| C | ESL | ESR | |

| X7R | 0.1u | 5E-10 | 0.035 |

| 0.01u | 5E-10 | 0.097 | |

| 4700p | 5E-10 | 0.134 | |

| 3300p | 5E-10 | 0.157 | |

| 2200p | 5E-10 | 0.186 | |

| 1000p | 5E-10 | 0.261 | |

| NPO | 1000p | 5E-10 | 0.065 |

| 470p | 5E-10 | 0.09 | |

| 330p | 5E-10 | 0.1 | |

| 220p | 5E-10 | 0.125 | |

| 100p | 5E-10 | 0.175 | |

| 68p | 5E-10 | 0.206 |

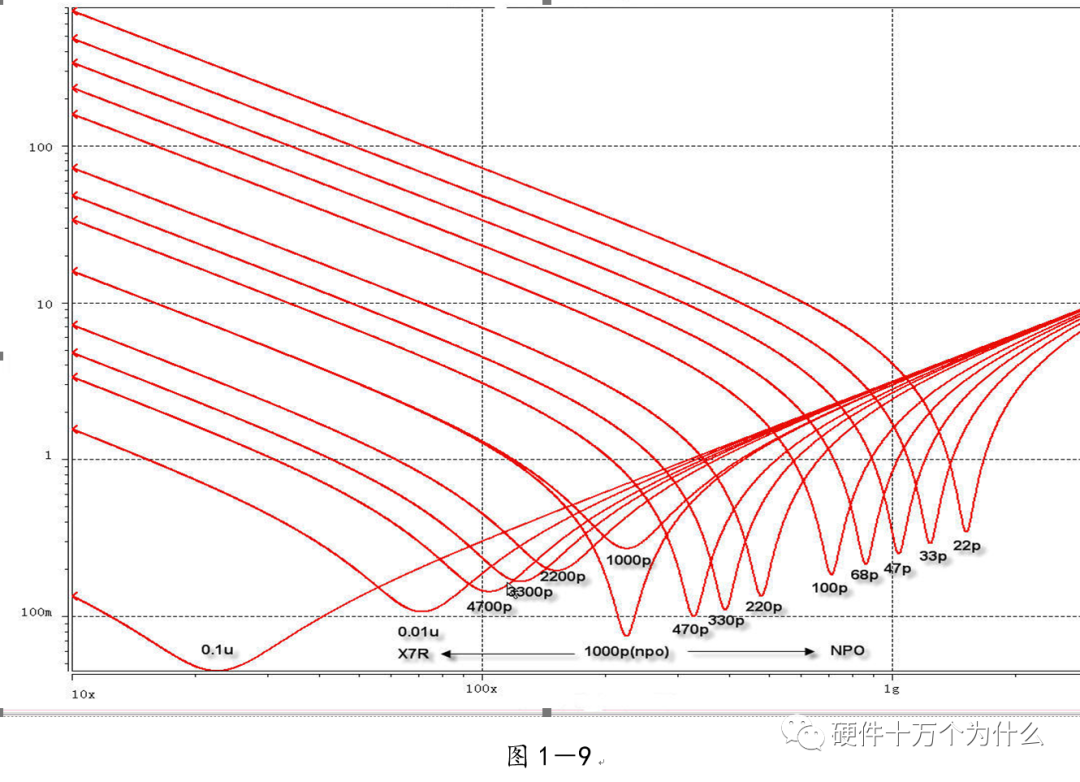

由上表的参数,得到如下的无引线电容的阻抗-频率曲线,如图1-9所示。

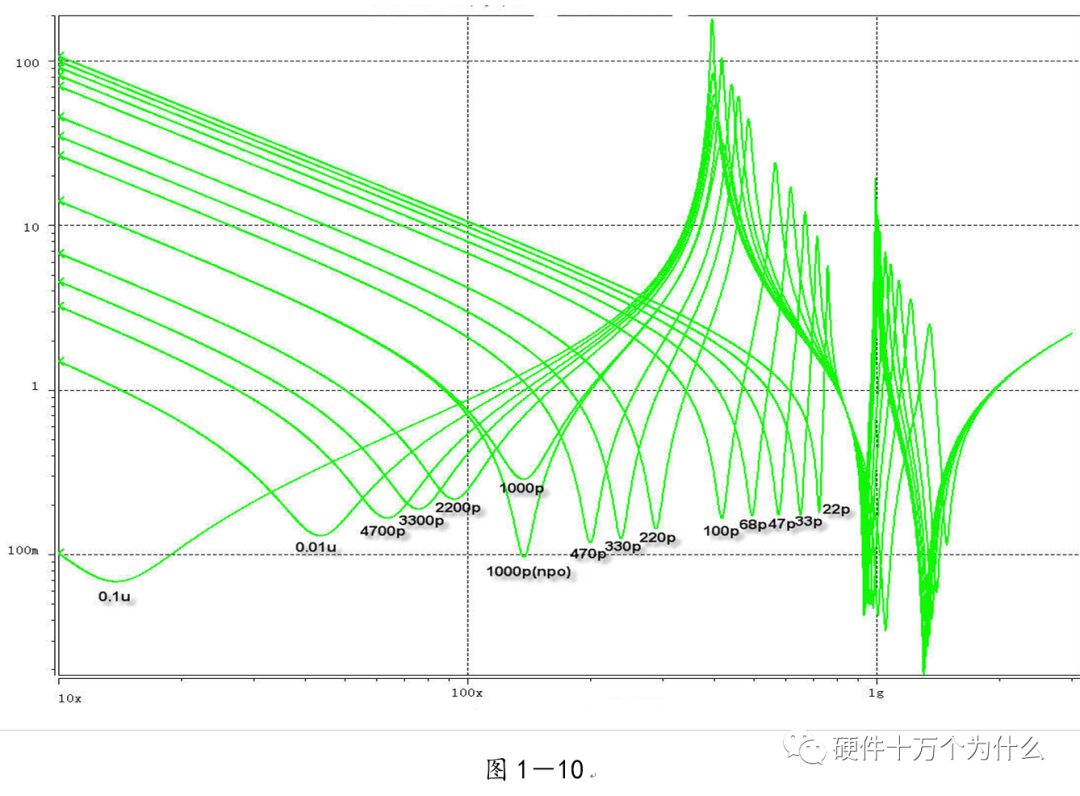

考虑引线与过孔的影响,可以推算出电容加上两端引线和过孔的阻抗-频率响应曲线,如图1-10所示:

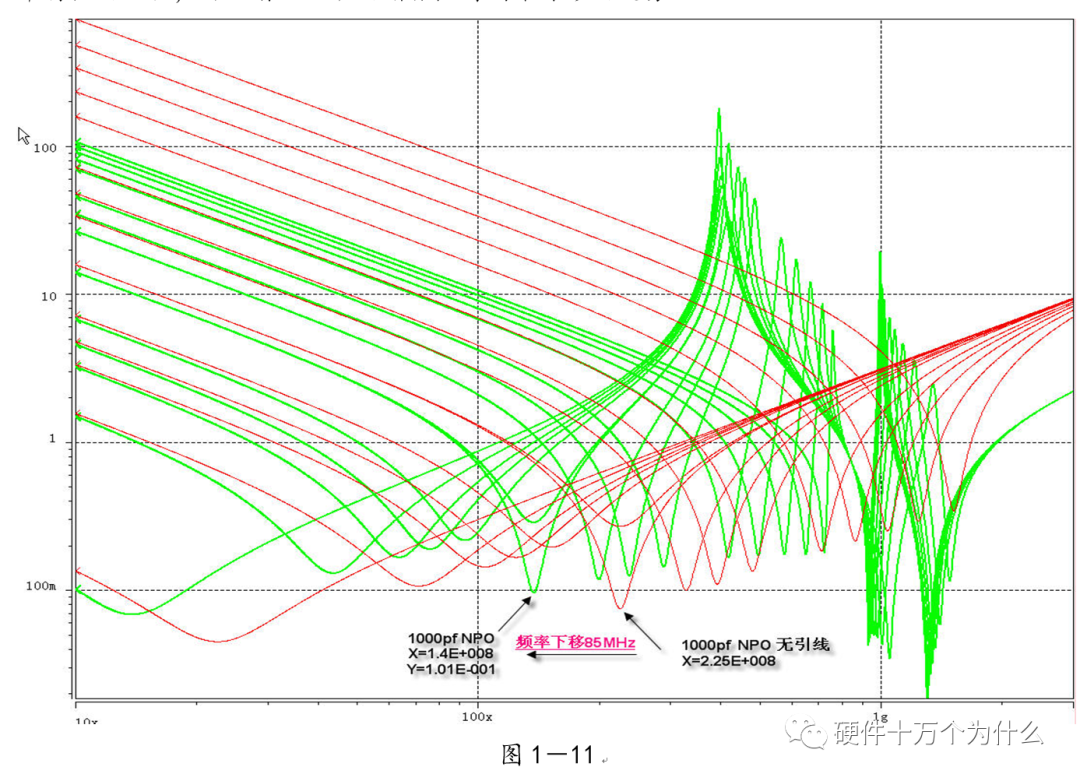

图1-11反映了有引线/过孔的电容(绿色曲线)和无引线/过孔电容(红色曲线)的阻抗-频率特性的比较,可以看出电容的谐振点有向下漂移的趋势。

4、电源完整性分析软件对电容分布参数的计算:

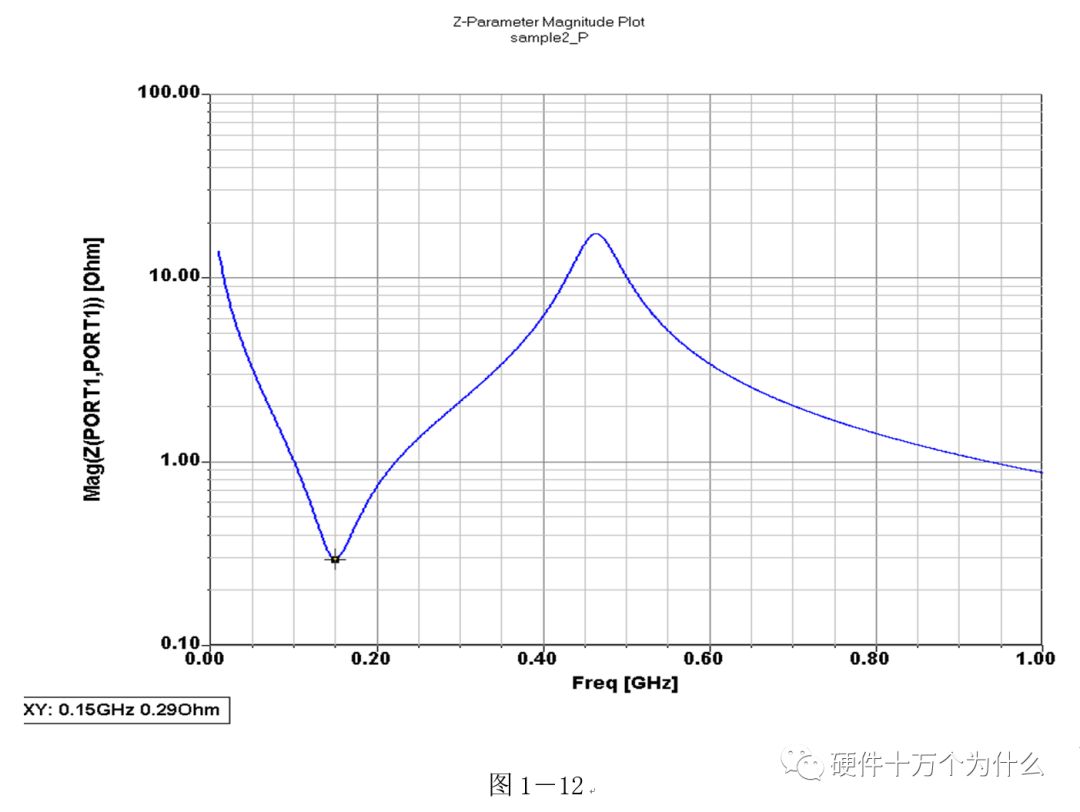

使用SIWAVE也可以分析出电容的引线及过孔的电感对谐振点的影响,将上面的例子转换成siw文件,加入上述参数的电容(NPO 1000pf),设定PORT,得到如图1-12的阻抗-频率曲线。

从图1-12可以看出:SIWAVE计算阻抗时已经考虑了引线及过孔的影响,1000pf电容的谐振点已经由225MHz向下漂移到150MHz左右。

【仿真电容问题总结】

1)电容的建模问题是PI仿真非常重要的一步,电容厂家很多,参数不一致,影响PI仿真结果的准确性。一般国内的电容厂家的ESL/ESR值很难提供,可以借助于仪器测量得到参数;

2)在PCB上完成电容引线时,应该以最小ESL为原则,如:加粗引线,加大过孔等,尽量减小分布电感对谐振点的影响;

3)可以适当采用电容组合;

4)对高频段采用小电容要慎重,以防引线/过孔电感造成实际谐振点的向低漂移与产生新的谐振点(反谐振),高频段应该以改进与优化PCB设计为原则。

电源完整性分析与EMI控制

PCB板上存在有两个主要辐射源。第一是来自顶层和底层的传输线。假设这些线相对应的参考平面是理想的,那么它们的差模辐射是可以根据导线电流计算得到的。对于顶层和底层的传输线,尤其是时钟,应避免1/4波长的走线;第二个源就是边缘辐射。电磁场从激发区域经过电源地平面间传播到边缘,在那里产生辐射。平面上存在的任何过孔、不连续阻抗等,都将转变为电源/地噪声和边缘辐射,因此,边缘辐射直接和电源/地噪声和电源完整性相关。一块具有良好信号完整性的PCB很自然的具有较低的电源/地噪声和较低的边缘辐射。

下面结合高速PCB的SI和设计过程和本人在设计中积累的经验,介绍一些通用的设计规则和值得注意的设计要点:

1、信号的过冲与振铃:

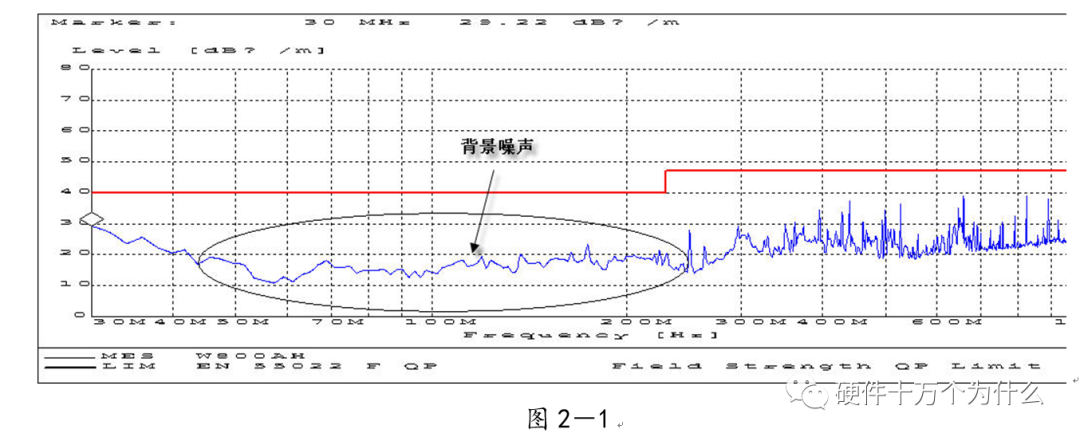

信号质量是我们首要关注的问题,信号的过冲与振铃会带来一系列可靠性问题,在EMI的测试方面,数据/地址等信号线的过冲与振铃是辐射背景噪声的主要贡献者。

解决信号过冲与振铃问题的主要手段是端接,选用适当的拓扑结构等。

在我们进行高速系统级仿真时,往往常常分析的问题是:当CPU通过总线,接插件,板间级连,PCB走线和多个对象通讯时,在不同对象个数、不同信号传输方向的情况下,系统的各个接收端波形会产生很大的差异,采用适当的端接策略可以解决这些SI问题,

下面举例说明:

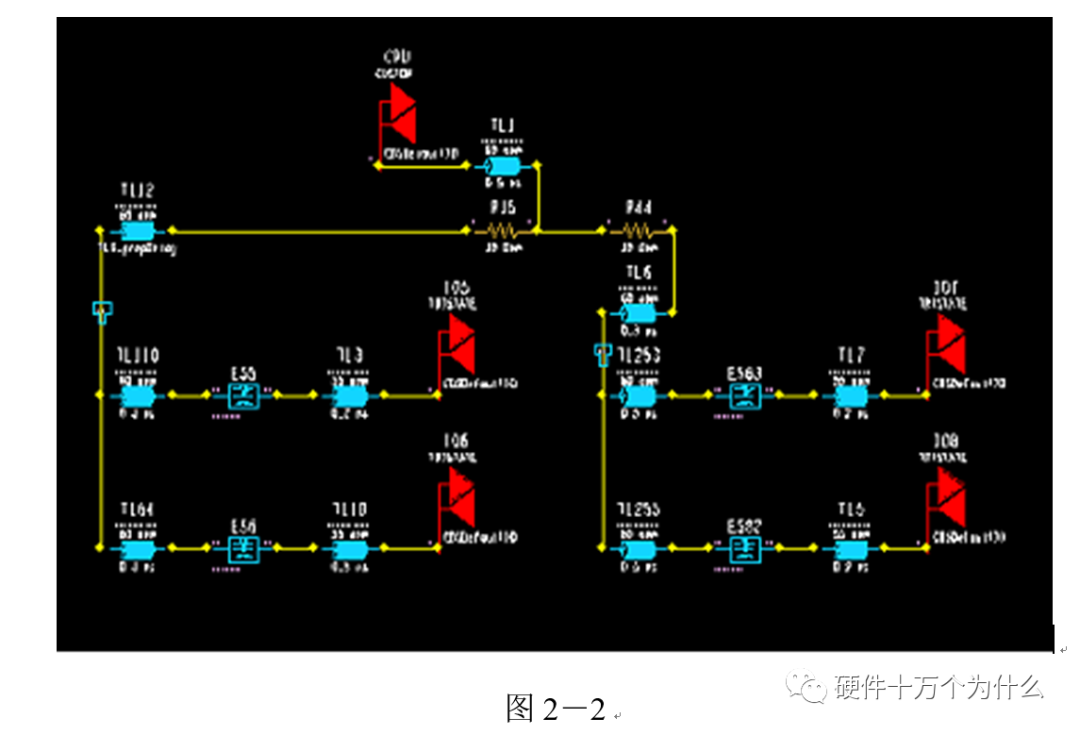

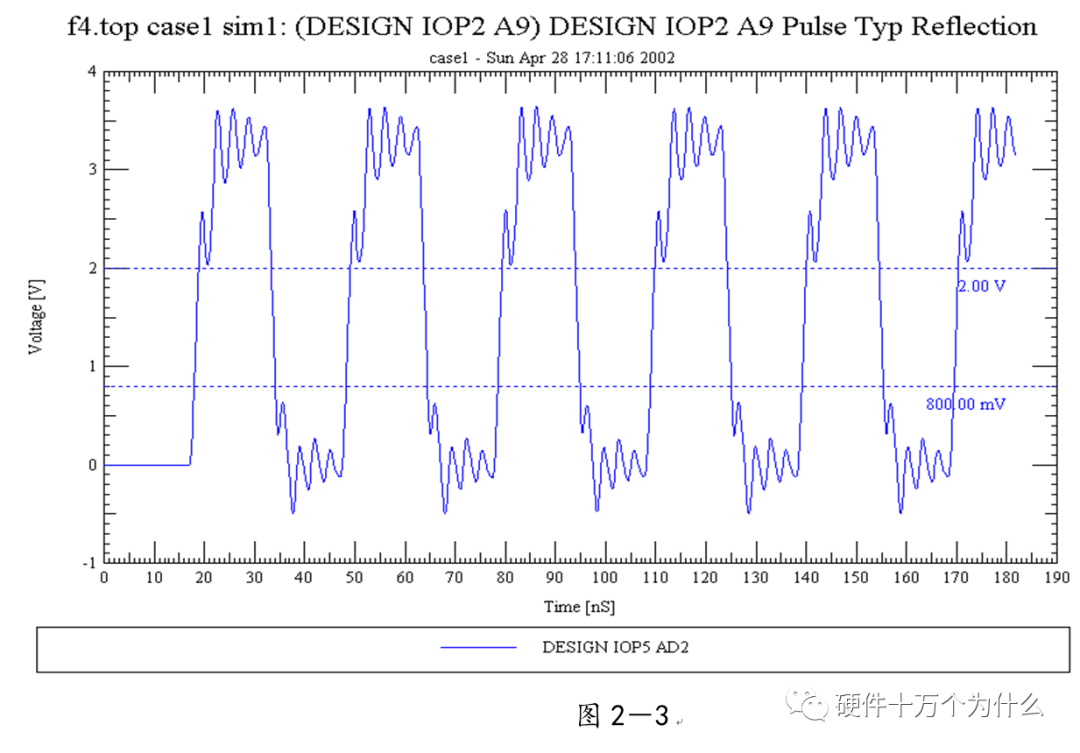

图2-2是一个典型的CPU通过板级互连的点到多点拓扑结构图,在源端已经加匹配电阻端接,以下是CPU发送,IOP5接收,在不同负载的条件下,IOP5的接收波形,图2-3是IOP6不用,其余3个接收端使用的情况下,IOP5的接收波形,可以看出,接收端有明显的过冲。

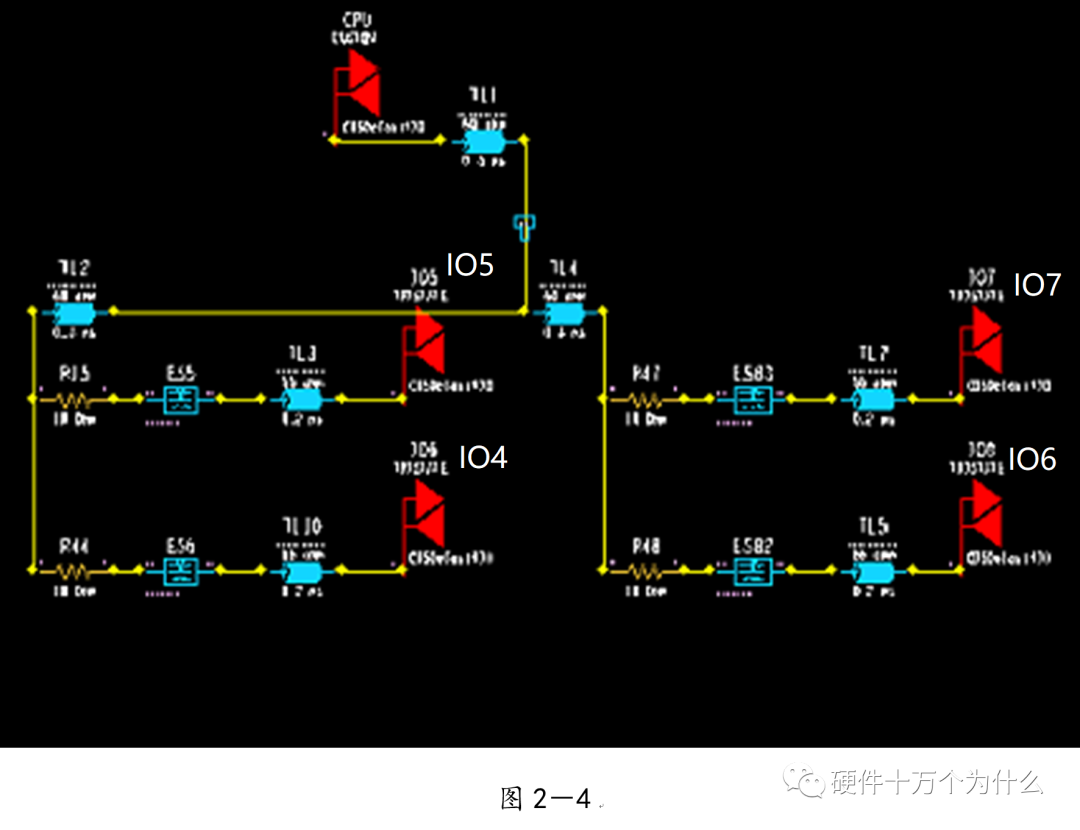

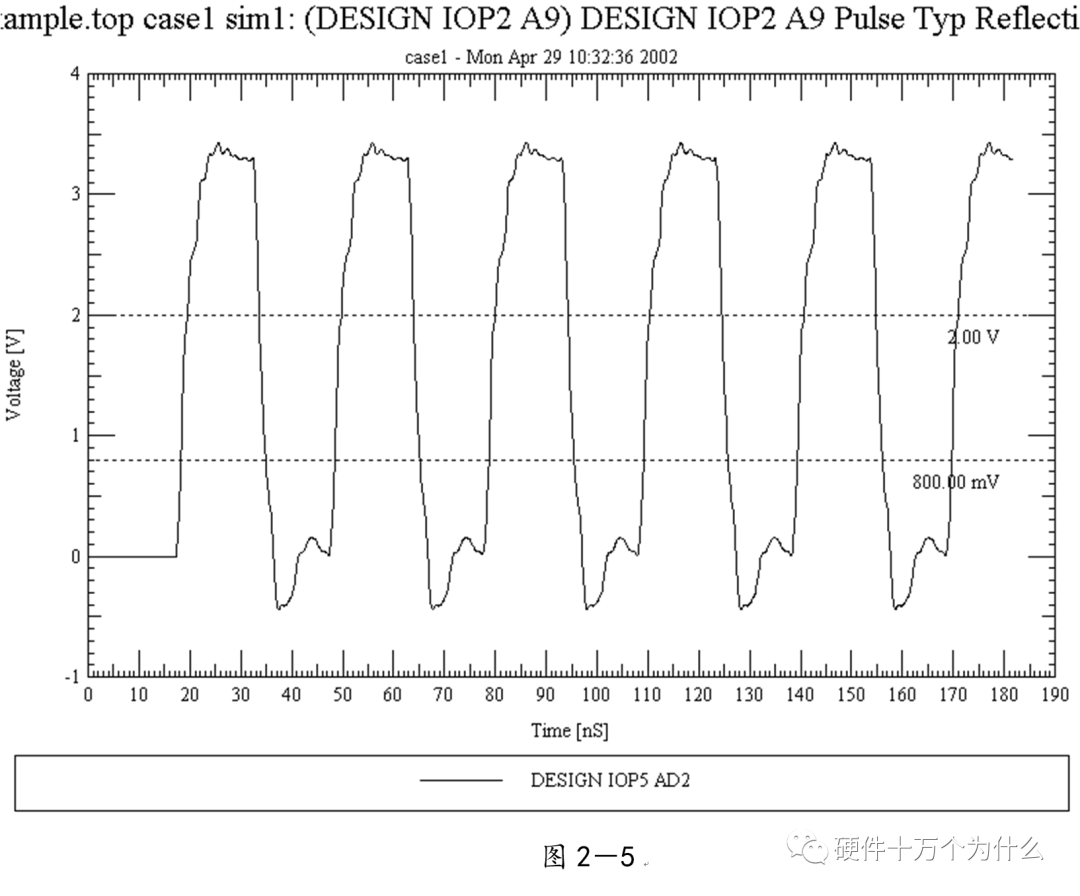

解决的方法有:更改拓扑结构、调整PCB走线的线长,阻抗、更换器件、调整端接方案等。通过改变图2-2的拓扑结构的端接电阻的位置,得到拓扑结构图2-4,我们得到当IOP6不用,其余3个接收端使用的情况下,IOP5的接收波形,见图2-5。

比较图2-3和图2-5可以看出,信号的单调性(monotonic),过冲(Overshoot,undershoot)等方面已经得到了明显的改善,同时,时序的改善也是显而易见的。

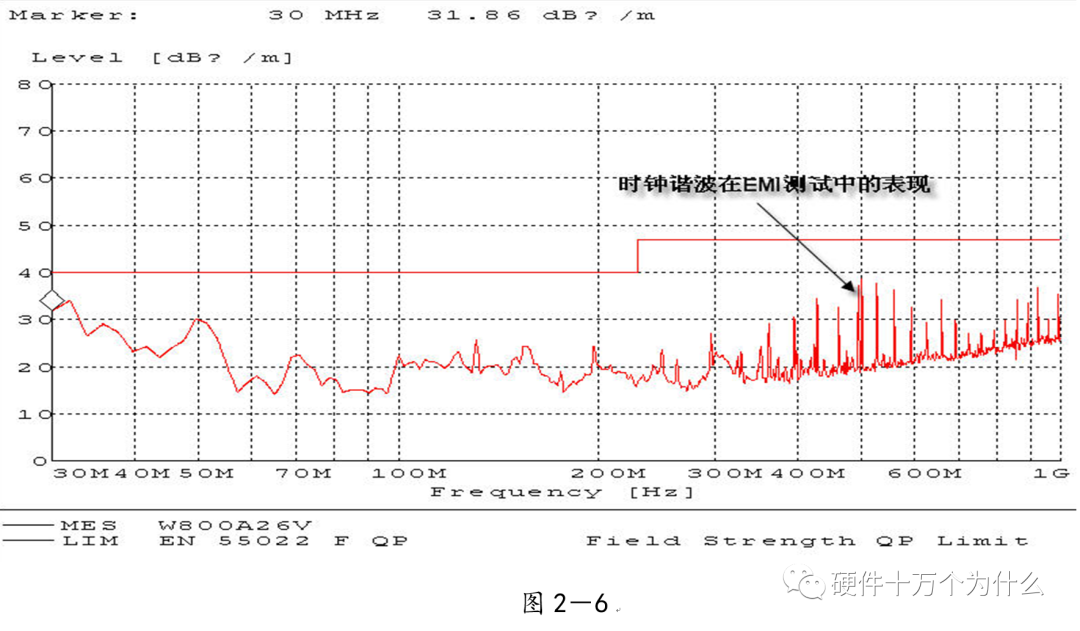

2、时钟电路的处理

时钟电路的设计和EMI问题切切相关,高速PCB的时钟电路的设计必须遵循严格的设计原则保证SI和PI的要求,由于时钟的周期性,在远场表现为离散的频谱,EMI超标的部分往往是时钟或时钟的谐波,时钟对远场EMI的贡献如图2-6所示。

在高速PCB的时钟电路的设计中,建议遵循以下几个设计原则:

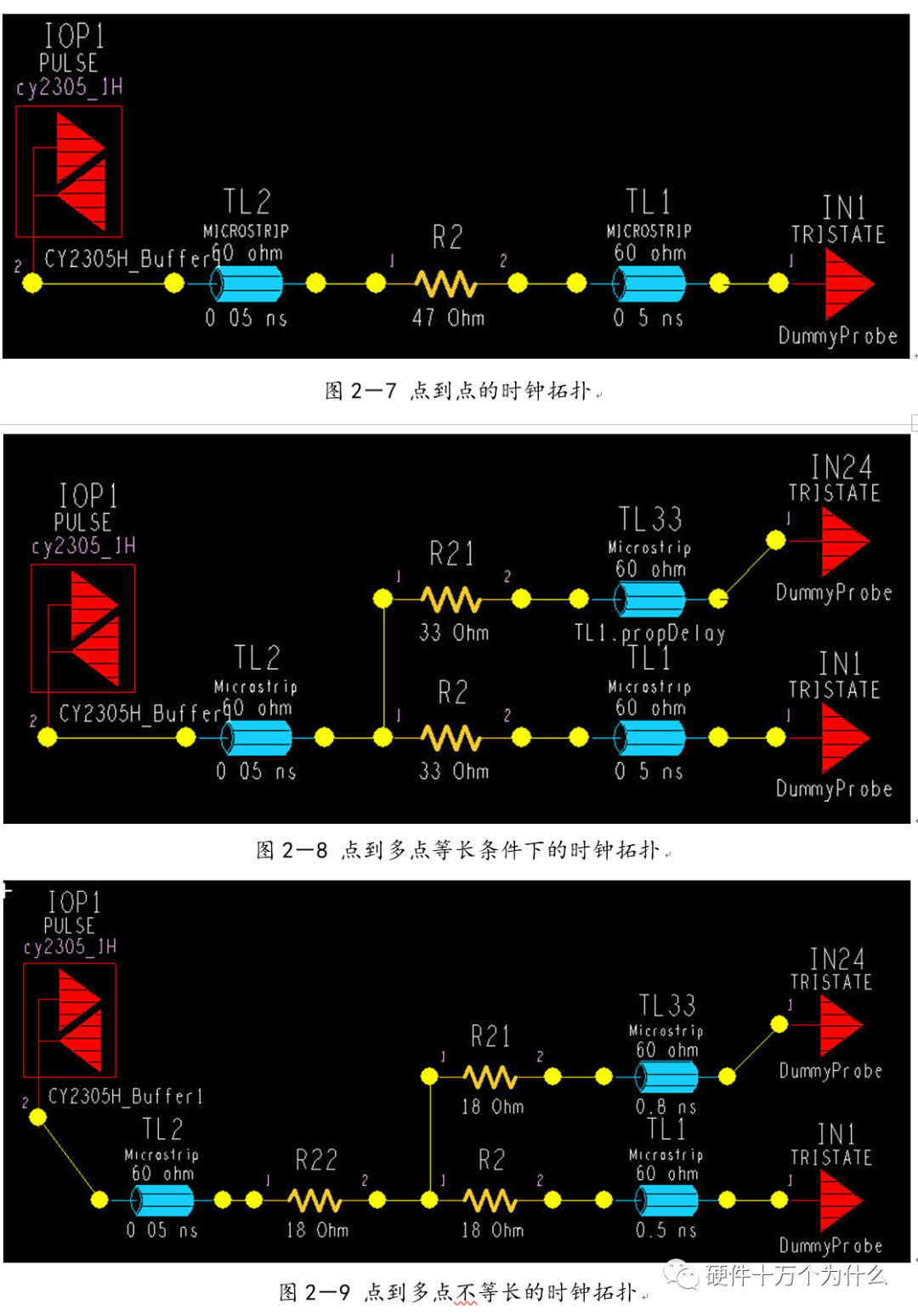

◎在点到点或点到多点的时钟电路设计中要做严格的SI分析确保时钟最小的过冲与最大噪声余量,时钟电路一般采用源端匹配和终端上下拉的方式匹配,如图2-7、图2-8、图2-9,串阻值可以在SQ中用扫描的方法获得,在保证时序空间有较大余量的前提下,可以调整串阻值将延适当变缓以减小EMI。

◎晶振的电源单独供电,通过磁珠加电容滤波电路,将时钟供电电源与VCC在PCB上隔开,如图2-10,供电电源由VCC经过磁珠Z6和电容C252(0.01u)和C253(1000pf)组成独立的电源滤波电路,同样的设计方法可以用于带PLL时钟分配器等电路。

◎时钟线应尽量走线在内层并少打过孔,保证时钟与回流路径的最小面积。

3、合理的叠层设计

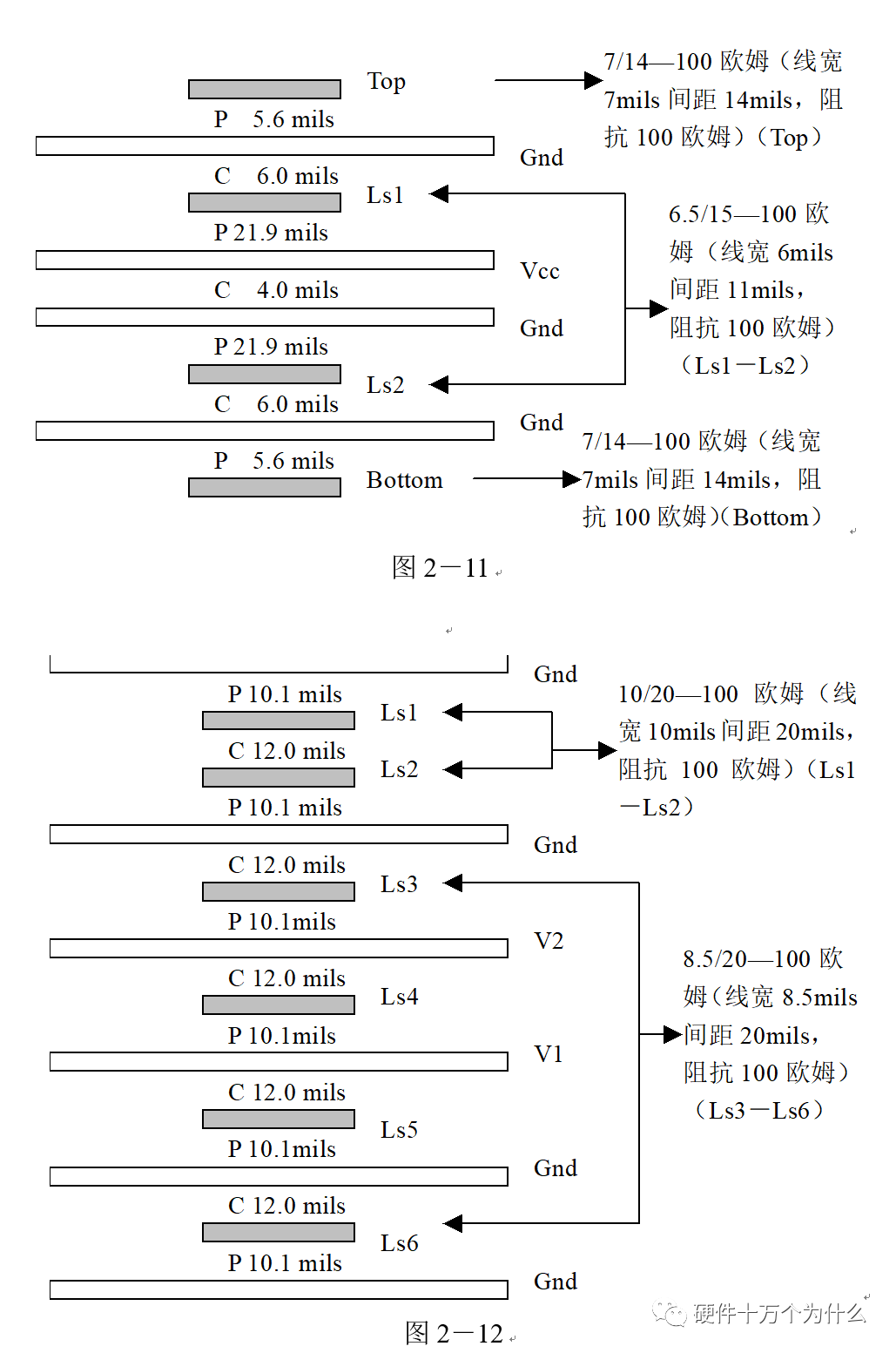

高速PCB的叠层设计在保证电源/地阻抗及EMI控制方面有较大影响,多层板的叠层设计在SI方面的设计指南中重点提及,可以参阅其它SI设计文档,这里举一例说明,如图2-11是一个常用的8层板叠层设计,图2-12是12层背板叠层设计图:

为保证电源完整性的要求,减小高速PCB的EMI,叠层设计一般遵循以下几个设计原则:

◎电源和地平面采用紧耦合,及电源平面紧贴地平面;

◎在线宽可以满足的条件下,信号线尽量与参考平面(一般是地)紧耦合;

◎尽量以地平面为参考平面。

4、控制信号线的回流路径

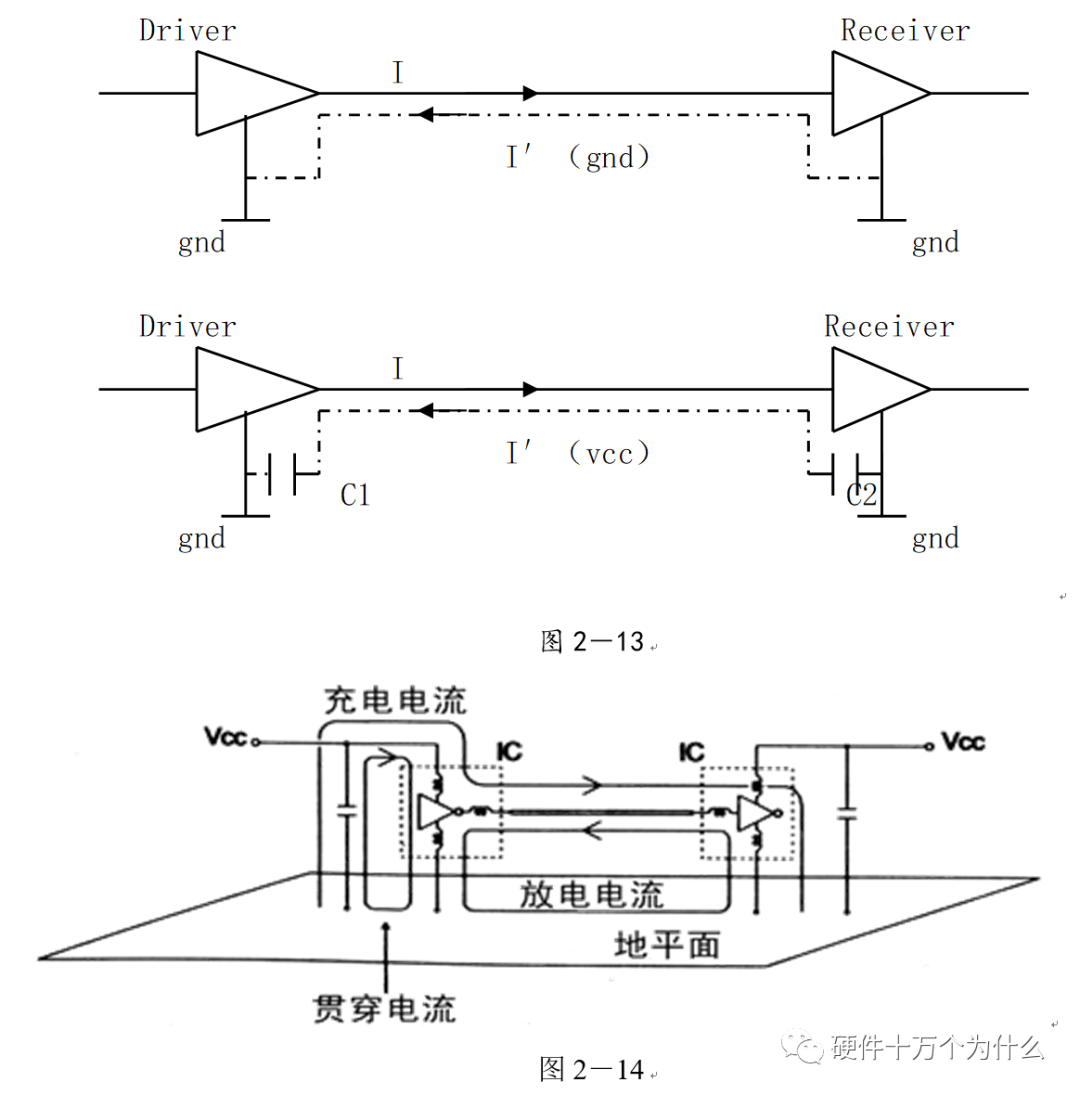

EMI取决于两个谐振回路,一个是“旁路环路”,由IC和旁路电容构成;另一个是“信号环路”,包括信号线在内。根据克希霍夫定律,任何时域信号由源到负载的传输都必须有一个最低阻抗的路径。图中I=I′,大小相等,方向相反。图中I我们称为信号电流,

I′称为映象电流,如果信号电流下方是电源层,此时的映象电流回路是通过电容耦合所达到的。见图2-13。

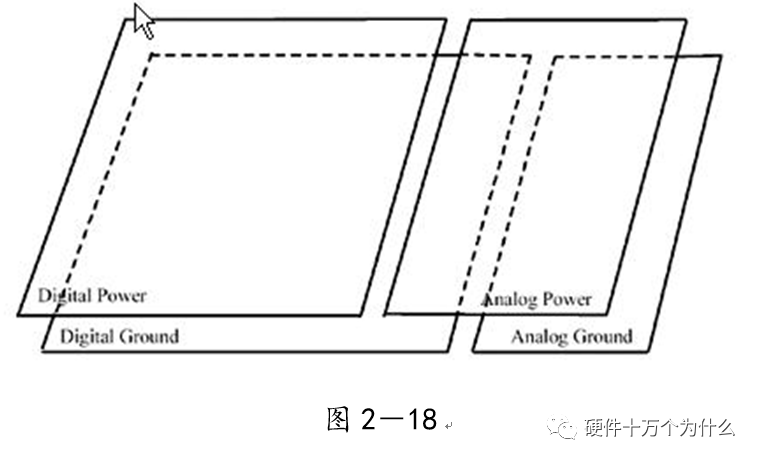

由此,我们得出在多层PCB中应遵循以下基本原则:

◎电源平面紧贴地平面。

◎信号层和参考平面层靠近,保证信号和回流组成的最小面积,重要信号应该以地平面作参考平面。

◎保证电源与地层阻抗最低,电源地的阻抗分析在下面的PI分析中将重点介绍。

◎高速信号线在换层时,会出现过孔等阻抗不连续点,应加地过孔或加旁路电容。

5、采用屏蔽过孔抑制EMI

在高速PCB中,电源地之间的噪声一般通过对外部的连线(如网线)或PCB的边缘辐射,在PCB边缘加上屏蔽过孔对边缘辐射起到阻隔的作用。

6、相邻平面层的交叠处理

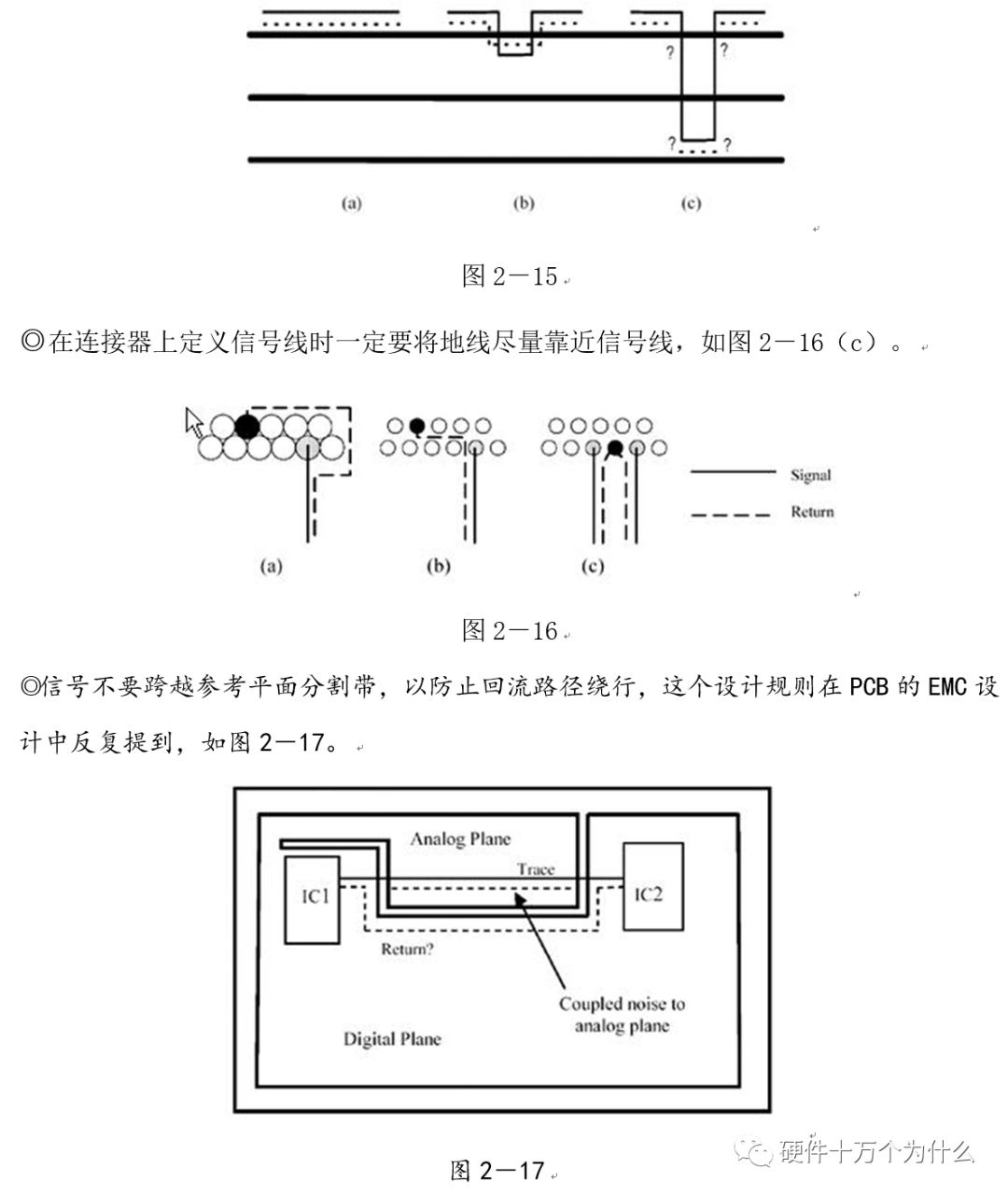

不要将没有联系的平面之间形成交叠,如:模拟电源/模拟地与数字电源/数字地,两者要严格分开,不要在平面上存在容性耦合,如图2-18所示。

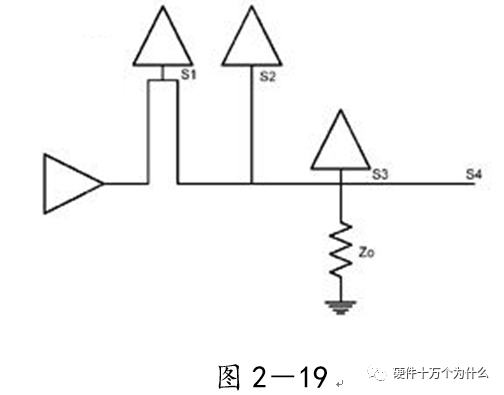

7、信号拓扑中Stub的控制

在高速PCB设计中,尤其要注意尽量减小高速信号的Stub长度,减小“尾巴”的反射,如图2-19中的S3-S4部分。

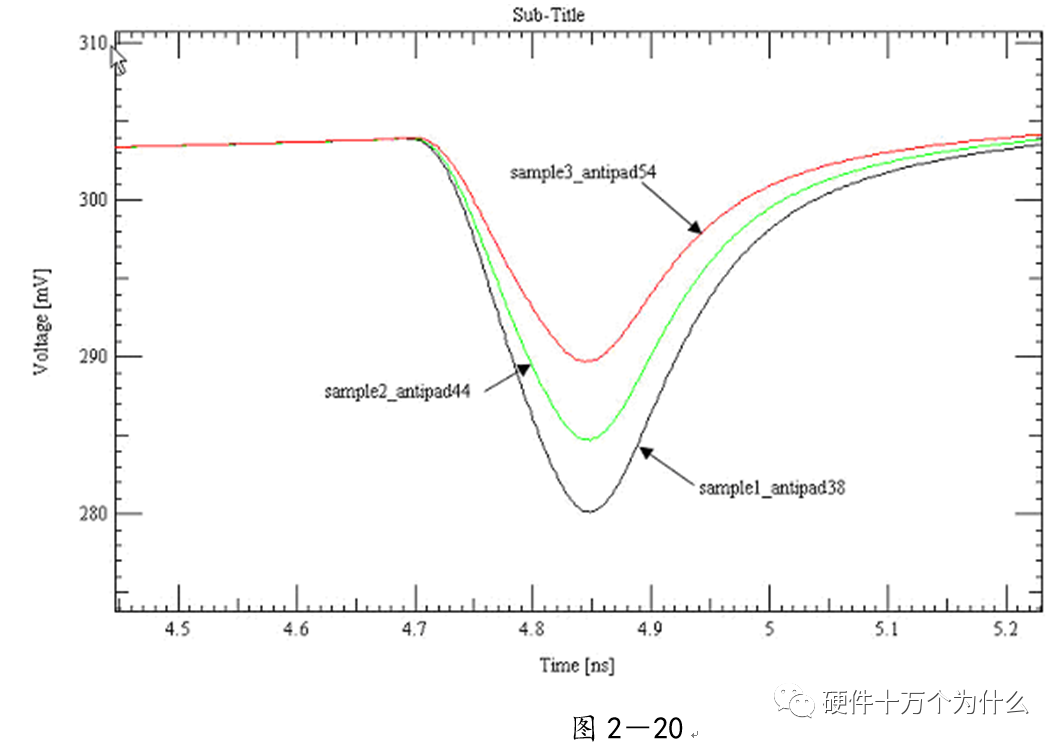

8、高速线过孔的优化问题

这类问题在高速背板设计文档中有详尽介绍,本文以一常用的过孔的实例介绍过孔的反焊盘的优化过程,我们设计了三种过孔结构的样板,过孔为12mil,焊盘为24mil,反焊盘分别为38mil/44mil/54mil,三种反焊盘的尺寸的TDR仿真分析结果对比如图2-20所示。

由此,我们可以得出结论,随着过孔反焊盘的加大,过孔的阻抗不连续的情况会得到改善。

(上例中过孔两端的差分阻抗为100ohm)。

高速PCB的电源完整性仿真要领与实例

高速PCB的SI与PI分析是高速电路设计的重要部分,SI和PI两者是相辅相成的关系,完善的PI设计是保证SI的基础,S-PI设计的成功会带来EMI的改善或者为EMC设计争取更大的设计余量与空间,减少EMC的设计难度,为高速PCB的EMC问题的最终解决奠定基础。

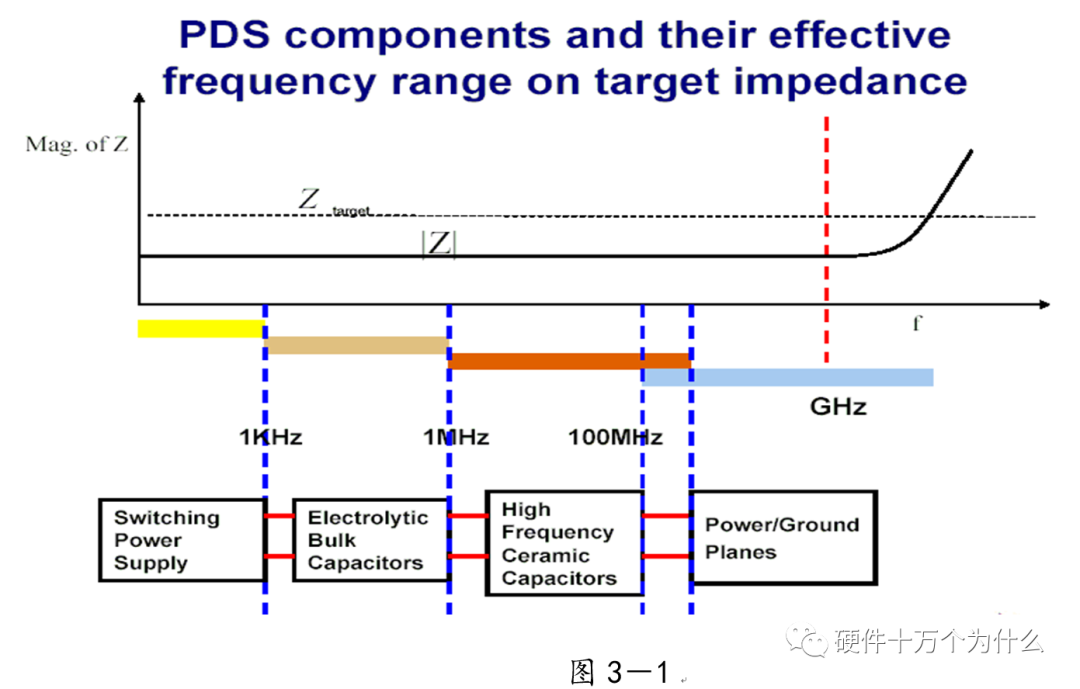

对于电源分布系统(PDS)的设计,在本文中首先关注的对象是:电源/地平面的阻抗,图3-1显示了PCB的PDS设计中不同频率范围,我们选用的电容是不一样的,不同的电容都有自己的适用范围,在1KHz以下,主要控制对象在开关电源;从1KHz到1MHz,我们采用电解电容来完成滤波,从1MHz到100MHz,我们通常选用用高频陶瓷电容;对于高频段,我们关注的对象是电源地平面的设计。高频段是PI设计也是EMI分析的难点,PCB设计显得尤为重要。

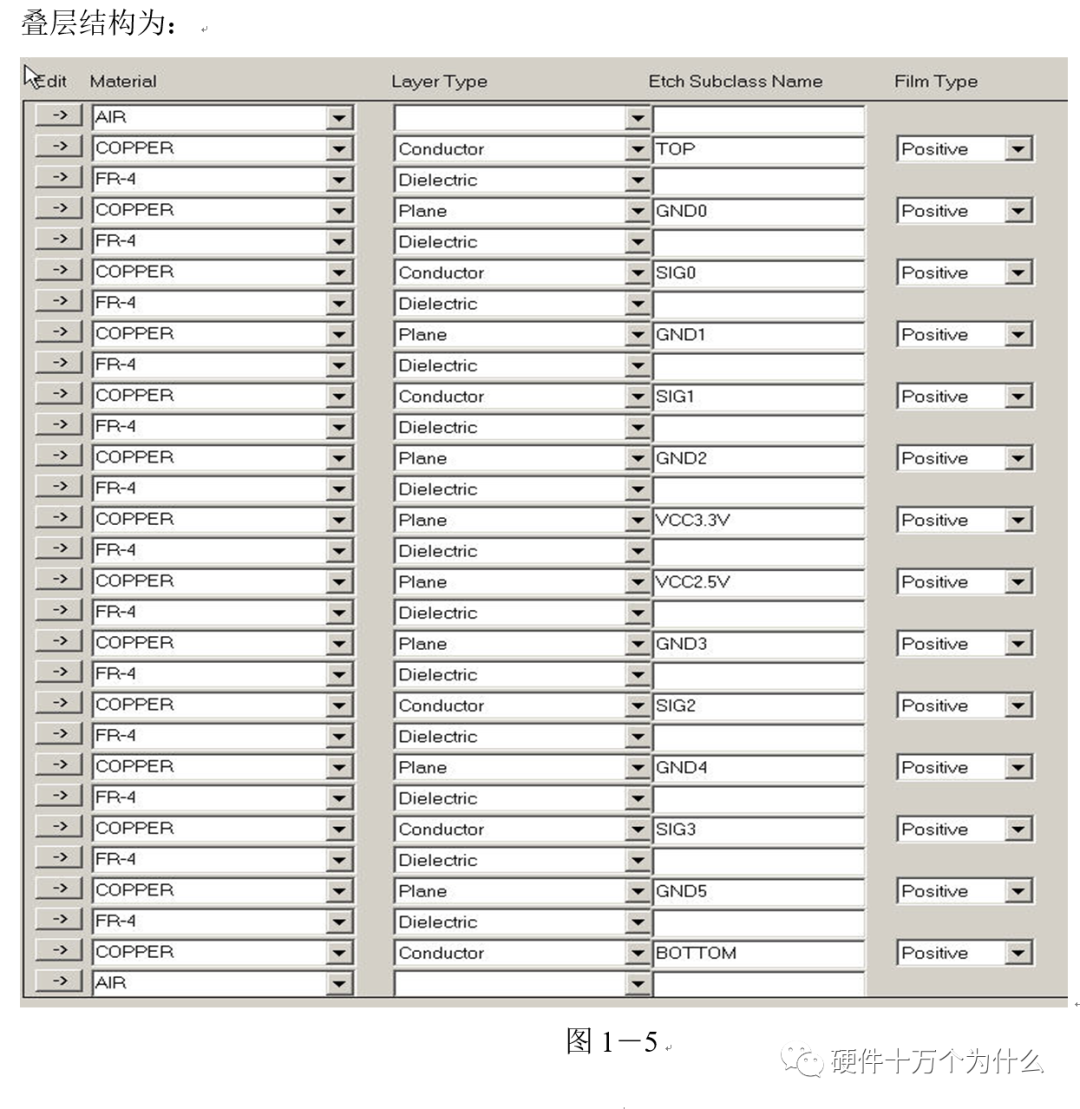

下面介绍一例复杂单板的电源地阻抗分析与控制过程,该单板的叠层结构如图1-5,在仿真过程中为了优化电容的引线方式,减小寄生电感,对该板的叠层结构做了取样分析与计算,得到的电容引线电感的分析数据如第一章所述,以下是电源地阻抗的解决过程:

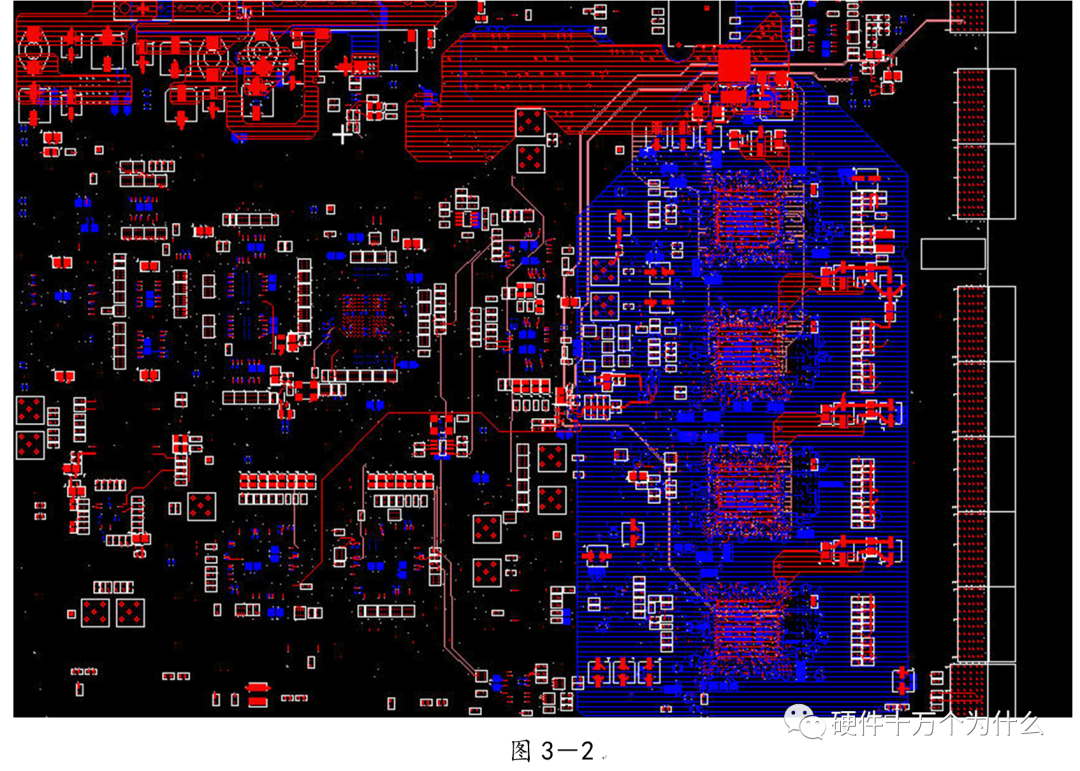

该板的设计难点是VCC1.8V和GND的阻抗,由于VCC1.8V是芯片的核电压,在PCB的局部区域采用,因此,在PCB上没有完整平面,采用在SIG0和BOTTOM铺铜的方法给芯片供电,图3-2的兰色区域是BOTTOM层的VCC1.8V铺铜。

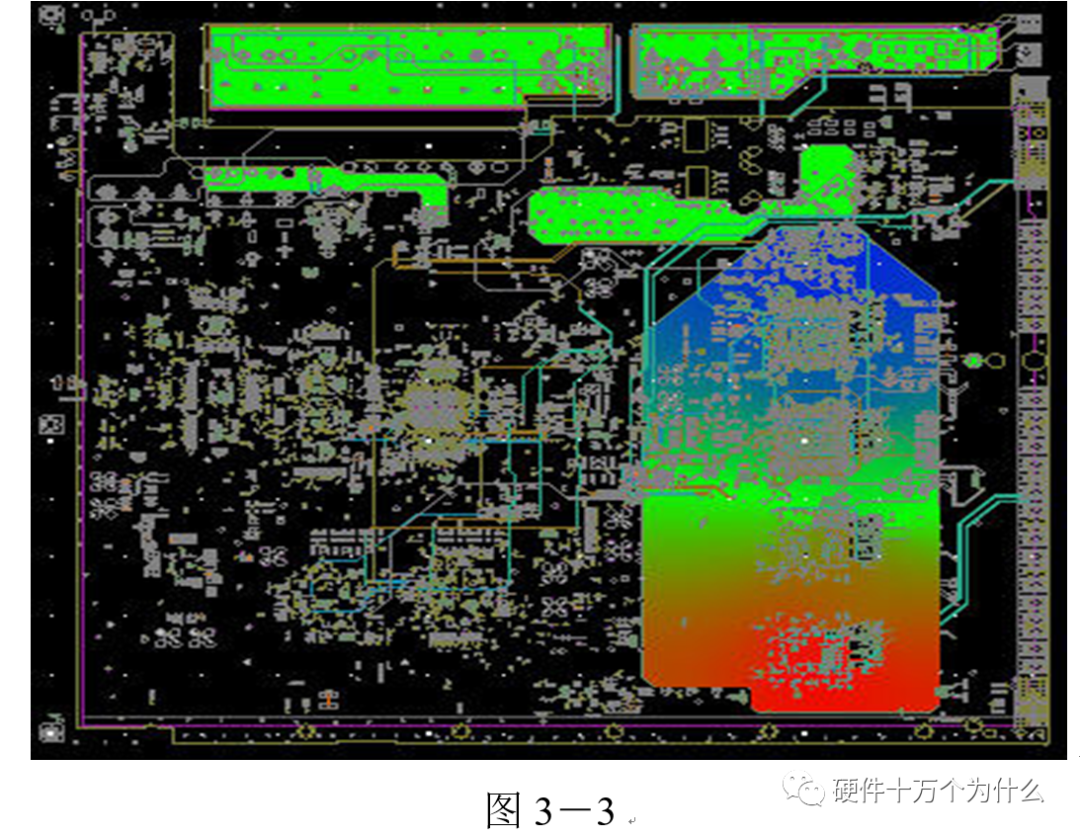

PCB在Resonant模式下VCC1.8/GND的谐振区域如图3-3。

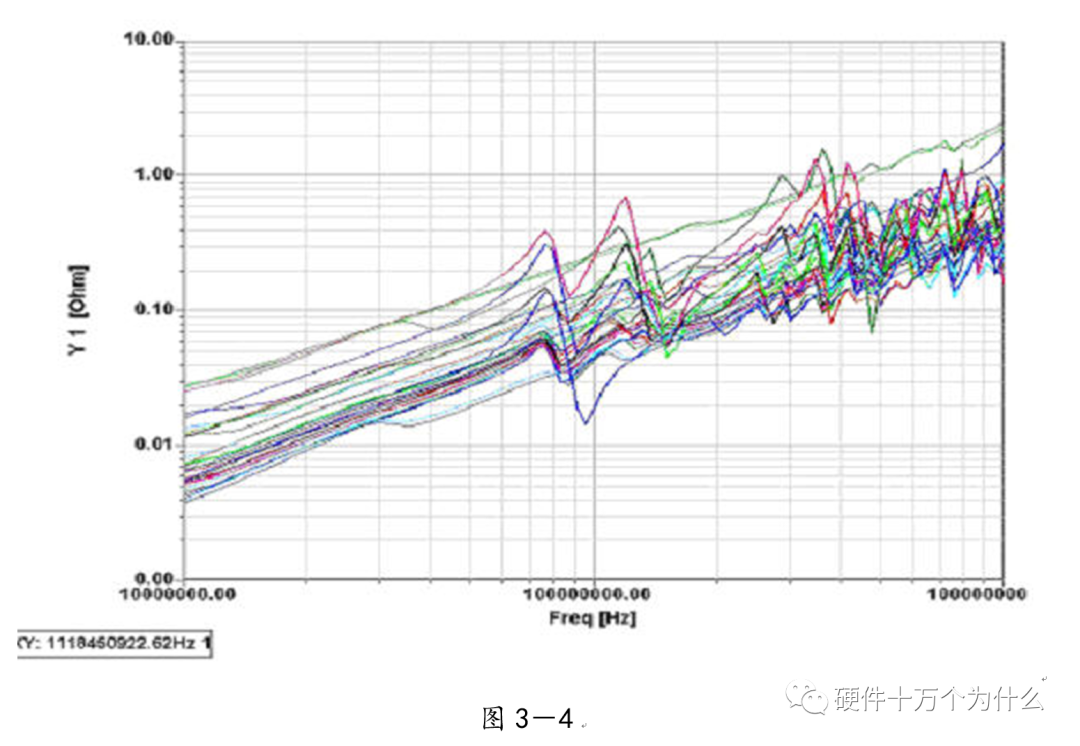

在VCC1.8/GND的各个平面层间定义PORT,得到Z参数曲线如图3-4。

图3-4反映了阻抗在高频段逐步走高的趋势,这是一个较难解决的问题,因为以往的加旁路电容的方法在这里不能完全解决这类问题,为此,我们对PCB作了以下的改进工作:

a)电容Fanout方式的正确选择,详细过程参见图1-7,考虑到公司的工艺要求与实际PCB的密度,选择了第二种引线方式,同时将过孔孔径从12mil调整到16mil,尽量减小过孔电感。

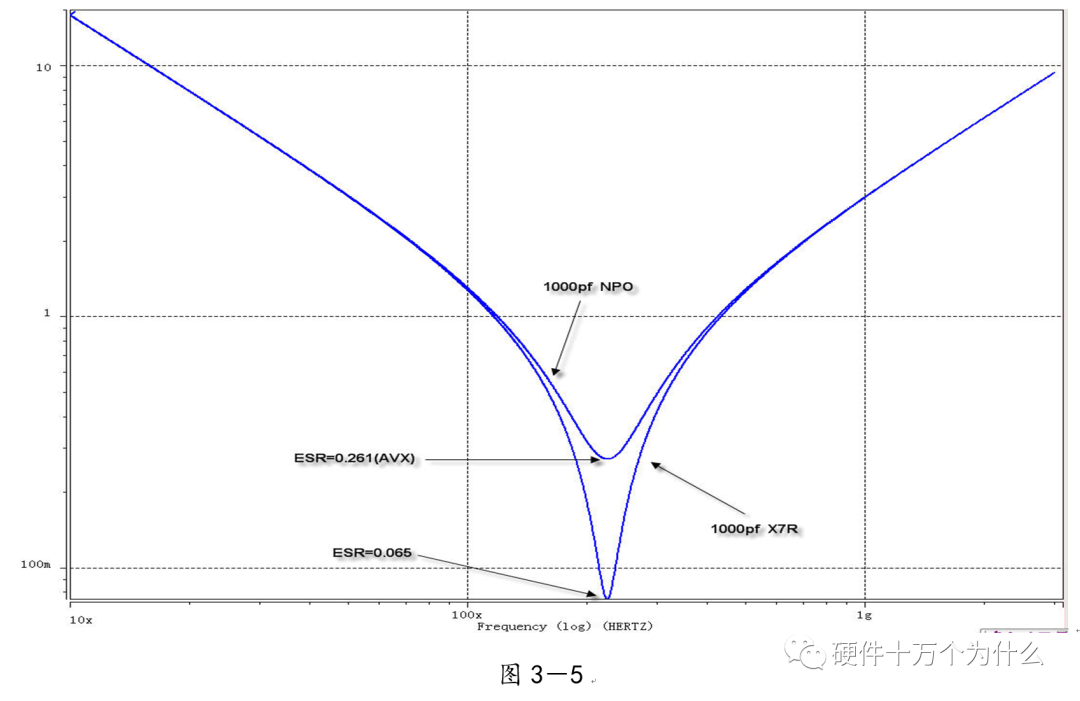

b)适当加一些ESR较低的NPO电容,在本板PI分析中,针对图3-4的Z参数曲线,在IC芯片周围等关键点增加了60个1000pf的NPO电容,NPO和X7R的阻抗曲线比较如图3-5所示(未考虑引线),这两种AVX电容在公司库中均有代码,NPO的ESR值为0.065 ohm;X7R的ESR值为0.261 ohm。

c)改进VCC1.8V平面层形状与结构;

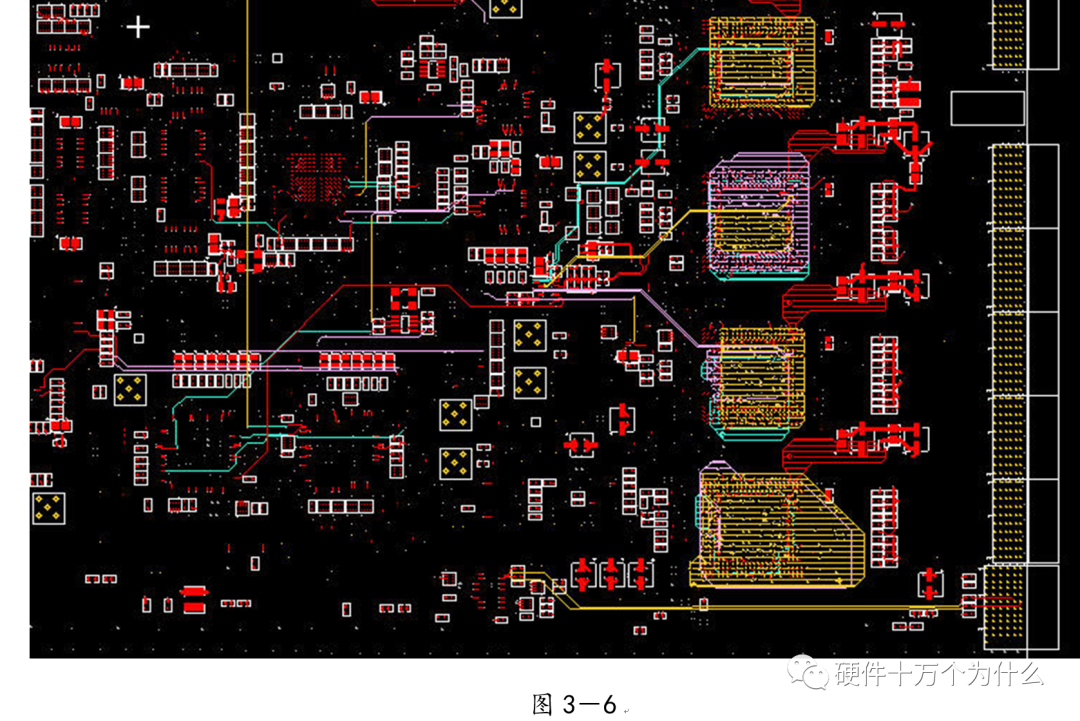

移开BGA下的走线,在其它信号层的BGA下铺铜,由于该设计的特殊情况,VCC1.8V采用在SIG0与BOTTOM两层的铺铜来实现,不如VCC3.3和VCC2.5那样有完整的平面,因此,增加VCC1.8V与GND之间的平面耦合电容也是解决高频段阻抗问题的主要手段,如图3-6所示。

d)在VCC1.8V与GND之间的铺铜层加地过孔,使各个BGA下的VCC1.8V平面层贯通。

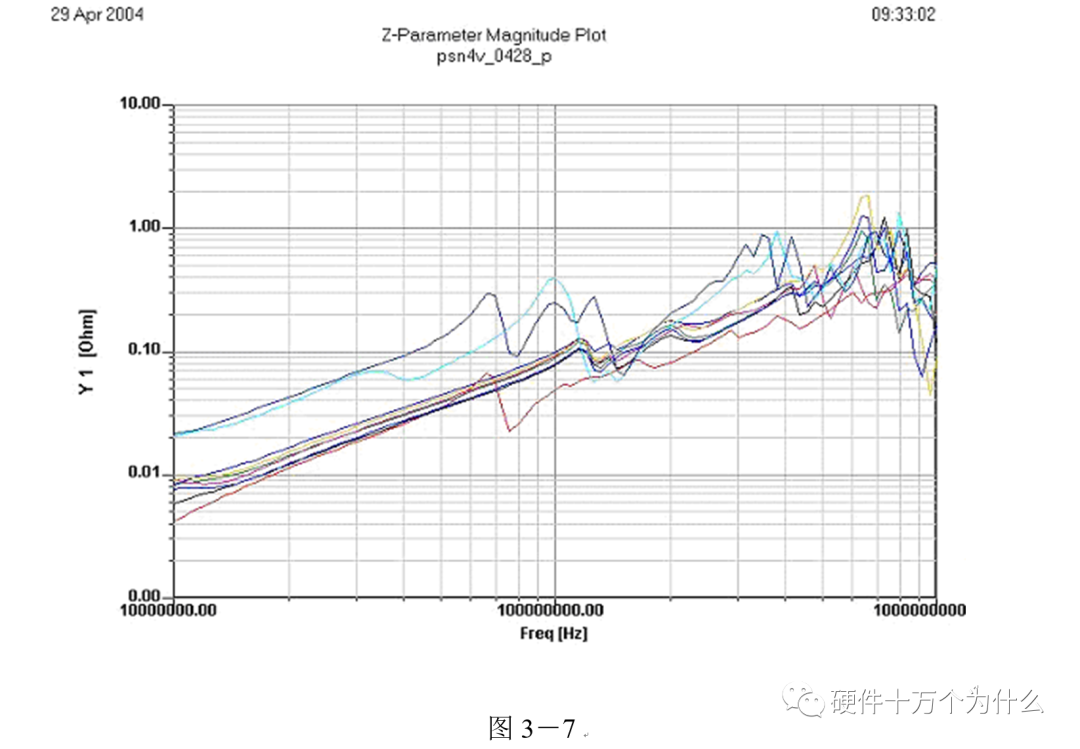

经过以上四步对PCB的改进过程,再将改进后的brd文件重新调入仿真,得到改进后的Z参数曲线如图3-7所示。

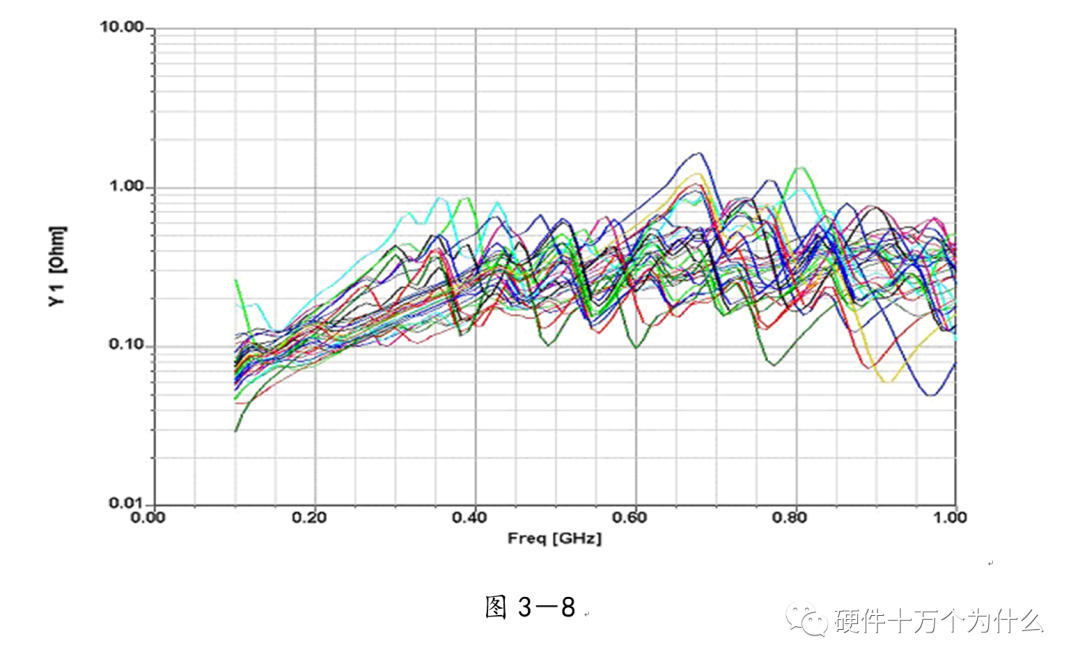

比较图3-4和图3-7可以看出,高频段Z参数曲线的逐步走高的现象得以解决,剩下的问题是解决高频段部分频率点的谐振问题,图3-7高频段Z参数曲线的放大图如图3-8所示。

根据图3-8的阻抗曲线,我们又着手下一步的改进方案:

1、首先检查Brd文件,发现放在BOTTOM层BGA下方的有些旁路电容引线方式(线宽与过孔)还没有按要求调整,另外SIG0和SIG1层4片BGA下方有的铺铜还可以进一步扩大;

2、增加BGA下的地过孔;

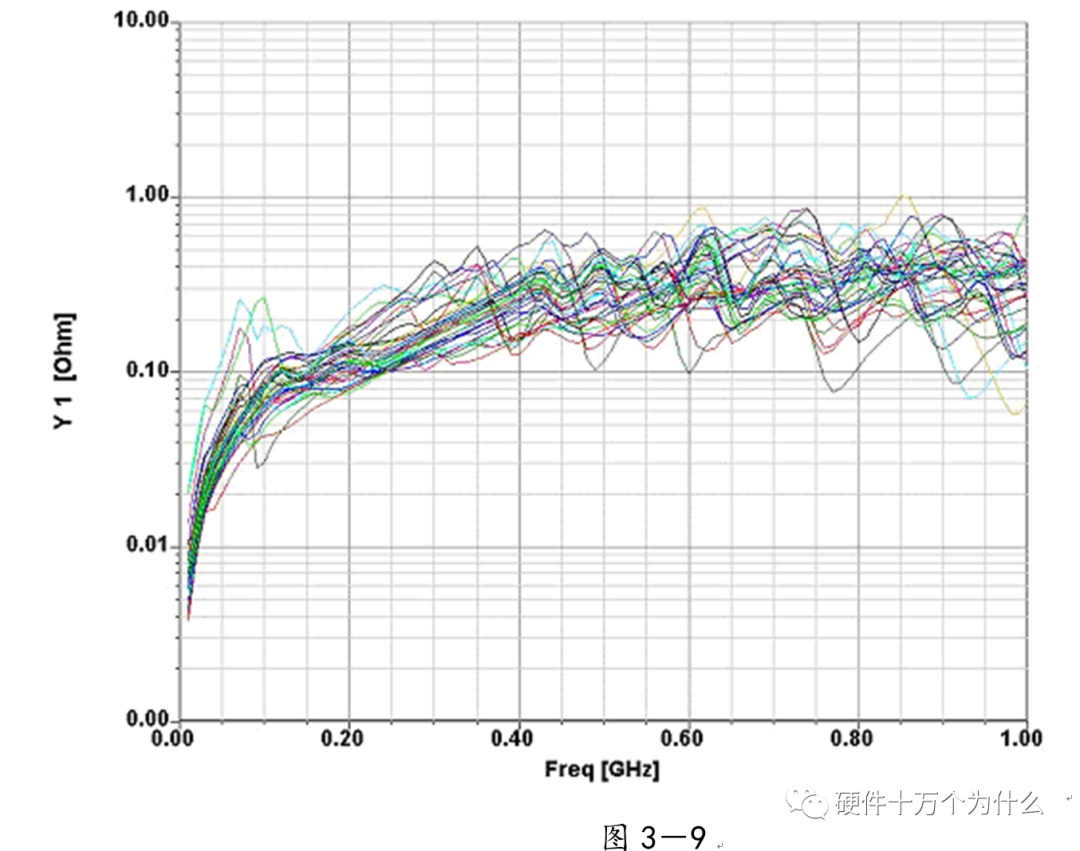

3、由于4片BGA下的空间有限,再增加电容已经不可能,因此采取了更改部分BGA下滤波电容值的办法解决,首先将原先8个0.1u的退耦电容,取出其中3个改为NPO高频旁路电容,注意选用高频段电容时一定要考虑到引线/过孔的影响。通过对BRD文件的进一步改进,得到Z参数曲线如图3-9。

【电源/地阻抗分析问题总结】

1、PCB的电源地阻抗分析是解决电源地噪声的关键所在,也是PI分析很重要的一步,本章节主要通过实例来说明分析过程;

2、电源地平面结构会对阻抗分析结果产生重要影响;

3、电容的引线方式与过孔的选择在高速PCB的电源系统分析中不可忽视,尤其在高频段;

4、由于本文的篇幅有限,对PI仿真的目标阻抗计算,退耦电容的计算、电容的选取、PCB的材料与结构对阻抗的影响等没有作详细介绍,大家可以参阅PI设计的相关文档。

四、结束语

本文主要介绍了高速系统的信号/电源完整性分析及实现方法,集中介绍了电源完整性/信号完整性分析对EMI控制的影响,指出了信号/电源完整性仿真设计和EMC设计的内在联系,介绍了信号完整性分析和电源完整性分析中应当注意的问题,最后以实例说明PI分析中阻抗分析的过程,希望本文对于从事这方面工作的开发人员能有所借鉴。

高速电路的设计设计过程往往是一个不断反复的过程,EMC问题的分析与解决过程涉及到电路设计、EDA设计、可靠性设计等方方面面的内容,PCB设计尤其是高速PCB设计优劣是EMI能否得到控制的重要方面,这一点已经被实践所证明,严格的信号完整性仿真与电源完整性仿真可以帮助我们最终解决EMC问题,器件和单板的EMI控制是从根本上解决问题,可以给系统最大的设计空间,这对于提高系统的稳定性和可靠性起到非常重要的作用。

审核编辑 :李倩

-

电源完整性

+关注

关注

9文章

209浏览量

20741 -

高速系统

+关注

关注

0文章

9浏览量

6764

原文标题:电源完整性仿真与EMC分析[20220617]

文章出处:【微信号:EMC_EMI,微信公众号:电磁兼容EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

电源完整性/信号完整性分析对EMI控制的影响

电源完整性/信号完整性分析对EMI控制的影响

评论