随着数据带宽需求的持续增长,数据传输从并行变成串行,收发器的速率越来越高,无论在单板内或者通过光纤和背板传输,都会带来一系列信号完整性问题。

如何解决这些问题,保证误码率满足协议要求,是一个很有挑战性的工作,主要涉及到从芯片选型、电路设计,到PCB的Layout的全过程。

所以各位老铁们,今天我就给大家介绍FPGA高速收发器中使用什么技术可以帮助我们解决信号完整性问题。

01、高速Serdes信号完整性影响因素

信号在PCB上传输,会遇到两个问题:插入损耗和反射。这两个因素主要影响了高速Serdes在传输过程中的信号完整性。

插入损耗

插入损耗是介质损耗、导体损耗、导体表面粗糙度等原因引起来的。1板材引起的插入损耗

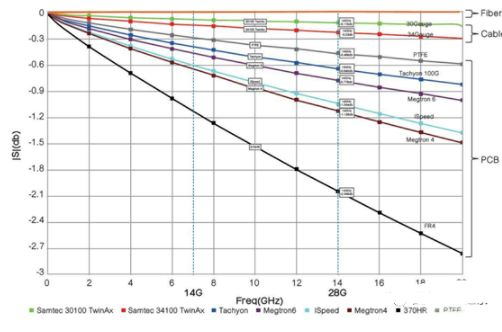

下图中表示不同的介质的插入损耗。我们看到通常用的FR4板材和高速板材M4、M6板材比较起来,插入损耗就比较大。所以我们在设计10G、25G背板传输系统时候,就会选用M4、M6板材。当然选用插入损耗小的材料价格也会比较贵。

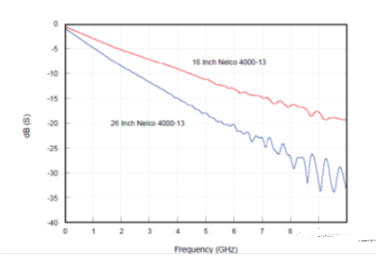

传输距离引起的插入损耗

对于同一种板材来说,传输距离远近不同,插入损耗也不同,见下图。因此我们在布线时候要优先考虑高速线的布线。

反射

反射是因为阻抗不匹配和stub引起的。例如线宽不一样,就会引起阻抗不匹配,信号传输中经过的耦合电容、过孔等都是阻抗不匹配的位置。

Stub是传输路径上短的开路的线。为何会产生stub线,我们举个例子,假设是12层板,我们走线从第1层到第3层,需要打一个过孔。大部分设计中的过孔是一个通孔,加工时候钻头会从第1层打到第12层,信号从第1层走到第3层后会继续沿着通孔走,从第3层到第12层就是一段stub,这就会引起信号反射,造成信号完整性问题。

02、信号完整性问题带来的影响

这些问题对信号有什么影响呢?首先我们知道信号频率越高,影响越大。从第一幅图中可以看出,信号频率越高,插入损耗就越大。

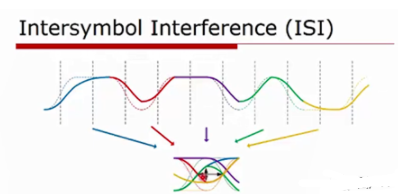

我们的发送数据包含很多频率成分,从低频到高频,经过线路的传输,高频成分被衰减得更多,后果就是引入ISI(码间干扰)的问题。

码间干扰

下图中解释了什么是ISI,信号从发送端经过线路传输到接收端后,因为损耗和反射的原因,不仅信号幅度变小了,而且因为高频成分衰减得更大,信号从陡峭变得平滑。这样造成的后果是前一个bit的波形延伸到了后一个bit位置。在发送侧我们发送的bit是0-1-1-0,经过传输后最后一个1的波形延伸到后面一个0的位置,会造成0的电压变高,判决时候可能判决成1,这样本来发送的0-1-1-0,在接收端判决成0-1-1-1。这就是码间干扰。码间干扰的主要原因就是高频成分损耗大,低频成分损耗小。

如何保证数据的传输可靠

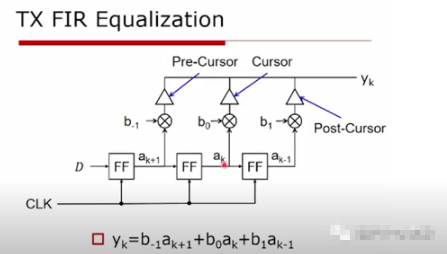

如何克服这些问题保证数据的可靠传输呢?我们在发送端引入去加重技术和接收端引入均衡技术。1去加重技术

首先介绍去加重技术,下图为高速收发器发送端的去加重电路。

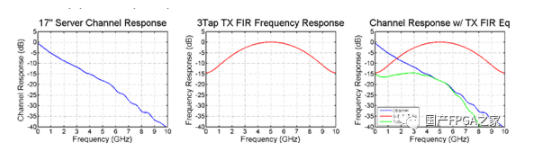

电路很简单,串行数据经过寄存器延迟后乘以不同的系数,然后合并在一起发送出去。频率响应如下图TX FIR Frequency Response所示,最后接收端的频率响应如如下图Channel Response所示,从直流到奈奎斯特频率是一个相对平坦的响应。

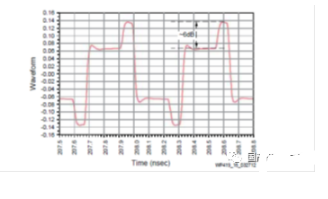

我们从时域上看一下去加重对波形的影响,看上去波形更奇怪一些,所以去加重有些像无线通讯中的一个术语“预失真”。

pre emphasis 时域波形

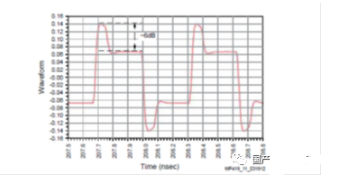

post emphasis 时域波形

我们可以看到pre和post处理的位置不同。pre是在信号变化前处理,post是在信号变化后处理。

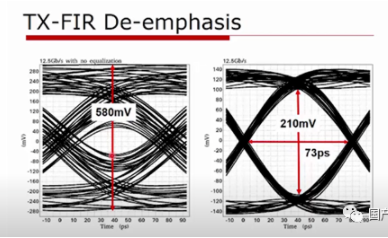

最后我们看一下经过和不经过去加重以后的眼图,下图左边是没有经过去加重的接收眼图,右边是经过去加重的接收眼图。我们可以看到,右边的图尽管电压变小了,但是波形变的陡峭了,就不会引起下一个bit判决错误。因此通过在发送端使用去加重技术,可以抵消线路带来的损耗。

在发送端使用去加重技术,在接收端我们还可以采用CTLE和DFE均衡技术。

-

FPGA

+关注

关注

1629文章

21744浏览量

603595 -

信号完整性

+关注

关注

68文章

1408浏览量

95496

发布评论请先 登录

相关推荐

FPGA高速收发器如何解决信号完整性问题

FPGA高速收发器如何解决信号完整性问题

评论