高速Serdes均衡技术介绍

FPGA高速收发器的接收通道上有2种均衡模式:CTLE(连续时间线性均衡)和DFE(判决反馈均衡)。1连续时间线性均衡

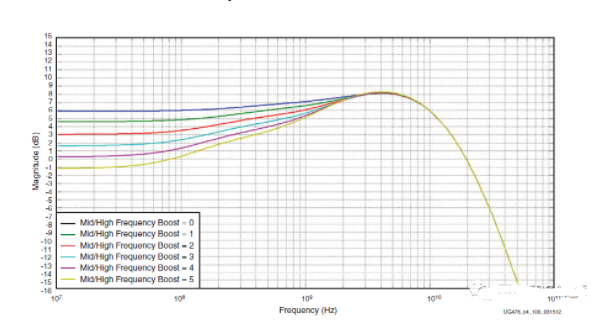

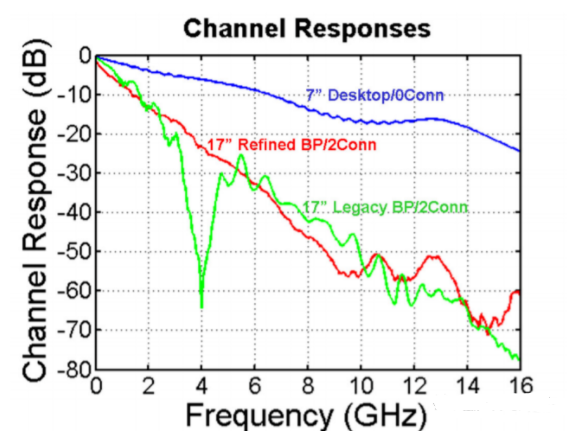

CTLE(连续时间线性均衡)是一种应用于接收的线性滤波器,可衰减低频信号分量,放大奈奎斯特频率附近的分量,并衰减更高频率,这样就抵消了通道的低通特性。如下图所示,可以调整 CTLE 增益以优化低频衰减与高频放大的比率。CTLE的缺点是放大高频分量的同时噪声和串扰也被放大。和上一篇提到的发送预加重一样,两者都通过反转通道的低通特性来解决通道损耗的问题,所以它们的功能其实很相似。在GT wizard中选择LPM 模式就是使用CTLE模式,FPGA里面的CTLE参数已经是自动调整了,不需要我们去设置。CTLE模式的功耗比DFE模式小10%-15%,在通道损耗小于12db时候建议使用LPM模式。板内互联情况下通道衰减基本上都小于12db,使用LPM模式是一个比较好的的选择。

2判决反馈均衡

DFE(判决反馈均衡)是一种非线性均衡器,在上一篇文章里面我们提到发送数据在经过有损通道后,高频成分被衰减,带来的影响是前一个bit数据污染了后来一个数据,引起了ISI(码间干扰)。

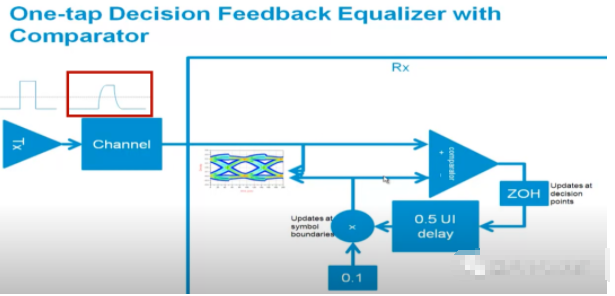

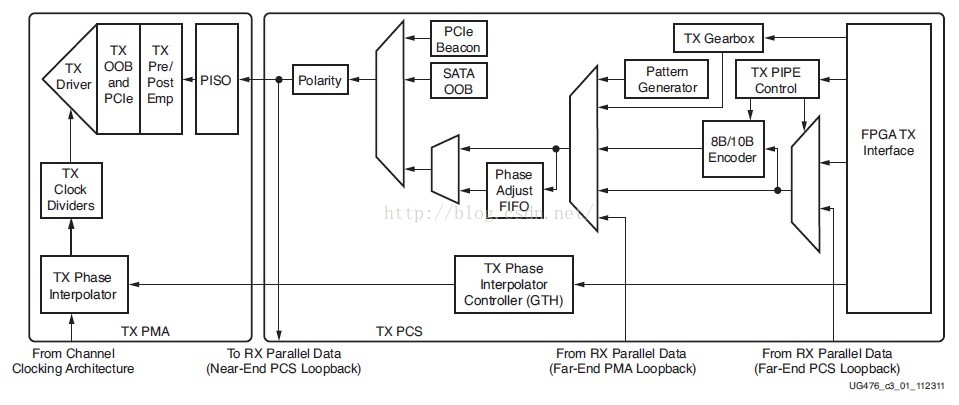

DFE的解决思路是:如果我们知道前一个bit对后面几个bit的影响有多大,在收到后面bit的时候把前面bit的影响去除,那就得到了干净的数据。下图中Rx框图内是DFE模块的结构。

这个是1个tap的判决反馈均衡器,Tx发送的数据是0-1-0, 经过有损通道后因为ISI的影响,我们可以看到图中红圈接收的0-1-0 波形有些畸变。我们假设前一个数据对后面的数据影响因素是10%。

DFE 模块中的slicer切片器就是一个采样保持器。串行数据经过CDR后恢复出时钟,时钟会在数据的中心位置采样数据。采样数据1经过延迟0.5个符号周期(UI)后,把采样数据1乘0.1也就是衰减10%,在后续接收到数据0时候减去衰减10%的前一个接收数据1,这样我们就消除了前面的数据1对后面数据0的影响。这就是判决-反馈的含义。

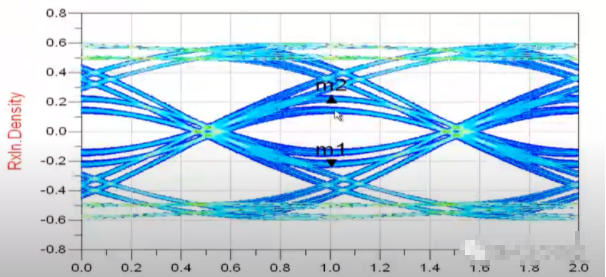

我们可能有些疑问为何延迟不是1个符号周期,而是0.5个符号周期?下图是不使用DFE均衡,我们看到接收的眼图比较小。

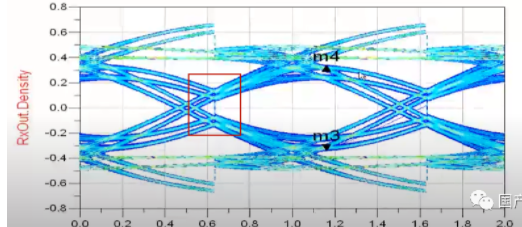

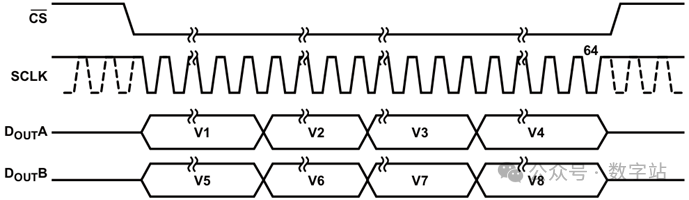

下图是使用DFE均衡后,眼图张开的比上图要大,我们注意红圈位置是数据的变化沿,DFE延迟0.5个UI,因此在下一个数据的变化沿处就开始减去前一个bit带来的影响,而不是只在数据的采样位置才起作用,这样的效果是整个的眼图都变大了,所以DFE的眼图看起来有不连续性。

3DFE特点介绍

DFE的优点:

1)DFE和CTLE相比不会放大噪声和串扰,数据经过衰减很大的通道后接收的数据信号幅度已经很小了,这个时候高频的噪声和串扰对信号影响就会很大。

2)在高速收发器通过背板连接的应用中,因为过孔和连接器阻抗不匹配引起反射,通道的衰减就像图中浅绿的线,在某些频率点衰减很大。在这种情况下CTLE的效果就比较差,DFE的效果就会比较好。

DFE的缺点:

1)设计DFE比CTLE难度大,这个是芯片设计的事情,我们不需要关心。

2)目前DFE的参数在FPGA中都是算法自动调整,不需要我们去设置,但是我们能看出DFE有一个错误传播的特点,如果前面一个bit判断错误,DFE算法会在后面几个bit中起到负面作用。在使用8B10B编码的协议而且数据没有加扰的情况下,如果线路上长时间发送固定码型会使得DFE自动调整算法漂移,引起负面效果。因此在8B/10B编码而且数据没有加扰的协议里面是不建议使用DFE的。我们都知道更高速的协议使用的都是64B/66B或者128B/130B编码,这种编码下数据都是加扰的。而且速率高通道衰减也大,所以DFE一般用在这种场合。

-

FPGA

+关注

关注

1634文章

21830浏览量

607988 -

收发器

+关注

关注

10文章

3524浏览量

106442 -

滤波器

+关注

关注

161文章

7919浏览量

179499

发布评论请先 登录

相关推荐

FPGA高速收发器的GTX发送端解析

FPGA设计之GTP、GTX、GTH以及GTZ四种串行高速收发器

求助FPGA高速串行收发器,输出12.5Gbps的信号要用什么电平 ...

视频: Artix-7 FPGA:如何在大批量应用中使用高速SerDes

FPGA高速收发器设计要遵循哪些原则?

高速ADC与高速串行收发器

Logos系列FPGA高速串行收发器(HSST)用户指南

FPGA高速收发器的高速Serdes均衡技术

FPGA高速收发器的高速Serdes均衡技术

评论