摘要

在先进的p型金属氧化物半导体场效应晶体管中,SiGe沟道可用于提高空穴迁移率和定制阈值电压偏移。在这种器件的源极/漏极区中SiGe:B的低温选择性外延生长(SEG)之前,SiGe氧化物的有效去除是强制性的。SEG之前的H2烘烤通常在低于650°C的温度下进行,以避免孤岛效应或形状变化,要求事先非常有效地去除表面污染物(如碳、氟、氧……)。由于锗在空气中非常活泼,Siconi原位表面制备方案很可能在具有这种热预算约束的SiGe表面上使用。最近,评估了一种新的表面制备策略,该策略基于I)湿化学氧化物形成,然后ii)标准NH3/NF3远程等离子体Siconi工艺。为了使用这样的方案来制造器件,我们在此研究了表面制备对Si0.60Ge0.40在Si0.60Ge0.40膜上外延再生长的影响(在氧去除效率、所得形貌等方面)。我们表明,这种表面制备大大减少了界面污染,然而,在外延再生长后,表面可能是粗糙的。由于对表面制备和生长参数之间的相互作用进行了深入分析,因此我们华林科纳半导体提出了一种创新的工艺顺序,可生产出光滑、高质量的薄膜。

介绍

在先进的金属氧化物半导体场效应晶体管(MOSFETs)中,电子和空穴迁移率比大块无应变硅高几倍,这是强制性的[1]。阿格浓度通常约为30%的压缩应变SiGe例如用于14 nm技术节点p型完全耗尽绝缘体上硅器件的沟道中。在这种器件的源极/漏极(S/D)区中进行几十nm的重度原位硼掺杂SiGe的选择性外延生长(SEG)。它用于降低接触电阻,具有足够的锗硅化材料,并保持(或增加)栅极下SiGe沟道中的压缩应变。SiGe:B SEG之前的表面制备在SiGe表面上特别棘手,因为SiGe表面在空气中非常容易发生反应。在外延之前,起始表面确实应该在原子尺度上是光滑的,并且没有任何污染物(例如O、C或F)。因此,排队时间(Q时间,即在单晶片湿法清洗工具中去除自然氧化物后在空气中花费的时间)的最小化在SiGe上比在硅上更关键。

实验细节

在这项工作中,15 nm厚的SiGe 40%层在600℃、20托下在300 mm大块Si(001)晶片上外延生长。沉积厚度低于塑性松弛的临界厚度;因此SiGe膜是完全压缩应变的。标准300mm foup(ente gris)用于洁净室中的晶片储存。湿法处理在300 mm单晶片DNS SU 3100工具中进行。评估了基于标准前端化学与有效漂洗步骤的组合的各种湿法清洗顺序(表1 ),例如1)稀释的HF/HCl,2)稀释的冷或热标准清洗1 (SC1 ),即NH4OH:H2O2:H2O溶液,或3)臭氧化(O3)漂洗。

结果和讨论

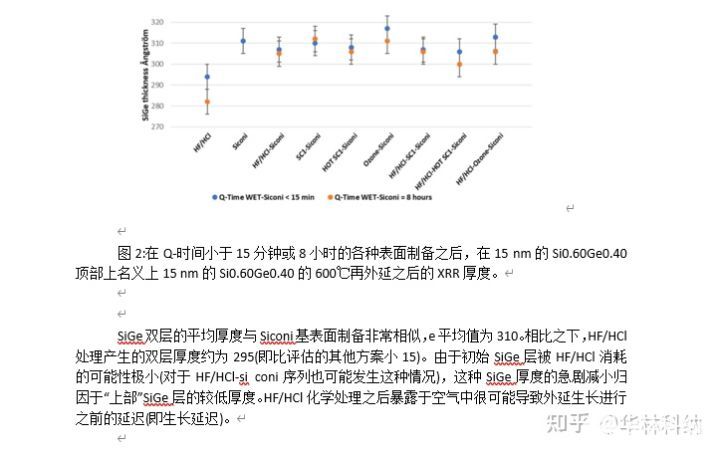

在下文中,我们已经在15 nm厚的Si0.6Ge0.4层上评估了不同的(I)湿法、(ii) Siconi和(iii)“湿法-Siconi”序列,在湿法清洗和Siconi工艺之间具有两个Q时间,少于15分钟或8小时。在没有任何空气中断的情况下,Siconi工艺之后是在超纯N2下将晶片转移到外延室,在那里进行20托的H2烘烤(温度低于或等于650°C ),并在600°C下再外延20托的另一种15 nm的Si0.6Ge0.4。这种低热预算的目的是最小化其对污染物去除效率的影响,并允许对各种探测序列进行适当的基准测试。我们首先从界面污染(SIMS和XRR)和膜质量(雾度和AFM)方面量化了使用化学氧化物-Siconi序列(先前由XPS [8]证明)的兴趣。本研究的第二个目标是在300毫米工业生产线(25个晶片的FOUP处理)的真实条件下证明这种序列的效率,然后在外延组合工具的惰性环境中,在湿清洗和装载之间有几十分钟到几个小时的Q-时间。8小时的Q-时间似乎是合理的,以显示生产线中过程的稳健性。

3.1表面处理对界面污染的影响使用Q-时间= 15分钟的表面处理

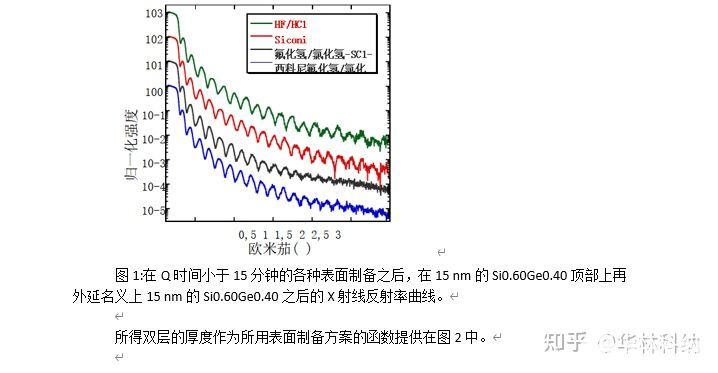

在各种化学处理(表1)之后,将Si0.60Ge0.40层装载到外延组合设备的N2净化的装载室中,进行Siconi工艺,然后转移(在N2下)到外延室,在那里进行再外延。在这些条件下,脱氧表面暴露在空气中的时间(在湿处理和晶片装载到装载室之间)不超过15分钟。在Si0.60Ge0.40外延再生长之后,通过X射线反射率测量晶片。在图1中可以找到选择的配置文件。在全外反射的临界角以上(大约0.13°),X射线传播到SiGe/Si叠层中。厚度条纹是由于表面反射的X射线和SiGe/Si界面处的相长干涉和相消干涉造成的。

结论:

在这项研究中,我们华林科纳已经展示了“化学氧化物-Siconi”序列去除SiGe自然氧化物的能力。这种顺序产生低热预算外延再生长,没有任何延迟并且氧界面污染比标准的“HF-last”湿法清洗低10倍(在低于或等于650℃的温度下H2烘烤2分钟后)。然而,这种顺序导致SiGe表面对岛化更敏感。这可能是由于在SC1 (NH4OH/H2O2/H2O)或O3溶液中浸泡后,在化学二氧化硅层下形成了一些富锗单层。为了避免岛化问题,在低热预算H2烘烤期间执行基于二氯硅烷的钝化,以在SiGe上产生薄的覆盖层(小于1nm)。所得的Si0.60Ge0.40 / Si / Si0.60Ge0.40叠层是光滑的,并且没有任何显著量的界面污染或延伸缺陷。

审核编辑:符乾江

-

生物

+关注

关注

0文章

49浏览量

15789 -

植物

+关注

关注

0文章

8浏览量

7158

发布评论请先 登录

相关推荐

半导体湿法清洗有机溶剂有哪些

应力消除外延生长装置及外延生长方法

碳化硅外延晶片硅面贴膜后的清洗方法

提高SiC外延生长速率和品质的方法

高温大面积碳化硅外延生长装置及处理方法

8英寸单片高温碳化硅外延生长室结构

芯片湿法刻蚀残留物去除方法

SiGe外延工艺及其在外延生长、应变硅应用及GAA结构中的作用

用于SiGe外延生长的湿法清洗序列

用于SiGe外延生长的湿法清洗序列

评论