引言

在半导体芯片的物理和故障分析过程中(即验证实际沉积的层,与导致电路故障的原因),为了评估复杂的半导体结构,拥有适当的处理工具至关重要。为制造的每件产品开发了去加工技术,涉及多步pfo程序,揭示芯片的逐层秘密。随着制造工艺的变化和半导体结构的变化,这些技术需要在时间和程序上不断调整。虽然有许多工具有助于这些分析,如RIE(反应离子蚀刻-一种干法蚀刻技术)、离子铣削和微切割,但钨的湿法化学蚀刻有时比RIE技术更具重现性。

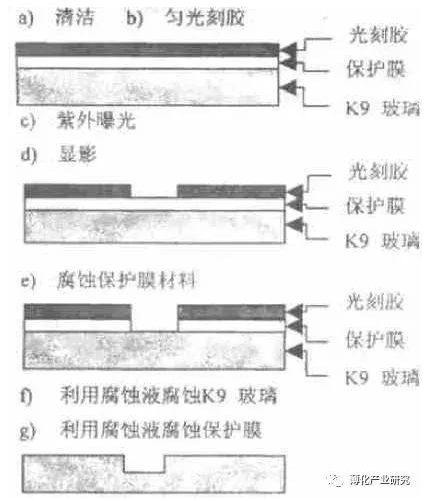

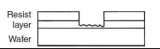

钨是MOS(硅上金属)器件中用于互连和电路的常用沉积金属。衬里材料用于桥接金属-硅,或防止金属和掺杂硅衬底之间的相互作用。耐火互连衬里可以包括MoSi或WSi,而阻挡材料包括TiW和TiN。在某些情况下,制造过程中引入的外来物质(FM)会腐蚀杆或衬垫材料。FM会形成不必要的连接(短路)或不必要的绝缘(开路)。在对芯片进行电气测试后,失败的信号通常指向导致电路故障的缺陷源。作为一个例子,如果电测试信号指示钨层下面有缺陷,则希望仅去除钨,同时保持衬垫的完整性,以评估缺陷的来源。在其他方面例如,需要高亮蚀刻以使钨稍微凹陷并限定衬里层。在这两种情况下,钨的一些表面(自上而下或横截面)必须在钨蚀刻之前暴露。

腐蚀剂描述

两种相当快速和容易的湿法蚀刻将去除钨但保留大部分衬垫完整,它们是:1)次氯酸钠(na0ci)和2)1∶1比例的氢氧化铵(NH‹0H)和过氧化氢(H2Oz)。蚀刻剂如下,并且基于最终得到可溶产品,为这些蚀刻剂中的每一种提供化学反应。

1)使用家用漂白剂(5.25%次氯酸钠)。试剂等级也可以,但通常不值得花费。在Pyrex烧杯中加热约50至100 mL至60°c。该蚀刻剂可使用6小时而无明显降解,但在此之后应进行处理和补充。

所得的可能反应产生二氧化二氯钨(W02CIz)的溶度积:

3 NaCI 0+W+Hz0-> Woz ciz+NaCl+2 na0h

2)在室温下,在Nalgene、玻璃或teflon烧杯中混合试剂级NH‹0H与Hz0z的1:1溶液(使用35% H2O2)。为获得最佳可靠性,请在混合后2小时内使用,因为Hz0t会分解。可能发生的反应产生仲钨酸铵((nh‹)zw 0236 H2O)的溶度积:

7w+21hz+6nh‹0h-->(nk‹)‹w 023 ' 6h 0+18hq

不锈钢或耐化学腐蚀的镊子也可以。将芯片放在边缘并靠在烧杯上,以帮助从烧杯中取出芯片。确保芯片足够大,能够被Geezers抓取,而不会损坏有缺陷的区域。钨在受到攻击时会嘶嘶作响。根据去除钨的厚度,试验2到10分钟,或者只需5到15秒进行高亮蚀刻。蚀刻后,将芯片浸入干净的去离子水烧杯中,然后在去离子水流中冲洗几秒钟。仍然拿着芯片,用干N2吹干。如果你的结构能够承受,超声波清洗是可以的,但是通常不需要。

优化技巧:

为了确定“完美”的蚀刻时间,使用这些蚀刻的增量时间,并用扫描电镜检查以确定蚀刻的深度。尝试使用大致相同的芯片尺寸和去加工状态,以最大化蚀刻的再现性。在精密的环境中,缺陷区域周围可消耗的钨的量会影响蚀刻时间。

为了加快这一程序的发展,使用低电压SEM(即2 KeV,500 pA -最好是FESEM)进行无涂层自上而下和简单的切除截面评估。在优化这些程序的时间时,请始终使用新鲜样品。即使在低电压下,SEM样品也可能被电子束沉积的碳、回流的油和室中的污染物覆盖,如果这种类型的样品被再次蚀刻,这将显著改变蚀刻时间和质量。虽然用氧等离子体灰化有助于去除SEM产生的沉积物,但结果并不理想。即使如此,如果只有一个样品,有时也需要灰化和重新蚀刻样品。蚀刻完成后,尽快进行SEM评估,因为新蚀刻的表面容易受到持续蚀刻和环境侵蚀的影响。当脱层发生时,光学显微镜将显示颜色变化,并且共焦显微镜有助于评估去除深度,而SEM在去除过程中提供最单一的信息。

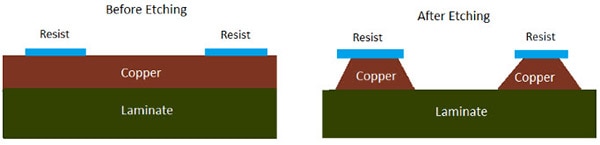

湿法蚀刻与干法蚀刻

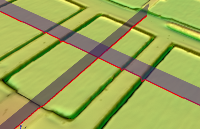

有几个原因可以解释为什么去加工甚至去高光被认为是一门“艺术”而不是一门“科学”。金属沉积技术、外形、密度、结构和微结构都将在金属蚀刻方式中发挥重要作用。今天有效的蚀刻时间和配方并不能保证对明天生产的产品也有效。在钨互连的情况下,互连中心的金属密度或微结构的接缝或变化创建一条比金属探针阻力最小(因此蚀刻速度更快)的路径。互连的核心首先被蚀刻掉,留下衬在互连周边的逐渐变薄的金属壳,并且在清除互连之前,下面的钨线可能发生不希望的蚀刻。

为什么选择湿法蚀刻技术而不是反应离子蚀刻(RIE)?理论上,RIE技术对钨沉积规律的敏感性应该低于set蚀刻。RIE可以被优化用于具有不同纵横比的蚀刻(各向同性或各向异性蚀刻),理论背后的事实是通过RIE完全单一形式的钨去除是最好的精细操作。气体流量、比率、压力和时间都是需要连续测试才能开始优化过程的变量。此外,在大多数情况下,金属图案的变化(密集区域与非密集区域)对RIE技术的影响比化学蚀刻更深远。周围的结构会遮蔽RIE工艺,并且RIE腔室的台板通常具有“蚀刻图案”,即,根据腔室内的位置,RIE蚀刻速率可以是定向的,甚至是有角度的。

RIE室的装载也影响去除速率,因为完整的八英寸晶片的蚀刻速率比装载到室中的几个一厘米的芯片要慢得多。这就是“负载系数”,指的是待蚀刻材料的表面积。当气流、时间和功率保持不变时,消耗的表面材料的量受到存在的反应气体量的限制。一个完整的8 '晶圆的蚀刻方式与从该晶圆上切下的几个芯片的蚀刻方式不同(即,你不能用一双杯状的手清空锉刀,但你可以清空水槽)。

与湿法蚀刻不同,即使在最严密监控的RIE系统中,盘形夹也总是具有从芯片边缘向中心的蚀刻梯度。也不同于湿法蚀刻,RIE室受到反应组分和吸收气体在室内壁上的积聚的困扰,特别是如果工具不仅仅用于钨蚀刻,这些积聚需要在均匀蚀刻之前进行清洁和室调节。虽然这些都是影响RIE工具的考虑因素、室内蚀刻特性的仔细评估和RIE蚀刻结果的分析可以产生在某些情况下优于湿法蚀刻的技术。

虽然湿法和RIE蚀刻技术都可以提供成功的结果和显著增强的分析能力,但是这两种技术都不能提供最佳的现成结果。

审核编辑:汤梓红

-

半导体

+关注

关注

335文章

27918浏览量

224808 -

MOS

+关注

关注

32文章

1297浏览量

94638 -

蚀刻

+关注

关注

9文章

421浏览量

15602

发布评论请先 登录

相关推荐

想做好 PCB 板蚀刻?先搞懂这些影响因素

深入探讨 PCB 制造技术:化学蚀刻

蚀刻基础知识

干法刻蚀的概念、碳硅反应离子刻蚀以及ICP的应用

芯片湿法蚀刻工艺

半导体湿法和干法刻蚀

锂电池行业中干法研磨与湿法研磨的应用

玻璃基电路板的蚀刻和侧蚀技术

玻璃电路板表面微蚀刻工艺

基于光谱共焦技术的PCB蚀刻检测

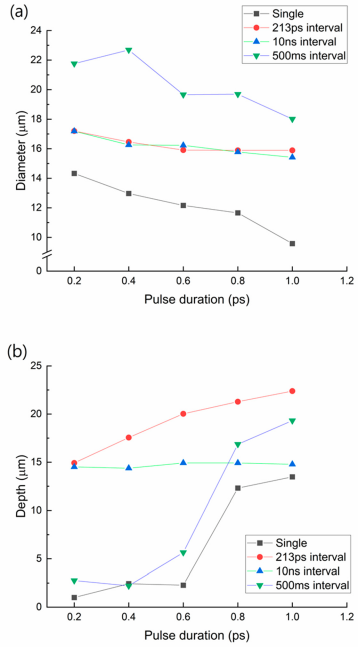

利用贝塞尔光束、超短双脉冲激光和选择性化学蚀刻研究玻璃通孔(TGV)

关于两种蚀刻方式介绍

影响pcb蚀刻性能的五大因素有哪些?

湿法蚀刻与干法蚀刻有什么不同

湿法蚀刻与干法蚀刻有什么不同

评论