如今,微控制器 (MCU) 的应用范围非常广泛。虽然这些无处不在的计算引擎在处理能力、外设产品和更高效的功耗方面取得了进步,但应用程序的数量仍在以令人难以置信的速度增长。

随着应用需求的扩大,微控制器上的关键系统组件也随之增加,时钟系统就是其中之一。该系统在微控制器中起着关键作用,对整体系统性能的各个方面都至关重要,包括优化功耗、精确计时、通信接口时钟以及微控制器内其他关键组件的内部时钟要求。

资源和要求

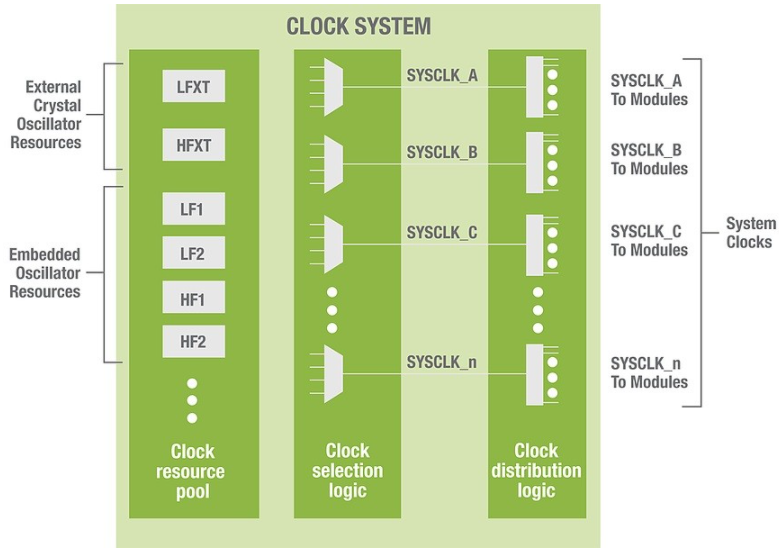

时钟系统可以被认为是一个资源池,称为时钟资源(见图 1)。每个时钟资源都针对主要目的进行了优化,即使它可以用于系统内的各种功能。时钟系统通常包括各种时钟源,称为系统时钟。这些系统时钟用于控制各种子系统组件,例如 CPU、总线接口、外设和数据转换器。由于应用要求可能有很大差异,每个系统时钟都提供多个时钟资源。

图 1:典型的微控制器时钟系统提供大量时钟资源以满足各种应用要求。

鉴于通用 MCU 可用于数百甚至数千个应用,时钟系统必须具有高度可编程性。这允许在特定应用中根据需要重新配置时钟系统。一些简单的应用只需要静态配置,时钟系统在初始化时只配置一次。其他人则需要动态配置,以允许根据应用程序的实时行为重新配置时钟系统。

时钟系统中可用的时钟资源类型很重要。应用程序具有实现特定功能所需的不同需求。例如,实时时钟系统需要一个准确的时基,以便在应用程序的整个生命周期内保持时间。大多数时钟系统都有一个集成振荡器,支持最常见的可用手表晶体,32,768 Hz。外部晶体需要适当的负载电容来正确设置频率中心并优化启动。

为了降低系统成本,一些微控制器集成了可编程负载电容器,允许一系列电容值来支持最常见的晶体负载要求。一些系统已经有可用的实时时钟资源。对于这些系统,旁路模式可以允许此资源与微控制器共享。以类似的方式,微控制器时钟系统可以输出缓冲的实时时钟源,以便在需要时在系统的其他地方使用。

在过去几年中,微控制器频率范围急剧增加。随着软件复杂性水平的提高,处理要求推动了频率范围的扩大。大多数 MCU 有多种方法来生成系统所需的高速时钟,最常见的是使用不需要外部组件的嵌入式振荡器。这节省了组件成本,更重要的是,降低了微控制器的引脚要求。振荡器通常设计为具有良好的启动时间,以及在电压和温度范围内 1% 到 3% 的相当严格的容差。

发现故障并防止错误

时钟系统的一个关键方面是系统时钟的可靠性,尤其是处理器时钟。理想情况下,处理器时钟应该随时可用,以确保应用程序可以从可能导致死锁情况的系统错误中恢复。由于时钟系统是高度可编程的,如果代码执行误入歧途,它会因不正确或无意的编程而带来一些风险。

大多数时钟系统对所有关键时钟系统配置寄存器都有密码保护访问。这最大限度地减少了由于错误代码执行而导致的意外配置的可能性。此外,一个好的时钟系统应该有其他硬件机制来防止死锁情况。

一个很好的例子是所有晶体资源的适当故障安全机制。由于电路板磨损、静电放电事件、焊点薄弱和其他原因,外部晶体或谐振器可能会失效。如果处理器系统时钟使用晶体作为其资源并且它发生故障,这可能会导致时钟丢失,并且可能会发生死锁情况。

为了防止这种情况,大多数微控制器都有硬件机制来检查晶体是否正常运行。检查包括不振荡或可能在不适当的频率范围内振荡。无论如何,如果检测到故障,系统时钟会自动切换到已知的良好时钟资源,从而允许应用程序代码继续执行。此外,还会向应用程序报告错误条件,例如不可屏蔽中断或复位条件,应用程序可以在这些条件下确定要采取的操作。这种已知的良好时钟源通常是完全嵌入式的振荡器,在启动特性和振荡可靠性方面非常稳健。

提高能源效率

大多数 MCU 应用需要低功耗或超低功耗。由于许多应用使用有限的能源,例如小型、低容量电池,产品寿命取决于能源的有效使用。节约能源的最佳方法是在给定时间使用适当数量的能源,并在所有其他时间将所有能源消耗降至最低。这是经典的占空比曲线。通常,大多数供应商将此称为活动时间与睡眠或待机时间。设备可以保持睡眠时间的时间越长,整体消耗的能量就越少。

时钟系统设计对于最大限度地减少睡眠或待机操作期间的能量需求至关重要。大多数待机或睡眠模式的特点是使用低频时钟。有几个选项可以提供这种低频时钟操作。

手表水晶就是这样一种资源。它的额定工作频率为 32 kHz,非常精确,并且可以设计为在 500 nA 或更低的极低电流消耗下工作,具体取决于晶体类型。如果系统中已经有手表水晶,这是一个不错的选择,因此不会产生额外费用。如果不需要晶体,嵌入式振荡器是另一个有效的选择,它的功耗极低,有些低至 100 nA。

这些振荡器通常涉及功率与精度之间的权衡。更高的精度通常需要消耗更高的功率。振荡器受温度和电压变化的影响,这在某些应用中可能很重要。因此,许多微控制器为此目的具有各种时钟资源,其中一些具有更高的功率要求但改进了精度或漂移特性。这些振荡器坚固耐用且成本低廉,无需外部组件或引脚。

时钟系统的另一个可以显着降低功耗的重要方面是时钟分配逻辑,它涉及到各种时钟系统如何在 MCU 内部进行路由或分配。由于时钟是动态功耗的关键因素,因此时钟分配逻辑的完成必须以最大限度地减少不必要的时钟负载和时钟切换的方式完成。不需要时,所有系统时钟都应关闭或保持静止。此外,只有需要特定系统时钟的逻辑才能被视为相应时钟的负载。

许多微控制器将特定的系统时钟分成几个单独的时钟,这些时钟只为特定的模块或外围设备供电。当特定模块需要系统时钟时,它会发送一个请求,只有请求时钟的模块才会接收它,从而大大降低了整体动态功耗。

适用于多种应用的灵活设计

为微控制器设计时钟系统涉及许多方面。德州仪器 (TI) 的 MSP430 5xx/6xx 系列微控制器包含许多前面描述的必要组件。这些 MCU 支持低频手表晶体操作,以及广泛的高频晶体。两个晶体都具有故障安全逻辑,可以在旁路模式下使用。时钟系统还包含一个带有锁频环 (FLL) 的嵌入式振荡器,无需外部组件即可实现高频操作。FLL 允许任何倍数的低频时钟作为其参考,从而提供了频率选择的灵活性。

低于 100 nA 的极低功耗嵌入式振荡器可用于低功耗、非精确、无晶体时钟应用。更精确的低功耗嵌入式振荡器也可用于更严格的时钟需求。此外,复杂的时钟分配逻辑与高度灵活的时钟请求系统一起提供。时钟系统的所有这些方面使 TI 的 MSP430 5xx/6xx 系列微控制器能够以低功耗、经济高效的方式服务于各种不同的微控制器应用。

审核编辑:郭婷

-

微控制器

+关注

关注

48文章

7571浏览量

151633 -

嵌入式

+关注

关注

5087文章

19148浏览量

306158 -

振荡器

+关注

关注

28文章

3840浏览量

139169

发布评论请先 登录

相关推荐

面对快速迭代的技术,怎能忽视设备升级的高效与灵活性?

使用可扩展微控制器实现设计灵活性

微控制器的结构和应用

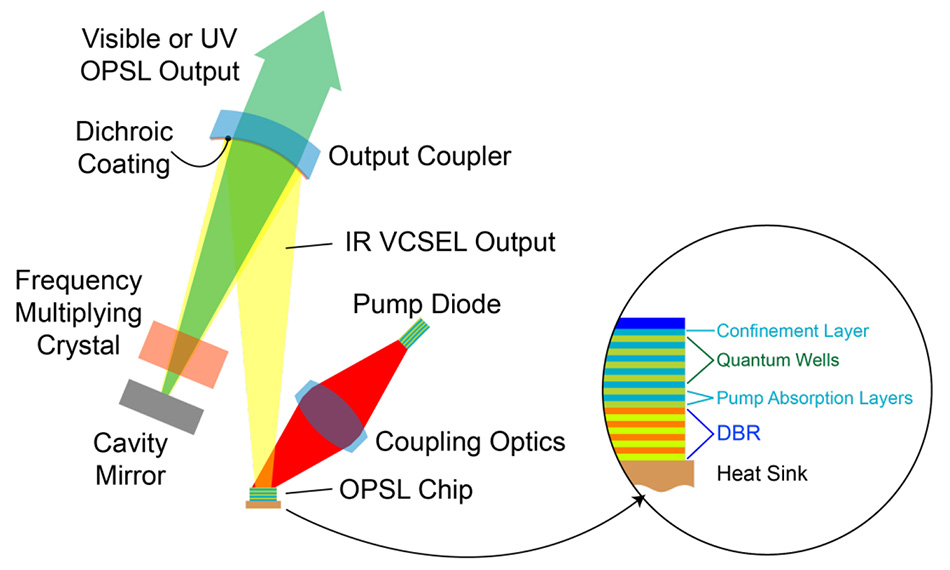

OPSL 优势1:波长灵活性

组合逻辑控制器与微程序控制器各有什么特点?

8芯M16公头如何提升灵活性

提高微控制器时钟系统的灵活性

提高微控制器时钟系统的灵活性

评论