美光:3D NAND继续往多层次发展

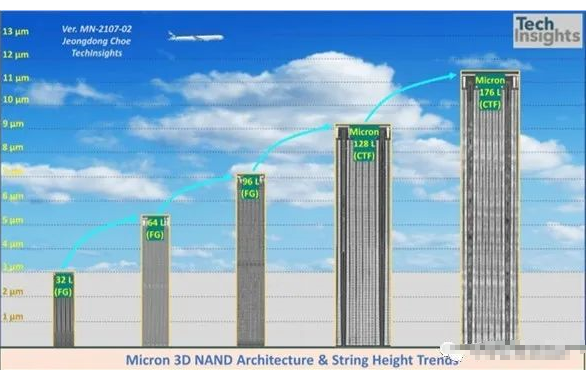

从2016年左右开始,因为二维设计不能满足其不断增加的小型化需求,NAND Flash走向了三维。之后,为了提高内存密度,各家公司都在认真增加三维堆栈的数量。例如,美光比其他任何厂商都更早地开始生产 32 层、64 层、96 层、128 层和 176 层。

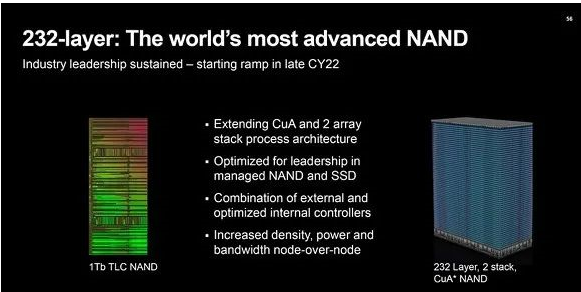

此外,在 2022 年 5 月 13 日,就在 IMW2022 召开之前,有消息称美光将从 2022 年下半年开始生产 232 层 3D NAND。这个 232 层的 3D NAND 是一个 116 层NAND的两层堆栈。采用了所谓的CMOS Under Array(CUA)结构,在存储器阵列的底部形成CMOS电路。

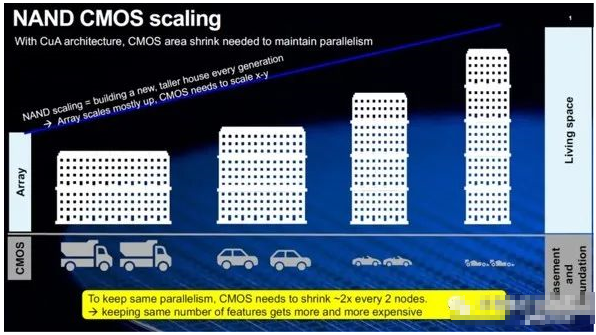

虽然增加堆栈数量以提高 3D NAND 的存储密度的方法很简单,但存在很多问题,例如打开高纵横比(AR)的存储孔并将其嵌入。因此,美光提出通过在平面方向,即XY方向上对存储单元进行缩放,以及依靠堆叠层数的增加来提高存储密度。

下午是存储单元阵列的平面图。一个称为柱子的小圆圈上下贯穿阵列堆栈。围绕柱子的字线 (WL) 充当存储器件的栅极。即柱与WL的交叉点形成存储装置的存储单元。该单元以不同的阈值电压 (Vt) 水平存储二进制数据。

WL之间的间隙称为狭缝,这是形成存储单元阵列所必需的结构。这是因为在 3D NAND 中,牺牲 WL 材料的去除和金属栅极的形成是通过狭缝进行的。

对于具有这种结构的存储单元,有两种 XY 缩放方法。一是减小狭缝宽度,二是密集排列柱子。这种方法称为支柱间距缩放。

从上图还可以看到,当狭缝之间的柱的数量增加到4柱、9柱、14柱和24柱时的存储单元的平面图。当狭缝之间的柱子数量超过 14 时,缩放收益开始减少。因此,可以看出,一味地进行柱间距缩放是不够的。

因此我们可以得出结论,有两种方法可以提高 3D NAND 的存储密度。一种是在垂直方向上堆叠存储单元。另一种是在XY方向上缩放存储单元。

前者对高AR孔的加工和上下级孔的对位难度逐年增加。而后者则是缓解存储器单元在垂直方向的指数堆叠的利器。

但是,如果继续XY方向的微细化,则CMOS的小型化将继续,例如,可以将FinFET用于晶体管,或者可以将EUV应用于精细布线。这些不能轻易采用,因为它们会导致内存成本飙升。

因此,当在 XY 方向缩放时,有必要想办法减少每比特的 CMOS 电路,以避免使用 FinFET 和 EUV 等昂贵的工艺。

综上所述,垂直堆叠、XY方向缩放、CMOS电路每比特减少这三种方法对于未来3D NAND的高密度化具有重要意义。

铠侠:液氮温度下的3D NAND演示实验

数据中心发热已成为全球性问题。因此,出现了浸入式服务器。这也就是我对 Kioxia 的公告感到惊讶的原因,因为他们通过将 3D NAND 浸入绝对温度为 77K 的液氮中来展示其操作。

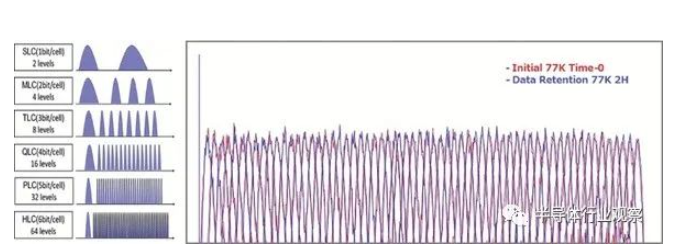

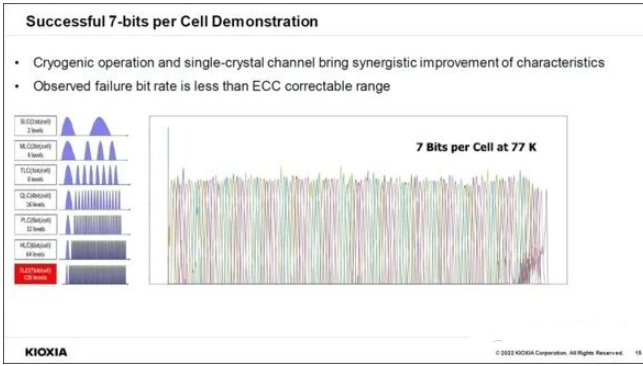

铠侠在 2019 年的 IEDM 上报告称,它通过将 3D NAND 存储单元分成两部分来运行 5 位/单元(Penta Level Cell (PLC))。2021 年 12 月,铠侠在 IEEE Journal on Exploratory Solid-State Computational Devices and Circuits上通过将 3D NAND 浸入液氮中成功实现了 6 位/单元操作,并已经完成相关操作。

这一次,铠侠的目标是通过将3D NAND浸入液氮中,并将3D NAND的沟道从多晶硅改为单晶硅,进一步提高价值。下图左侧显示了本次使用的单晶硅沟道的3D NAND结构,下图右侧则显示了实验设置。

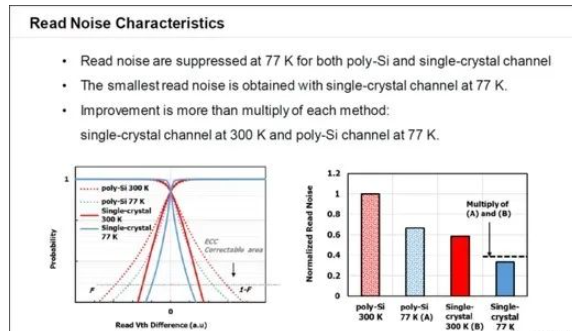

首先,3D NAND的读取噪声结果如图所示。如果将多晶硅沟道在室温300K的读取噪声标准化为“1”,只需将其浸入77K的液氮中即可将噪声降低至70%,室温300K时噪声为60%在单晶通道中,当单晶沟道浸入液氮77K时,噪声降低到40%以下。

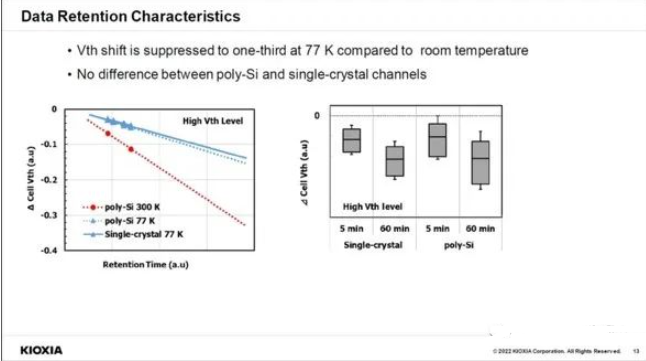

接着,数据保持特性的实验结果如图所示。发现在 77K 的液氮温度下,由于电荷损失导致的 Vth 偏移小于在 300K 的室温下。还发现多晶硅和单晶硅在液氮温度为 77 K 时没有区别。

然后,将单晶沟道的3D NAND浸入液氮中运行,成功实现7bit/cell。

铠侠将5-bit/cell称之为Penta Level Cell (PLC)。6 位/单元会是 Hexa Level Cel (HLC) 吗?而7 bits/cell就是Hepta Level Cell (HLC),但是缩写是6 bits/cell和7 bits/cell是一样的。我们应该如何区分?

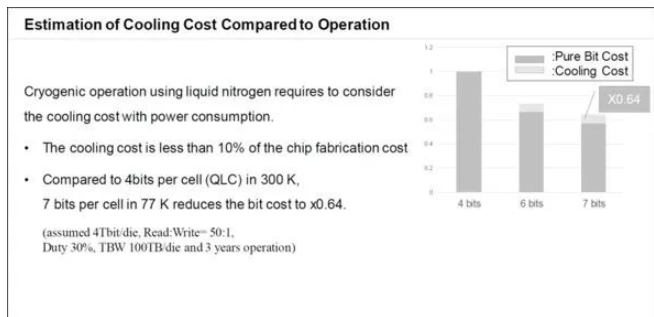

就算能做到 7 bits/cell,但用液氮冷却 3D NAND 可能成本会很高(我也是这么认为的)。为此,铠侠对成本进行了估算,如图所示。

参考是在 300K 的室温下运行 4 位/单元 (QLC) 3D NAND 的情况进行的。

据铠侠测算,液氮冷却的成本不到芯片制造成本的10%。因此,在液氮 77K 中可以运行 7 位/单元的 3D NAND 的成本是参考的 64%。如果这个计算是正确的,用液氮冷却不会导致成本增加。

-

美光

+关注

关注

5文章

707浏览量

51389 -

3DNAND

+关注

关注

2文章

18浏览量

10629 -

铠侠

+关注

关注

1文章

90浏览量

7678

发布评论请先 登录

相关推荐

铠侠推出162层3D闪存 提升了10%密度

3D NAND flash大战开打 三星独霸局面打破

铠侠开发新的3D半圆形闪存单元结构“Twin BiCS FLASH”

铠侠展望3D XPoint前景,3D NAND技术成熟占据主导

美光和铠侠对3D NAND FLASH的布局介绍

美光和铠侠对3D NAND FLASH的布局介绍

评论