摘要

跨晶圆栅极临界尺寸(CD)的一致性会影响芯片与芯片之间在速度和功耗方面的性能差异。随着线宽减小到90 nm及以下,跨晶片CD均匀性的性能规格变得越来越严格。本文介绍了我们华林科纳提出了一种新的方法,通过光刻和刻蚀工艺顺序来提高跨晶片栅极CD的均匀性。我们华林科纳所提出的方法是通过优化整个晶片曝光后烘烤(PEB)温度曲线来补偿光刻工艺顺序中的上游和下游系统CD变化成分。更准确地说,我们首先构建了一个温度-偏移模型,该模型将PEB温度分布与多区PEB板块的设定点偏移相关联。然后从CD扫描电子显微镜测量中识别将跨晶片CD与PEB板的设定点偏移相关联的第二模型。然后基于CD-偏移模型和温度-偏移模型提出了显影后和蚀刻后CD均匀性增强方法。温度-偏移模型被确定为更适合用于CD均匀性控制,因为与CD-偏移模型相比,它具有更好的保真度和便携性。我们证明,在验证实验中,蚀刻后CD变化的标准偏差减少了约1nm,这验证了所提出的CD均匀性控制方法的有效性。

索引术语—约束二次规划、临界尺寸(CD)、临界尺寸均匀性(CDU)、多目标优化、多区域PEB烘烤板、等离子体蚀刻偏差信号、曝光后烘烤(PEB)、过程控制、过程建模。

介绍

如今,批次间和晶圆间的临界尺寸变化一般通过先进工艺控制(APC)来解决。已经对控制晶片老化CD进行了广泛的研究,其方案从前馈到前馈/反馈闭环控制[3]–[ 7]。在这些论文中,CD数据被用于校正来自光刻蚀刻顺序的扰动,以便将晶片平均CD调节到目标,并最小化晶片间和批次间的CD变化。整个晶片的CD可变性变得越来越重要,这要求工艺控制超越批次与批次和晶片与晶片的水平,达到整个晶片的水平,以减少可变性。不幸的是,在现有文献中还没有对跨晶片CD变化的控制进行深入研究。有效控制跨晶片CD变化将导致更紧密的芯片速度和功耗分布。这进而导致更一致的芯片性能和更高的产量。

在整个光刻和蚀刻过程中,各种来源导致CD变化。这些可以如表1所示进行分类。减少跨晶片CD变化的最简单和最直接的方法是使每个处理步骤在空间上均匀。一些研究人员已经研究了提高单个处理步骤的均匀性。Ho等人提出了一种级联控制结构[8],通过控制多区烘烤板的温度分布,将涂覆的抗蚀剂膜厚度不均匀性降低到小于1 nm。向min-展示了坂本的一种新的开发应用技术

尽量减少显影不均匀性,导致晶片CD偏差为6nm(3 sigma)[9]。

然而,对于300毫米晶片加工来说,使每个加工步骤在空间上均匀变得过于昂贵。此外,并不是通过光刻蚀刻顺序的每个处理步骤都提供空间控制权限。我们注意到,在典型的蚀刻工艺中,空间可控性受到严重限制。唯一潜在可用的控制机制是双区ESC冷却系统中背面氦气压力的调节。然而,这种双氦区系统在蚀刻机中并不普遍。此外,由于其仅有的双区配置,背面氦气压力调节在蚀刻过程中提供非常有限的控制权限。光刻步骤提供了更多的空间控制机会。这包括逐个芯片的曝光剂量调整

[10]通过调整加热器区域控制器的偏移和PID设置[12],在曝光后烘焙(PEB)步骤中调整空间温度曲线。这两个控制输入通常很容易接近。我们论文的中心思想是使用这些控制机制,通过补偿其他系统的跨晶片CD变化源,如上游显影不均匀性和下游等离子体蚀刻偏置信号,来改善蚀刻后跨晶片CD均匀性。在这篇论文中,我们把我们的控制行为限制在PEB步骤。曝光设置的探索是一个有待在未来研究中分析的课题。

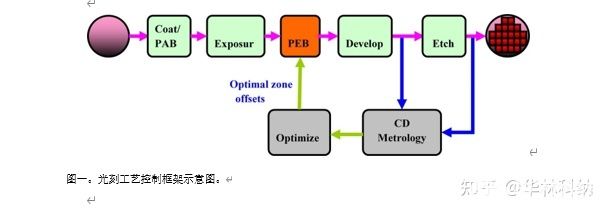

为了说明我们的方法,考虑图1所示的典型光刻工艺控制框架。因为局部PEB温度可以直接控制局部CD,所以如果通过适当调整PEB温度空间分布可以平衡整个晶片CD变化源,则可以最小化整个晶片的显影后/蚀刻后CD变化1。

通过将PEB温度与多区域烘烤板区域控制器偏移相关联的温度-偏移模型或者将CD与多区域烘烤板区域控制器偏移相关联的CD-偏移模型,可以获得对应于最小化CD扩散的期望PEB温度分布的最佳加热器区域控制器偏移。这些模型是通过一组设计好的实验从实验中提取出来的。还通过平行设计的实验提取了KrF和ArF抗蚀剂的局部光致抗蚀剂PEB热敏性。

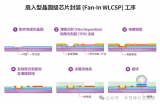

如图2所示,在裸硅衬底上涂覆2950 KrF DUV抗蚀剂。光刻工具是一个248纳米波长扫描仪,以及一个现代跟踪功能的多区PEB烘烤板模块。使用最先进的CD扫描电子显微镜(SEM)来测量横跨每个晶片的45个管芯处的线间距光栅上的抗蚀剂CD。

本文的其余部分组织如下。第二节介绍了多区烘烤板和从实验设计(DOE)中提取的经验温度偏移模型和临界尺寸偏移模型。第三节介绍了显影后[即显影检查或(DI)] CD均匀性控制方法以及蚀刻后[即最终检查或(FI)] CD均匀性控制方法。获取基线光刻-蚀刻工艺特征的表征实验和蚀刻后CD均匀性控制的验证实验在第四节中描述。最后,第五部分给出了结论和讨论。

审核编辑:符乾江

-

半导体

+关注

关注

334文章

27527浏览量

219962 -

蚀刻

+关注

关注

9文章

414浏览量

15449

发布评论请先 登录

相关推荐

【「大话芯片制造」阅读体验】+ 芯片制造过程和生产工艺

芯片湿法蚀刻工艺

光刻工艺的基本知识

详解不同晶圆级封装的工艺流程

WD4000系列晶圆几何量测系统:全面支持半导体制造工艺量测,保障晶圆制造工艺质量

WD4000系列晶圆几何量测系统:全面支持半导体制造工艺量测,保障晶圆制造工艺质量

通过光刻和蚀刻工艺顺序提高整个晶圆的关键尺寸均匀性(1)

通过光刻和蚀刻工艺顺序提高整个晶圆的关键尺寸均匀性(1)

评论