正文开始前,闲扯几句。在接下来分析CCIX规范的过程中,大家会发现CCIX里面有太多ARM的影子,尤其是协议层的一致性协议部分,你会看到有很多跟CHI相似的东西。另外,在CCIX规范的底层,基本全是复用和遵循PCIe规范。

说到PCIe,就必须先提一提PCI。PCI是Peripheral Component Interconnect的缩写,它是一种由英特尔公司1991年推出的局部总线标准。最早提出的PCI总线工作在33MHz频率之下,传输带宽达到132MB/s,基本上满足了当时处理器的发展需要。后来,随着对更高性能的要求,不断把PCI 总线的频率提升。 PCI使用共享并行总线架构,其中PCI主机和所有设备共享一组通用的地址,数据和控制线。 这种并行架构天然决定了PCI的时钟频率不可能一直提升。因为随着时钟频率的不断提升,并行总线间的信号干扰(EMI)会越来越严重。所以PCI后期已经不能适应高速发展的数据传输需求。

PCI-Express(Peripheral Component Interconnect express,简称PCIe)应运而生。PCIe是一种高速串行计算机扩展总线标准,它原来的名称为“3GIO”,是由英特尔在2001年提出的,旨在替代旧的PCI,PCI-X和AGP总线标准。PCIe属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽。它的主要优势就是数据传输速率高。目前,PCIe交由PCI-SIG组织负责维护和发布。市场已经有支持PCIe 5.0标准的控制器和设备,相信不久之后,PCIe 6.0将会大规模商用。

由于PCIe标准极其复杂,本人能力有限,对PCIe标准还处于学习阶段。所以后面跟PCIe相关的部分一带而过,主要介绍一下CCIX独有的部分,重点是规范中的第三章。

如果有小伙伴精通PCIe,还望不吝赐教。

接下来,我们按照CCIX规范的章节过一遍,主要是对规范内容的理解和归纳。CCIX规范本身比较晦涩难懂,而且通篇看下来感觉有一些段落前后顺序有些颠倒。比如我发现有一些概念是先用后解释,造成的后果就是初看前面的时候一头雾水,看到后面的章节才明白前面大概在说啥。如果大家也有类似的感觉,不妨多看几遍。本系列文章中尽量避免这些问题,但是由于本人水平有限,难免会漏掉一些细节或者有理解不准确的地方,请见谅,一切以spec为准。

1. 文档概述

CCIX规范定义了一些术语:

Port:端口与物理引脚关联,并有两个子层,CCIX Port和Transport Port。CCIX端口充当来自CCIX设备的CCIX协议层消息的入口(Ingress)和出口(Egress)。传输端口是充当传输层数据包进出网关的控制器。

CCIX Link:CCIX链路是一对CCIX端口之间的逻辑连接。

PCIe Link:PCIe链路是PCIe端口的物理连接。

Transport Link:传输链路是指传输层规范中用于覆盖CCIX协议层的物理链路。

CCIX Components:CCIX组件是定义CCIX一致性协议所需的模块。

Acceleration Function:加速功能(简称AF)是针对一致性协议的内存访问请求的特定实现源,该协议由CCIX请求代理表示,用于通过CCIX一致性层进行通信,后文中会经常提到AF。

CCIX Device:CCIX设备是由一个或多个符合CCIX协议的CCIX组件组成的物理实体。

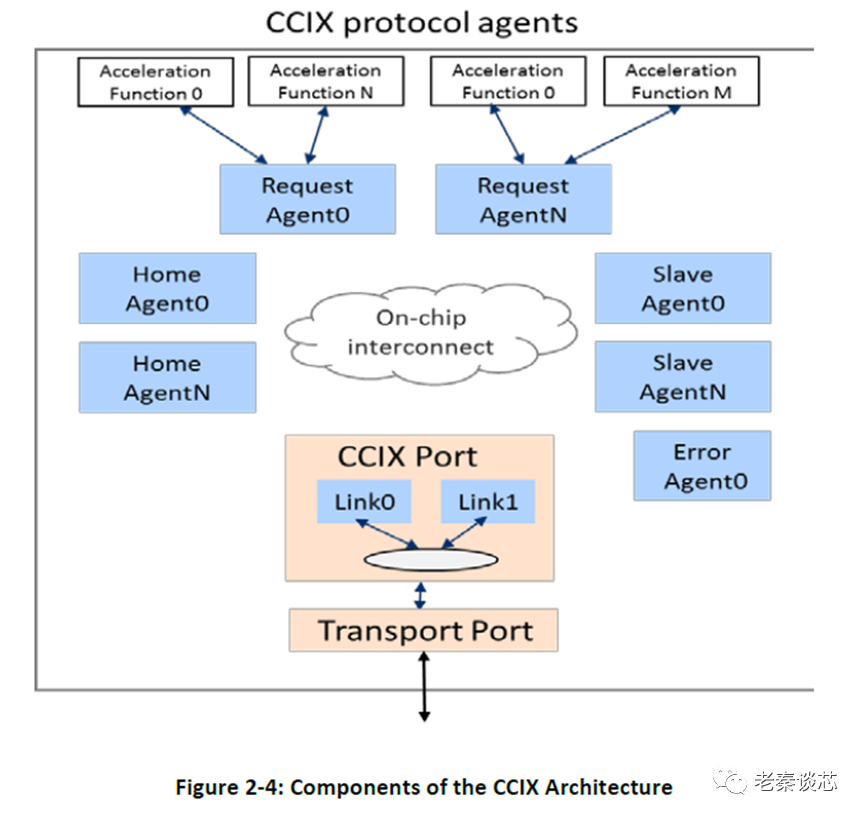

CCIX Agent:CCIX代理,在规范中分为四类,Request Agent(RA),RA是读写事物的源端;Home Agent(HA)负责管理给定地址范围内的一致性和内存访问;Slave Agent(SA),处理HA的事务,扩展系统内存,包括连接到外围设备的存储;Error Agent(EA),接受和处理协议错误消息。

CCIX Function Blocks:定义CCIX组件功能所需的构建模块。

CCIX Switch:一种CCIX设备,由两个或多个CCIX ports组成,支持端口到端口的转发。

Packet:独立路由的数据传输单元。

SAM:System Address Map,系统地址映射。

G-SAM:Global System Address Map。

G-RSAM:Global Request Agent System Address Map。

G-HSAM:Global Home Agent System Address Map。

RSAM:请求代理视角的SAM。

HSAM:主代理视角的SAM。

PSAM:端口相关的SAM。

EDR:Extended Data Rate,除了PCI Express基本规范定义的标准PHY速度之外的PHY的数据速率。

ESM:Extended Speed Mode,ESM是一种允许PCIe链路速度在标准PCIe速度和EDR速度之间转换的机制。

CCIX Consortium Identifier(CCID) :CCIX DVSEC结构和CCIX PCIe兼容头协议消息中的16位公共标识符。

CCIX Consortium Unique Value(CCUV) :CCIX DVSEC结构和CCIX PCIe兼容头协议消息中的硬件默认16位值。

2. CCIX概述

CCIX规范扩展了处理器-处理器,处理器-内存,处理器-加速器,加速器-加速器之间的数据共享。CCIX允许所有处理实体之间的一组公共虚拟地址(VA)引用所有数据结构。为了实现这些功能,CCIX扩展了共享虚拟内存(Shared Virtual Memory,SVM)模型。

扩展系统内存:CCIX允许将系统内存域扩展到主机连接内存之外。作为系统内存的一部分,主机内存管理器可以选择以与主机内存分配和管理相同的方式,去分配和管理外围连接的内存。因此,通过CCIX内存扩展,主机可以扩展其内存容量和/或支持新的内存技术。主机的外围连接内存视图与多节点主机系统中现有的内存视图一致,即非统一内存访问(NUMA)内存模型。

基于处理器或加速器的应用程序访问模式的软件透明数据移动:CCIX在加速器中支持硬件一致性缓存,并为处理器和加速器访问维护共享数据的一致视图,而无需软件干预。在CCIX系统中,缓存允许根据处理器或加速器的访问模式隐式移动共享数据,以便进一步重复使用或修改,而无需在它们之间迁移或维护多个或修改后的副本。

应用程序管理的数据从主机移动到加速器连接的内存:CCIX使应用程序能够协调从一个内存节点到另一个内存节点的数据移动,而无需任何操作系统协助。这允许数据生产者将数据放在作为数据消费者的计算实体(处理器或加速功能)旁边。

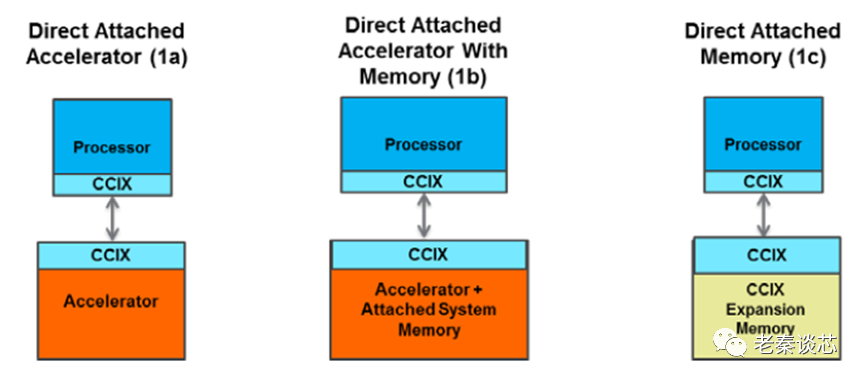

以上所说的这几点构成了主机内存和处理器、外设连接内存和加速器之间无缝数据共享的基础。扩展系统内存没什么好解释的了;CCIX规范支持在多芯片的处理器内核之间共享缓存数据,这种共享是通过一致性协议来完成的,对软件来说是完全透明的;至于应用程序管理数据,我的理解是类似于CHI中的cache stashing。CCIX标准支持多种拓扑结构:tree,mesh,ring等等。比如下图中的直接连接拓扑:

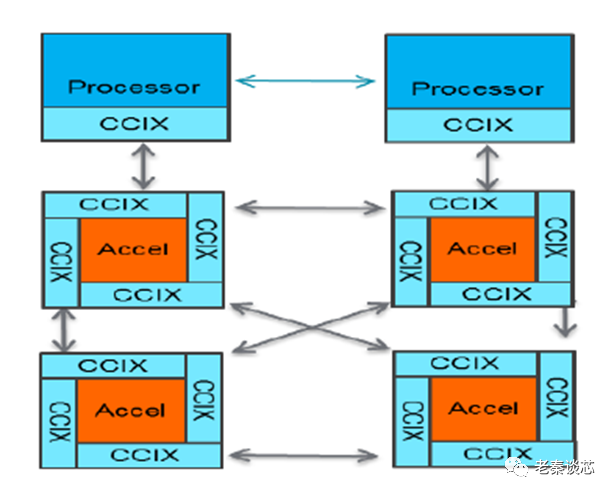

全连接拓扑:

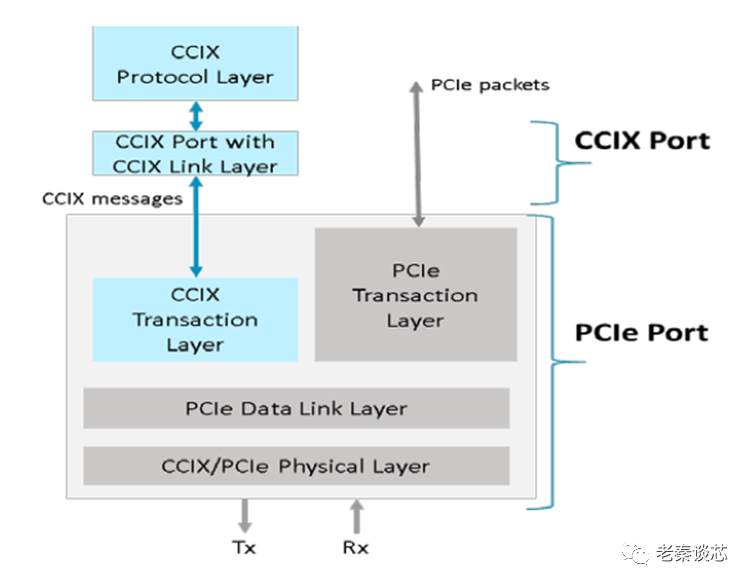

上一篇中介绍过了CCIX规范的分层架构模型,这里就不再重复了。放张图帮助大家回忆。

每个CCIX端口都与一个传输端口(Transport Port)相关联。传输端口仅限于PCIe端口。CCIX端口负责创建与PCIe兼容的供应商定义消息(VDM)事务层数据包(TLP),或具有优化报头的CCIX数据包。CCIX协议消息在PCIe兼容或优化TLP的有效负载中承载。每个CCIX端口可以与一个或多个CCIX端口通信。

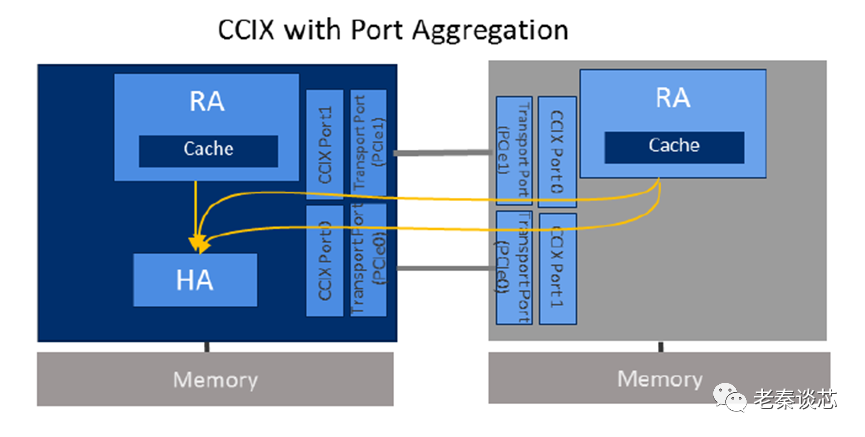

CCIX可以通过选择性地聚合多个CCIX端口,在两个CCIX设备之间实现更高的带宽连接。CCIX体系结构定义了一种跨多个CCIX端口分配内存访问请求和监听的方法,当PCIe用作传输时,每个CCIX端口映射到一个PCIe控制器,以有效地在CCIX代理之间实现更高的带宽。端口聚合(Port Aggregation)通常用于单个端口的可用吞吐量不足以满足两个芯片之间的通信需求的情况。如下图所示,右侧芯片的RA的请求可以通过两个CCIX端口(图中的Port 0和Port 1)发给左侧芯片的HA,达到增加两个芯片数据共享的带宽。

CCIX设备可以作为PCIe设备被主机发现和管理。组件及其功能通过PCIe配置空间中指定的特定供应商的扩展功能(DVSEC)部分被主机识别。CCIX DVSEC在PCIe配置头的DVSEC供应商ID字段中携带通用CCIX ID(CCID)。CCIX DVSEC定义了功能,还提供了控制和状态字段。CCIX一致性互连通过标准CCIX驱动程序进行管理。AFs通过供应商提供的驱动程序作为PCIe功能进行管理。CCIX允许加速器连接的内存成为整个系统内存的一部分。然后,内核内存管理器将其作为可分配系统内存进行管理。

CCIX定义了服务器级可靠性、可用性和可维护性(Reliability Availability Serviceability,RAS)功能集。CCIX的RAS体系结构通过PCI Express基本规范中定义的高级错误报告(Advanced Error Reporting,AER)机制维护PCIe传输错误的报告。与CCIX一致性互连相关的错误通过一个单独的并行机制报告给AER。这个记录和报告协议错误的新机制称为协议错误报告(Protocol ErrorReporting,PER)机制。CCIX设备中的PER错误记录在协议DVSEC中。

CCIX利用PCIe的地址转换服务(Address Translation Service,ATS)标准,允许CCIX设备将虚拟地址(VA)映射到其相关的物理地址(PA),并提供每页的访问控制。CCIX规范要求,所有CCIX设备需要提供以下保证:CCIX设备通过地址转换服务确保来自AFs的所有请求受访问权限控制

CCIX设备确保在设备上的固件受信任

CCIX可以使用PCIe标准的消息信令中断(MSI/MSI-X)将事件从加速器发送到主机处理器。在前面讲ARM中断控制器的时候介绍过一些MSI的知识,想了解更多的话,往前翻一翻,或者去看看PCIe的规范。通过这两次的学习,我们对CCIX的大体轮廓有了一个认识。CCIX是在PCIe规范的基础上发展出来的,在复用了大量PCIe规范的同时添加了CCIX协议层,CCIX链路层和CCIX事务层,并通过这三层定义了缓存一致性协议和所需的CCIX消息,以及消息传递机制。这三层往下就是复用PCIe的分层结构了。另外,CCIX规范扩展了PCIe的物理层数据传输速率。

原文标题:技术分享 | CCIX(二)

文章出处:【微信公众号:安芯教育科技】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

处理器

+关注

关注

68文章

19548浏览量

231876 -

加速器

+关注

关注

2文章

816浏览量

38393 -

PCIe

+关注

关注

15文章

1285浏览量

83729

原文标题:技术分享 | CCIX(二)

文章出处:【微信号:Ithingedu,微信公众号:安芯教育科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一文了解Highcharts

一文了解Android UDP通信

详细了解骁龙8至尊版强大的AI能力

xshell7,详细了解xshell7是什么

深度了解SiC材料的物理特性

一文了解激光测距传感器

IPC-6012E CN 2020中文 CN 刚性印制板的鉴定及性能规范

一文了解MySQL索引机制

科普 | 一文了解FPGA

一文带你了解NVIDIA Jetson

一文详细了解CCIX规范

一文详细了解CCIX规范

评论