在我之前写的FPGA时序约束教程中,有一篇中讲到了虚拟时钟:

但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

首先,虚拟时钟用于什么地方?

虚拟时钟通常用于设定输入和输出的延时,即set_input_delay和set_output_delay。可能有同学忘记这两个约束的用法了,这里我们再展示一下:

set_input_delay0.5-clockclkA[get_portsA]

set_output_delay1-clockclkB[get_portsB]

其中clkA和clkB就是我们使用create_clock创建的主时钟或者虚拟时钟。

主时钟在创建的时候需要指定时钟输入端口,虚拟时钟不需要指定端口,所以称之为虚拟时钟。那什么场景下要用到虚拟时钟呢?

- 外部IO的参考时钟并不是设计中的时钟

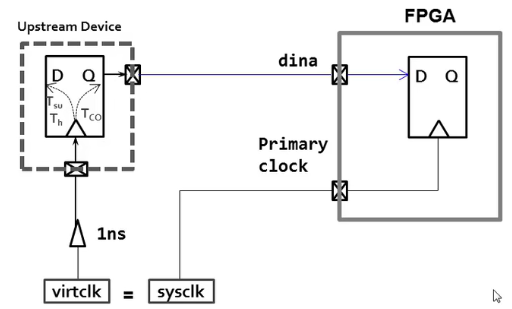

下图中,外部IO的参考时钟比设计中主时钟的路径上多了一个BUFFER,因此我们需要使用虚拟时钟来进行约束。

create_clock-namesysclk-period10[get_portsclkin]

create_clock-namevirtclk-period10

set_clock_latency-source1[get_clockvirtclk]

set_input_delay-clockvirtclk-max4[get_portsdina]

set_input_delay-clockvirtclk-min2[get_portsdina]

- FPGA I/O路径参考时钟来源于内部衍生时钟,但与主时钟的频率关系并不是整数倍

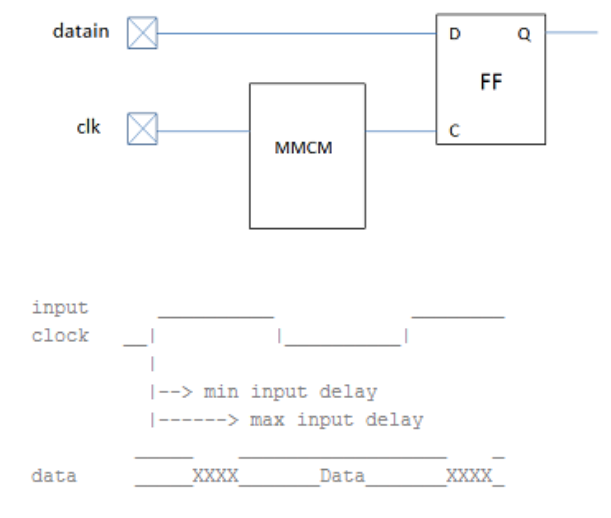

如果I/O路径参考时钟源于内部的衍生时钟,那set_input_delay和set_output_delay约束中-clock参数后的时钟不能是衍生时钟,比如下图的例子中,输入10MHz时钟经过了MMCM后去采输入的数据。

image-20211206203529124

image-20211206203529124a) 如果MMCM没有负的相移而且输出的频率也是10MHz,那么直接使用主时钟来约束input delay。

create_clock-period100.000-nameclk[get_portsclk]

set_input_delay-clockclk-max2.000[get_portsdatain]

set_input_delay-clockclk-min1.000[get_portsdatain]

b) 如果MMCM输出频率是60MHz,那么这个衍生时钟跟主时钟并不是整数倍关系,这时就需要用到虚拟时钟了

create_clock-period100.000-nameclk[get_portsclk]

create_clock-nameclk_port_vclk-period16.67

set_input_delay-clockclk_port_vclk-max2[get_portsdatain]

set_input_delay-clockclk_port_vclk-min1[get_portsdatain]

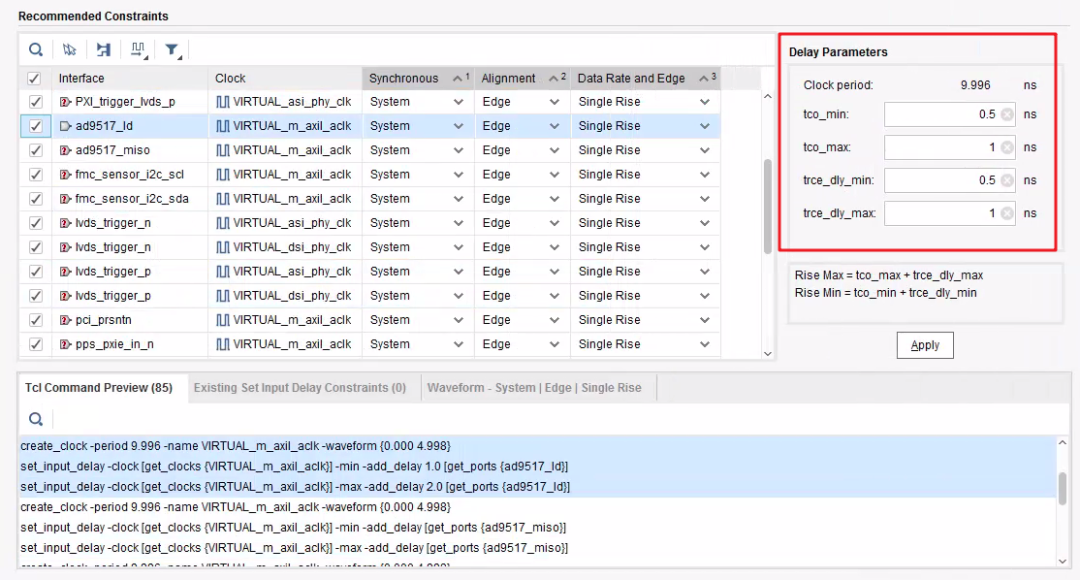

- 在不修改时钟特性的情况下针对I/O指定不同的jitter和latency

这个需求我们可以在Constraints Wizards中指定,简单又方便

image-20211206212729797

image-20211206212729797

在设置完成后,可以看到Tcl Command Preview中提示的约束指令。

审核编辑 :李倩

-

FPGA

+关注

关注

1634文章

21821浏览量

607550 -

虚拟时钟

+关注

关注

0文章

5浏览量

6617

原文标题:FPGA的虚拟时钟如何使用?

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

用TVP5150做得视频解码芯片然后过FPGA处理,有黑线怎么处理?

如果用FPGA采集AD1672,如何保障FPGA时钟同1672时钟一致?

请问TLV320AIC3254EVM-U 开发板程序丢失,怎么通过USB重新写入,程序从什么地方可以得到?

振动传感器用在什么地方

110配线架可用于什么地方?rj4模块化配线架可用于什么地方?

FPGA如何消除时钟抖动

数字电源模块用在什么地方

网络电话配线架用在什么地方

MAX13085EESA+与MAX13485EESA+的差异在什么地方?

FPGA开发过程中配置全局时钟需要注意哪些问题

FPGA的时钟电路结构原理

FPGA的虚拟时钟用于什么地方?

FPGA的虚拟时钟用于什么地方?

评论