使用 FPGA 的优势之一是能够实施经过验证的知识产权,以快速、自信地完成桥接功能。看看一个常见但复杂的接口 PCI Express,就可以证明这些好处。

与其前身外围组件互连 (PCI) 一样,PCI Express (PCIe) 正在成为一种无处不在的系统接口。与 PCI 不同,PCIe 采用 SERDES 接口为用户提供未来应用所需的可扩展性。随着系统带宽的增加,越来越多的应用正在转向基于 SERDES 的接口,例如 PCIe。过去,专用 IC (ASIC) 和专用标准产品 (ASSP) 通常用于实施下一代接口解决方案。ASIC 和 ASSP 是流行的选择,因为它们提供了低成本、低功耗的设计解决方案。

然而,几个新的 FPGA 系列为 PCIe 接口提供了有吸引力的选择。FPGA 提供了一个适应性强的平台,它没有 ASSP 的不灵活性,也没有 ASIC 通常相关的较长的交付周期和大量的非经常性工程成本。具有嵌入式 SERDES 的新一代 FPGA 以低成本、低功耗的串行接口解决方案为设计人员提供了极其丰富、高价值的可编程架构。相同的 FPGA 可用于支持各种串行协议,如 PCIe、GbE、SGMII、XAUI、Serial RapidIO 等,为多种设计提供单一 FPGA 平台。

PCIe 也正在成为控制平面应用程序的首选接口,取代旧的并行接口,如 PCI。新一代设备使用一个或多个 PCIe 链路。在大多数设备中,PCIe 内核被实现为 PCIe 端点。设计人员通常需要将这些设备连接到具有并行总线的上一代设备(例如具有并行总线接口的微处理器)。使用低成本、低功耗 FPGA 在 PCIe 和并行接口之间进行桥接可为设计人员提供解决此问题的灵活性,而不会超出其系统成本和功率预算。

设计挑战

随着设计人员从 PCI 迁移到 PCIe,协议的复杂性以及基于 SERDES 的设计所涉及的复杂性构成了重大挑战。幸运的是,FPGA 与全功能 PCIe IP 内核、参考设计、硬件评估板和相关演示相结合,有助于消除 PCIe 设计人员面临的陡峭学习曲线。FPGA 是基于 PCIe 的应用的理想平台。因为它们是可编程的,所以 FPGA 使设计人员能够灵活地在设计周期的后期解决设计问题,并加快周转时间。随着个别设计要求的发展,设计人员可以轻松更改或添加功能。FPGA 设计还允许设计人员进行更新以适应规范的变化,使他们能够在未来证明其设计不会过时。可编程平台使设计人员能够使用相同的 FPGA 来实现连接到各种其他 PCIe 芯片组的接口解决方案:端点、根复合体或交换机。设计人员可以在FPGA中集成系统所需的其他功能,减少板上元件的数量,进一步降低系统的总成本。

桥接接口

FPGA 为系统设计提供了极其灵活的可编程平台。包含 IP 内核、硬件平台、演示设计、驱动程序和软件的综合解决方案包使设计人员能够缩短开发周期,同时降低设计的复杂性。

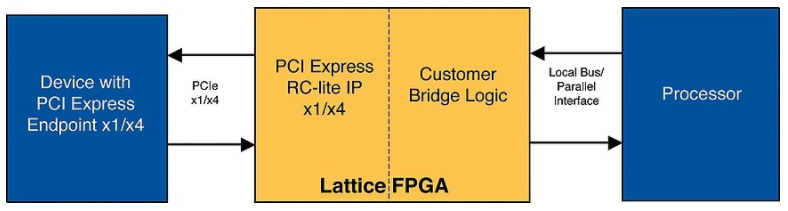

一个常见的设计要求是 PCIe 解决方案在 PCIe 串行接口(端点设备)和传统并行总线接口之间进行桥接,如图 1 所示。具有 PCIe 根复杂 IP 内核的 FPGA 为设计人员提供了实现所需的基本构建块这样的解决方案。或者,ASSP 和 ASIC 也可以实现此功能。然而,与 FPGA 不同,这些设备只能实现固定配置,无法更改以适应各种可用的并行总线接口。

图 1:具有 PCIe 根复杂 IP 内核的 FPGA 在 PCIe 串行接口和传统并行总线接口之间桥接。

另一方面,可编程 FPGA 平台使设计人员能够对其设计进行特定更改,以实现与其特定板上可用接口相匹配的特定桥接功能。设计人员还可以灵活地在单个 FPGA 中实现多个桥接或桥接的不同配置,从而减少板上的组件总数。FPGA 与 PCIe 根复杂 IP 核相结合,可以实现设计所需的多种其他桥接解决方案。

PCIe 根复合体

PCIe 端点作为上游设备运行,这是根复杂设备可以执行的功能。然而,就所使用的 FPGA 门而言,一个全功能的根复杂实现是相当昂贵的。相反,具有事务层功能子集的轻量级根复杂核心足以实现大多数桥接功能。

如图 1 所示,这座桥由两个基本组成部分组成。第一个块是 PCIe 根复合体(或 Root Complex-lite)IP 内核,它与 PCIe 端点设备接口。第二个块是连接到本地总线/并行接口的桥接逻辑。由于此实现是在可编程 FPGA 中实现的,因此设计人员可以根据特定接口需求灵活地定制设计。其他功能也可以集成到同一个 FPGA 中,从而消除板上的其他组件并降低总体材料成本。

实现更轻量级的 IP

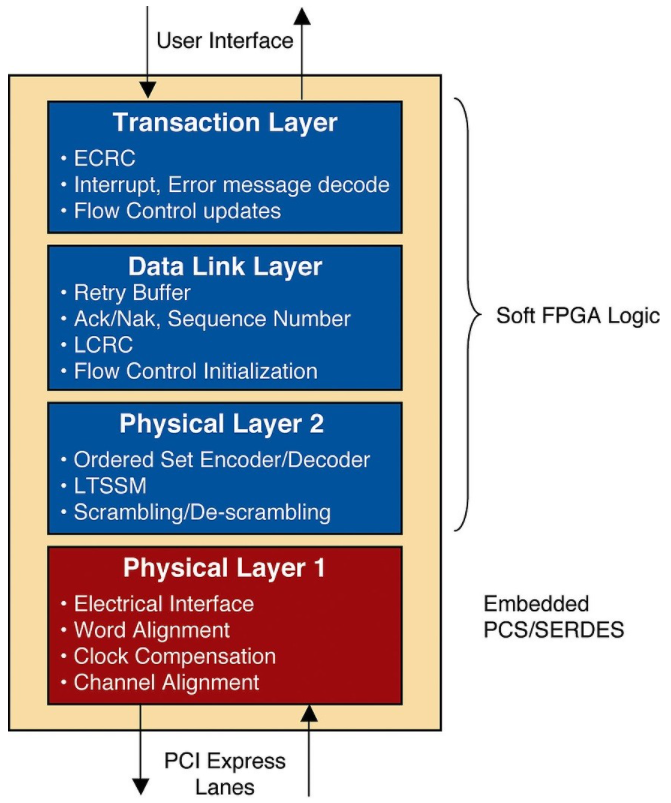

PCIe 是一个复杂的协议。提供功能齐全、经过充分验证的 PCIe IP 内核可显着降低设计复杂性。例如,莱迪思半导体的 PCIe Root Complex Lite (RC-lite) 内核实现了 x1 或 x4 根复合功能,主要用于 PCIe 桥接应用。如图 2 所示,所有 PCIe 层均作为嵌入式 ASIC 块和在 FPGA 中实现的 PCIe RC-lite 软 IP 内核的组合来实现。各种模块包括电 SERDES 接口、物理层、数据链路层和最小事务层,以支持实现 PCI Express 根复杂功能所需的协议栈。这种较轻的 IP 针对 PCIe 端点接口和并行本地总线接口之间的简单桥接应用进行了优化。

图 2: PCIe RC-lite IP 协议栈有助于降低 PCIe 桥接应用的设计复杂性。

在 LatticeECP2M 或 LatticeECP3 FPGA 中实现的 PCIe RC-lite IP 可实现低成本、低功耗的 PCIe 桥接应用,同时为设计人员提供定制桥接接口的灵活性。此外,PCIe 硬件评估板和各种参考设计、演示和软件驱动程序可帮助设计人员启动他们的 PCIe 设计并缩短上市时间。莱迪思还为设计人员提供了一个硬件评估板来测试 RC-lite IP 解决方案。设计人员可以在部署之前完成互操作性并验证这些解决方案的系统级功能,从而节省通常与设计后调试和性能增强相关的时间和成本。

简化桥接复杂性

PCIe 设计对设计人员提出了重大挑战。对接口的要求各不相同,具体取决于 PCIe 设备是否必须连接到另一个端点、根联合体或交换机。此外,设计通常需要一个 PCIe 端点设备和另一个具有并行总线接口的设备之间的连接。

设计人员可以在低成本、低功耗的 FPGA 平台中实现这些功能,同时保留灵活可编程架构的所有优势。在 FPGA 中使用 PCIe 根复杂 IP 功能提供了实现这些桥接功能的理想平台。

审核编辑:郭婷

-

FPGA

+关注

关注

1625文章

21644浏览量

601401 -

接口

+关注

关注

33文章

8471浏览量

150759 -

PCIe

+关注

关注

15文章

1213浏览量

82383

发布评论请先 登录

相关推荐

通过PLX PCI9080桥接芯片实现TMS320C6000扩展总线与PCI总线的接口

KeyStone设备的PCI Express (PCle)常见问题

使用TI PCI-Express Gen5.0转接驱动器进行眼图扫描

XIO2001 PCI Express至PCI总线转换桥接器数据表

在FPGA中实施PCI Express桥接解决方案

在FPGA中实施PCI Express桥接解决方案

评论