2纳米芯片什么时候上市

本月17日消息,台积电在2022年北美技术论坛会上,推出了2纳米芯片的制程工艺,并表示2纳米芯片将在2025年量产。

这也就意味着台积电将在2025年开始将使用2纳米制程工艺开始生产芯片,鉴于芯片的生产周期,2纳米芯片还要晚一点才能进行商用,大约在2025年底或2026年才能面世。

2纳米芯片的意义

国际商业机器公司(IBM)公司曾表示,全球首创的2纳米芯片制造技术可以在7纳米芯片速度上提升多达45%,能源效率方面提升多达75%。

目前多数电子产品使用的都是7纳米芯片,虽然距离2纳米芯片制造技术仍然有很长的路要走,但2纳米芯片的技术发展已经成为了新的趋势。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

458文章

51479浏览量

429277 -

芯片制造

+关注

关注

10文章

640浏览量

29003

发布评论请先 登录

相关推荐

纳米压印光刻技术应用在即,能否掀起芯片制造革命?

压印光刻技术NIL在这条赛道上备受关注,是最有机会率先应用落地的技术路线。 今年早些时候,根据英国金融时报的报道,负责监督新型光刻机开发的佳能高管武石洋明在接受采访时称,采用纳米压印技术的佳能光刻设备FPA-1200NZ2C

Rapidus携手博通推进2纳米芯片量产

近日,据日媒报道,日本半导体新兴企业Rapidus正与全球知名芯片制造商博通(Broadcom)展开合作,共同致力于2纳米尖端芯片的量产。Rapidus计划在今年6月向博通提供试产

Rapidus或携手博通,6月提供2纳米芯片原型

近日,有消息称日本半导体制造商Rapidus正与博通展开合作,计划在今年6月向博通提供其2纳米制程芯片原型。这一合作标志着Rapidus在先进制程技术领域的又一重要进展。 Rapidus作为日本

OptiFDTD应用:用于光纤入波导耦合的硅纳米锥仿真

介绍

在高约束芯片上与亚微米波导上耦合光的两种主要方法是光栅或锥形耦合器。[1]

耦合器由高折射率比材料组成,是基于具有纳米尺寸尖端的短锥形。[2]

锥形耦合器实际上是光纤和亚微米波导之间的紧凑模式

发表于 01-08 08:51

英伟达、高通或转单三星2纳米工艺

近日,据SamMobile的最新消息,英伟达和高通两大芯片巨头正在考虑对其2纳米工艺芯片的生产策略进行调整。具体来说,这两家公司正在评估将部分原计划在台积电生产的

高通明年骁龙8 Elite 2芯片全数交由台积电代工

芯片代工伙伴。上一次高通选择三星代工,还要追溯到2021年的骁龙8第一代芯片,当时采用的是三星的4纳米制程。 据悉,台积电将为高通生产骁龙8 Elite 2

7纳米工艺面临的各种挑战与解决方案

本文介绍了7纳米工艺面临的各种挑战与解决方案。 一、什么是7纳米工艺? 在谈论7纳米工艺之前,我们先了解一下“纳米”是什么意思。纳米(nm)

碳纳米管的结构与特性解析 碳纳米管在能源储存中的应用

构成的二维材料)卷曲而成的圆柱形结构。碳纳米管的直径通常在几纳米到几十纳米之间,长度可以达到微米级别。 2. 碳原子排列 碳纳米管的壁由六边

碳纳米管的导电性能介绍 碳纳米管如何提高材料强度

管。这些不同的结构类型影响了碳纳米管的电子性质,包括导电性。 2. 导电性能 碳纳米管具有优异的导电性能,这主要得益于其特殊的电子结构。在理想状态下,碳纳米管可以表现为金属或半导体,这

OptiFDTD应用:用于光纤入波导耦合的硅纳米锥仿真

介绍

在高约束芯片上与亚微米波导上耦合光的两种主要方法是光栅或锥形耦合器。[1]

耦合器由高折射率比材料组成,是基于具有纳米尺寸尖端的短锥形。[2]

锥形耦合器实际上是光纤和亚微米波导之间的紧凑模式

发表于 12-11 11:27

胜科纳米IPO提交注册,芯片检测“全科医院”上市在即

近日,上交所官网披露了胜科纳米(苏州)股份有限公司(以下简称“胜科纳米”)的招股说明书(注册稿)等相关文件,标志着胜科纳米IPO进程再次取得重要进展。从11月22日过会到11月29日提交注册,仅隔7天时间,胜科

日本拟为Rapidus提供贷款担保,助力2纳米芯片制造

据悉,Rapidus计划于2027年前在北海道岛北部建立尖端的2纳米芯片生产基地,总投资额高达5万亿日元(约合318亿美元)。

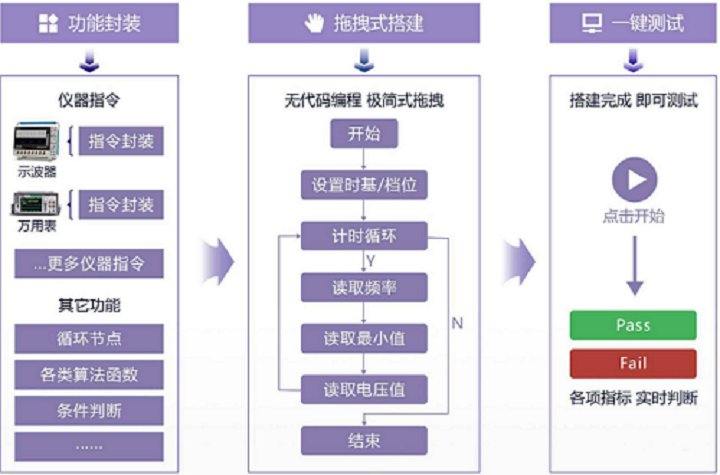

纳米软件自动化测试合作:4644芯片与VPX模块测试

近日,纳米软件与西安广勤电子技术有限公司就4644电源芯片自动化测试和VPX电源自动化测试达成战略合作。在双方进行深入探讨后,纳米软件为广勤电子公司提供了高效、专业的测试解决方案,助推该公司自动化测试的发展。

三星半导体将其“第二代3纳米”工艺正式更名为“2纳米”!

近期,科技巨头三星半导体做出了一个引人注目的决策:将其“第二代3纳米”工艺正式更名为“2纳米”。

2纳米芯片什么时候上市_2纳米芯片的意义

2纳米芯片什么时候上市_2纳米芯片的意义

评论