Q1

关于DFX的问题: 正在尝试为Xilinx Github下的PYNQ_Composable_Pipeline工程的PR_0区域添加新的RM(Reconfigurable Module),让这个动态函数区域支持更多函数,但是在implement这个config对应的的child_2_impl_1时遇到了以下报错:

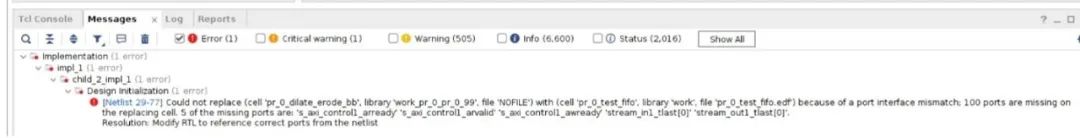

[Netlist 29-77] Could not replace (cell 'pr_0_dilate_erode_bb', library 'work_pr_0_pr_0_99', file 'NOFILE') with (cell 'pr_0_test_fifo', library 'work', file 'pr_0_test_fifo.edf') because of a port interface mismatch; 100 ports are missing on the replacing cell. 5 of the missing ports are: 's_axi_control1_arready' 's_axi_control1_arvalid' 's_axi_control1_awready' 'stream_in1_tlast[0]' 'stream_out1_tlast[0]'.

Resolution: Modify RTL to reference correct ports from the netlist

但没能找到在Block Diagram的PR中添加新的.bd文件作为RM的教程或案例。

错误流程:

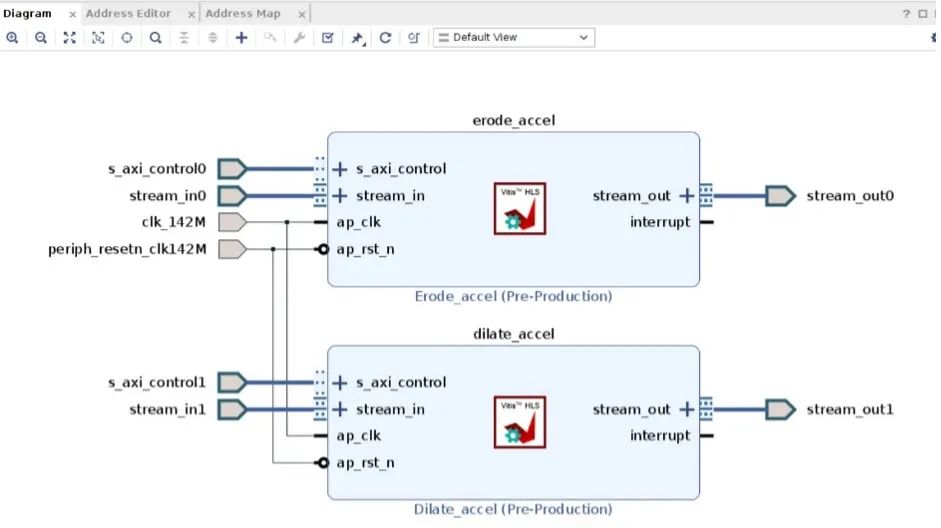

pr_0_dilate_erode.bd是工程原本含有的RM

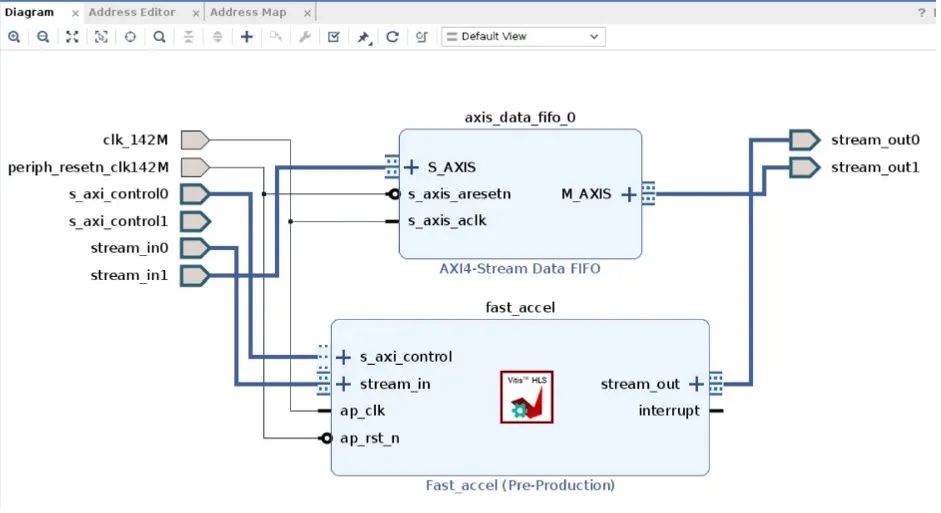

pr_0_test_fifo.bd是新添加的RM

在make原始工程后进行了以下操作:

新建了pr_0_test_fifo.bd

将pr_0_dilate_erode.bd的接口复制到了pr_0_test_fifo.bd中

仿照pr_0_dilate_erode.bd一样在pr_0_test_fifo.bd中放置了两个IP并完成连线

仿照pr_0_dilate_erode.bd配置各口的时钟、分配bd地址,validate与save bd_design

在DFX wizard中添加pr_0_test_fifo为RM与完成其他配置

在运行对应的child_2_impl_1后,pr_0_test_fifo_synth_1、synth_1与impl_1正常,但在child_2_impl_1处出现上述错误。

A:建议按以下步骤操作,可以参考一下:

1. 从"Partition Definitions" Tab 打开已有RM的BD

2. 执行"write_bd_tcl bd.tcl", 从生成的bd.tcl中直接copy接口相关的内容到新建的BD中,同时自己在新BD中做Block连接

3. 从DFX Wizard中为RP创建新的RM,内容就是新建的BD,也可以参考以下命令:

create_reconfig_module -name $pr_0_hongh -partition_def pr_0 -define_from $pr_0_hongh

4. 设置新的Configuration,执行这个child run的impl

审核编辑 :李倩

-

Block

+关注

关注

0文章

26浏览量

14735 -

GitHub

+关注

关注

3文章

474浏览量

16658

原文标题:本周一问 | 如何在Block diagram中为PR区域添加.bd格式的Reconfigurable Module

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

探索BD仓储物流效能提升的秘诀

TMUXHS4212 MUX与DS160PR421或DS160PR412 Redriver在PCIe GEN 4应用中的比较

AFE032系数滤波器的设置格式是什么,如何设置?

如何在自己的程序中启用AT模块?

如何在引脚映射器文件中添加TC322?

如何在ModelSim中添加Xilinx仿真库

abb机器人系统如何添加选项

如何在stvd中添加被人的库使其编译通过,正常调用?

如何在Cubemx中添加所有的外设头文件?

鸿蒙OS实战:【module的使用】

如何在Block diagram中为PR区域添加.bd格式的Reconfigurable Module

如何在Block diagram中为PR区域添加.bd格式的Reconfigurable Module

评论