在FPGA的HR BANK上供电3.3V,先就其差分端口而言,LVDS电平以及LVDS25电平能否约束到这个BANK上呢?

解决这个问题前,先了解下

1、什么是HR Bank以及HP bank:

Xilinx的7系列FPGA有两种IO Bank:HP(High Performace)和HR(High Range)。HP(high-performance)I/O banks的设计目的是为了获取更高的Memory及chip-to-chip间的传输速率;而HR(high-range)I/O banks的设计目的是为了更宽的I/O电平标准。两种BANK的IO口电压不同,其中HR I/O Banks的VCCO电压最大为3.3V,HP I/O banks的VCCO电压最大为1.8V。特别是初次使用7系列时,在硬件设计中特别要注意它们I/O口的最大工作电压,一不注意就会把电压搞错,导致FPGA不能正常工作。

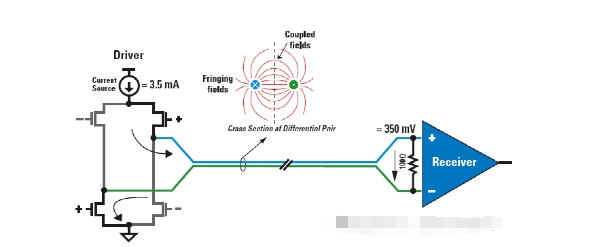

2、HR和HP banks的LVDS电平

当两个banks的I/O口作为LVDS电平时,HR banks的I/O电压VCCO只能为2.5V,HP banks的I/O口电压为1.8V。两个banks支持LVDS的标准不同,HR I/O banks的I/O只能分配LVDS_25标准,HP分配为LVDS标准。

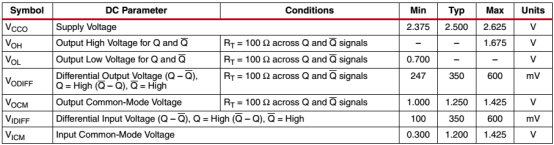

LVDS_25的直流特性如下表所示。

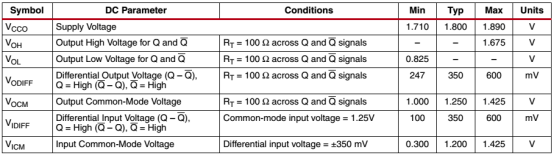

LVDS的直流特性如下表所示。

xilinx 7系列芯片不再支持LVDS33电平,在VCCO电压为3.3V的情况下无法使用LVDS25接口。

有些设计者想通过在软件中配置为LVDS25,实际供电3.3V来实现LVDS33也是无效的,原因是xilinx 7系列芯片在IO配置方面增加了过压保护,因而无法通过欺骗综合软件的方式强行配置IO,具体参见

7-Series SelectIO Resources Guide, page 100, Note 2 states:

"if the voltage exceeds 2.85V, the outputs will be in a high-Z state. The device should always be operated within the recommended operating range as specified in the 7 series FPGA data sheets."

虽然在VCCO为3.3V情况下无法输出LVDS25,但可以作为输入进行使用,具体参见AR#43989 https://www.xilinx.com/support/answers/43989.html

即使VCCO电平不是1.8V,在HP I / O bank中也可以使用LVDS输入。LVDS输出(因此双向LVDS)只能用于1.8V供电的组。

同样,即使VCCO电平不是2.5V,也可以在HR I / O bank中使用LVDS_25输入。LVDS_25输出(因此双向LVDS_25)只能用于2.5V供电的bank。

查了上述说法之后,我们自己试验下:

实验验证:

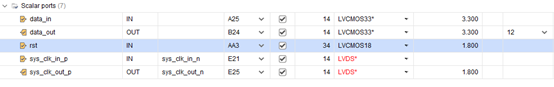

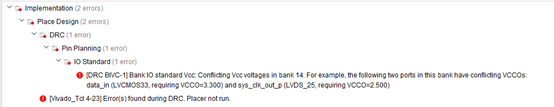

Bank14为HR Bank,差分输入以及差分输出使用LVDS电平:

提示说明,LVDS电平不支持HRbank。

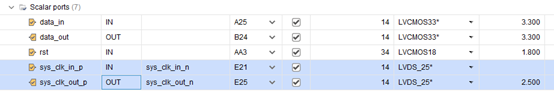

差分输入以及差分输出使用LVDS25电平:

提示VCCOs矛盾,输出差分时钟sys_clk_out_p,要求VCCO=2.5V,但对输入并没有这种要求。

验证了:

即使VCCO电平不是1.8V,在HP I / O bank中也可以使用LVDS输入。LVDS输出(因此双向LVDS)只能用于1.8V供电的组。

同样,即使VCCO电平不是2.5V,也可以在HR I / O bank中使用LVDS_25输入。LVDS_25输出(因此双向LVDS_25)只能用于2.5V供电的bank。

审核编辑 :李倩

-

FPGA

+关注

关注

1629文章

21729浏览量

603049 -

Xilinx

+关注

关注

71文章

2167浏览量

121323 -

电平

+关注

关注

5文章

360浏览量

39886

原文标题:FPGA学习-FPGA的LVDS电平以及LVDS25电平能在HR Bank上使用吗?

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

能否用LMH0341将HD-SDI转成LVDS接口,再用DS90CR288A将LVDS转成RGB?

使用DS90CF383输出的LVDS_data在一个周期中低电平时,会有电平翻转,什么原因?

请问sn65lvds048a能否接收300MHz的2.5V LVDS电平?

ADS5404可以使用LVDS或LVPECL的时钟源头吗?

求助,关于ads4125在LVDS模式下输出信号的波形问题求解

请问DAC3161的DACCLK能否支持LVDS电平输入吗?

当ADC3663的LVDS输出给到ZYNQ-7000的LVDS接收这两者之间可以直连吗?

LVDS Serdes接收器SN65LVDS94LVDS数据表

LVDS Serdes接收器SN65LVDS96LVDS数据表

LVDS-SERDES发射机SN65LVDS93LVDS数据表

LVDS-SERDES发射机SN65LVDS95LVDS数据表

LVDS电平以及LVDS25电平能否约束到这个BANK上呢?

LVDS电平以及LVDS25电平能否约束到这个BANK上呢?

评论