前言近两年,随着国家对信息技术应用创新日益重视,作为芯片行业的重要成员,许多国产CPU公司有了长足的发展。无论是面对芯片紧缺、断供的严峻形式,还是工业软件“卡脖子”的窘境,都无一例外要求我们加大国产芯片、工业软件的研发力度和速度。包括龙芯、飞腾、海光、兆芯在内的众多国内一线CPU芯片设计公司,正在为全力打造“中国芯”而不懈努力。在这个进程中,急需一种快速的方法,检查芯片设计和应用中的信号完整性、电源完整性问题,从而提高CPU芯片的设计迭代和投产效率。

国产CPU市场概况

CPU处理器主要面向的市场有PC、服务器、嵌入式、智能手机、安防监控、汽车电子、视频和多媒体处理。目前,中国仍是全球CPU最大的消费市场,下游需求旺盛,随着国际供应链断裂和信息安全风险加剧,我国对国产CPU领域的政策支持力度持续提高,国内CPU正在加快发展步伐。

国产CPU中以X86架构代表的企业有兆芯、海光。其中,兆芯是来自威盛的x86技术,架构技术和性能相对Intel、AMD有所差异;海光获得的是AMD 14nm Zen架构的IP授权。ARM架构的代表还有华为、飞腾。此外,MIPS架构的代表有龙芯。

从国产CPU的工艺制程看,16nm工艺是比较主流的先进工艺,采用7nm工艺的只有华为鲲鹏920,但其处于暂停生产状态,而兆芯新一代7nm工艺芯片尚未正式发布,其它厂商的规划还不明确。在政企市场,国产CPU受到重视,得到快速推进,而在消费级市场还只是刚开始。

CPU应用中的挑战

1. 信号完整性、电源完整性挑战

在CPU中,通常采取优化多核心、高速缓存、内存、IO等接口的方式,以达到提升运算速度并降低功耗的目的。但在这一过程中,不可避免的会存在信号完整性和电源完整性的问题,而且越是使用先进工艺节点,其挑战就越严峻。无论是对于传统封装还是先进封装,信号的可靠程度与电源的稳定性都是衡量芯片质量的标准。因此,在设计中必须面对这两个老生常谈的问题。除了优化设计外,如何加快设计迭代速度也是设计中的重要考量因素。

2. 先进封装带来挑战

CPU的封装,从早期的QPF、FCBGA到现在的先进封装,有了更多的变化。对于CPU芯片来说,随着工艺的发展,工程师利用硅载板或者TSV结构设计的先进封装,如何能够准确高效的处理好多个信号之间的串扰问题,也是设计的重要一环。

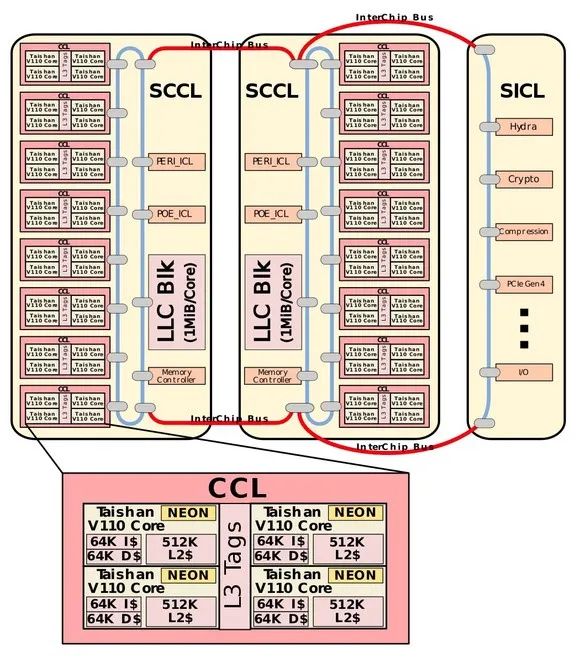

以鲲鹏920为例:下图是三颗裸芯组成的64核芯片,其中左边两颗为计算DIE,每颗含32个TSV110核,由4个核组成一个簇,8个簇挂在一个环状总线上,32MB的L3作为一个节点也挂在环上,同样的存控也作为一个节点挂在环上。三颗裸芯之间由 chip间总线实现互连。复杂的工艺以及众多的信号线需要一个强大计算能力的仿真工具,完成对信号和串扰的评估。

图1 鲲鹏920内部架构图

3. PCB板级协同挑战

对于CPU芯片来说,在设计配套CPU的PCB测试版、demo板时,也需要进行相关的仿真工作。一方面芯片的高速接口需要PCB的协同设计,另一方面,PCB作为CPU的配套使用载体,它的性能也是直接影响整体链路性能是否完善的关键因素。对于高速PCB来说,就算是经验丰富的工程师,在设计高速链路的时候,仍需要对过孔、焊盘等细节进行优化。若有SerDes或者DDR的走线,对其串扰的分析就更不可避免。

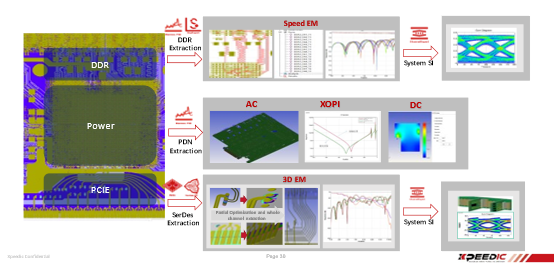

芯和CPU应用中的SI/PI解决方案芯和半导体针对CPU应用中的封装以及PCB的SI/PI提供了完整的解决方案。对于传统型封装的QFN、QFP或者FCBGA,工程师可以利用芯和半导体的工具,针对其金线、Bump等结构进行分析;对于3DIC、Chiplets或者TSV结构的先进封装,设计人员同样可以利用工具进行设计-分析的一站式流程;而对于PCB板级,也可以根据低频-高频不同的应用场景进行相应的算法切换并进行分析。

图2 CPU应用中的SI/PI解决方案

1. 信号完整性、电源完整性分析

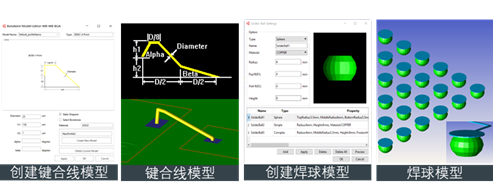

芯和半导体的Hermes 3D、Hermes PSI提供了针对CPU封装的SI及PI的解决方案。Hermes 3D是一款三维全波电磁场仿真工具,它可以支持主流ECAD工具输出的版图文件,导入生成相应的3D模型。它同时提供了自动切割版图和自动添加端口的功能,大幅提高了工程师的建模效率。Hermes 3D采用自适应网格剖分技术和有限元算法,可以确保对任意三维结构在任意频段都具备较高的求解精度。

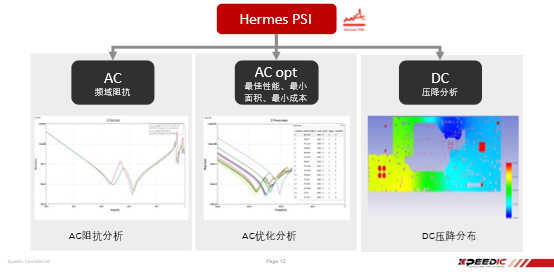

Hermes PSI 是一款专注封装与板级电源完整性分析的工具,包括直流压降分析和交流阻抗分析两大功能模块。在设计中,直流压降分析可以帮助工程师快速分析电源的直流效应,并检查直流压降、电流趋势和电流密度分布,优化电源路径中可能存在的瓶颈。交流阻抗分析可以计算封装基板和PCB之间的PDN阻抗,并自动优化去耦电容。

图3 Hermes3D 帮助建模与SI仿真

图4 HermesPSI帮助建模与PI仿真

2.先进封装仿真建模

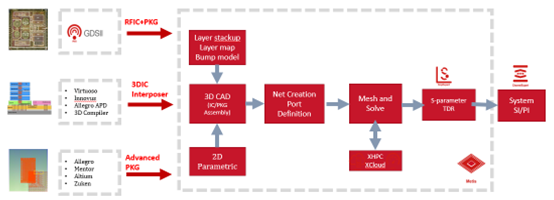

芯和半导体的Metis工具提供了专注于先进封装的建模和仿真流程,针对目前最为火热的Chiplets、TSV、interposer等结构,有着明显的建模和仿真优势。工程师可以利用它突破传统封装仿真技术的极限,同时容纳超大规模的信号数量,并利用矩阵级别的集群分布式计算,提高计算效率的同时,降低硬件资源消耗,真正达到快速、节省的跨尺度仿真效果。工程师在初次使用时,可以通过3DIC和先进封装两种分析流程向导,快速完成联合仿真设置。利用内置的Speed、Balanced和Accuracy三种仿真模式,满足工程师不同设计阶段对精度和速度要求。

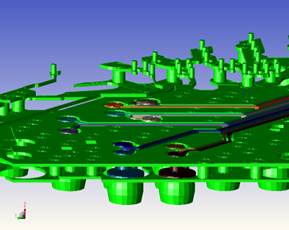

图5 Metis提供先进封装仿真流程

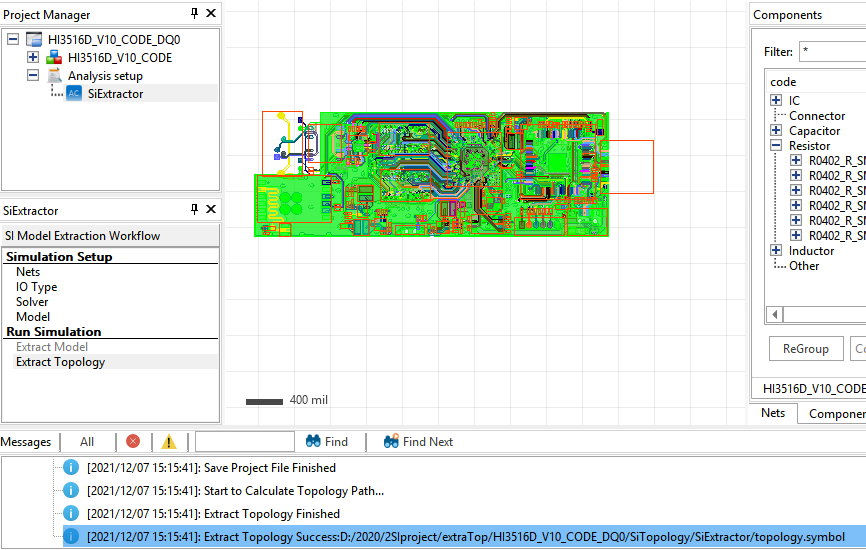

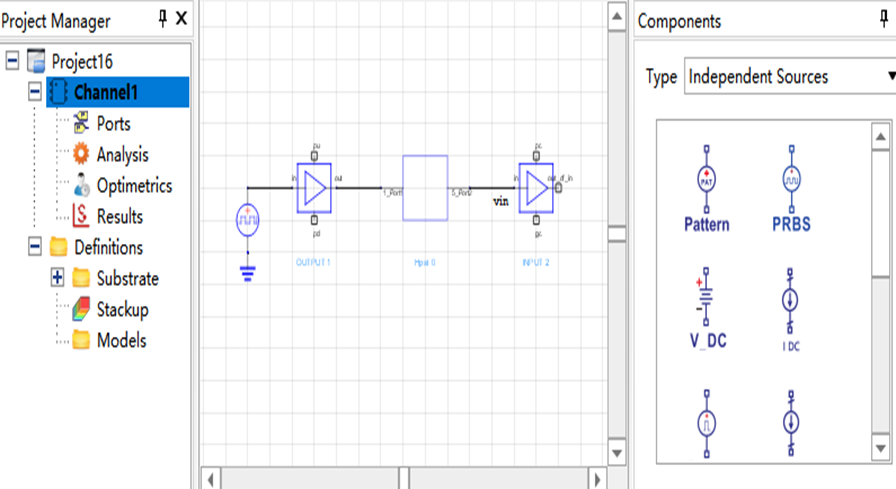

3.PCB板级协同仿真

在CPU设计时,PCB和封装的协同设计同样重要。工程师不但可以通过Hermes工具进行封装设计仿真,也可以进行PCB板级设计的仿真。设计人员利用Hermes PSI的拓扑功能,可以快速进行封装和PCB板级的协同仿真。此外还可以进行电、热的协同仿真,让工程师可以直观的了解现有设计中芯片的供电质量如何,电流密度是否满足设计规范要求。根据这些仿真结果,让工程师可以调整优化现有封装设计,从而大大加快产品的设计周期,提高产品的设计质量。

图6 HermesPSI拓扑功能帮助仿真设计

总结本文首先从国内CPU的发展现状切入,讲述了目前CPU研发现状以及市场现状,引出CPU应用中的挑战。无论是传统型封装、先进封装还是PCB板级,CPU在设计时都会存在信号完整性、电源完整性的问题。芯和半导体的Hermes 3D、Hermes PSI可以进行信号完整性、电源完整性的分析;Metis工具可以帮助工程师进行先进封装的仿真;同时它们也都支持PCB板级的协同仿真,可以很好的从根本上解决CPU应用中的仿真难题。

原文标题:【解决方案】CPU应用中的仿真解决方案

文章出处:【微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

pcb

+关注

关注

4329文章

23188浏览量

400562 -

cpu

+关注

关注

68文章

10922浏览量

213283 -

仿真

+关注

关注

50文章

4134浏览量

134126 -

芯和半导体

+关注

关注

0文章

111浏览量

31501

原文标题:【解决方案】CPU应用中的仿真解决方案

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CPU\GPU引领,国产AI PC进阶

CPU怎么降频 bios中如何把cpu调低频率

FPGA+GPU+CPU国产化人工智能平台

AMD第三季度CPU出货量激增,挑战英特尔市场地位

英伟达计划2025年推出基于Arm架构的消费级CPU,挑战英特尔和AMD

服务器cpu和台式机cpu区别

双核cpu和单核cpu的区别

CPU的定义和功能

什么是CPU缓存?它有哪些作用?

中国加速本土技术采购,国产CPU与操作系统迎来机遇

CPU中寄存器的用途

国产CPU和操作系统被纳入政府采购清单:加速换国产OS

国产CPU市场概况 CPU应用中的挑战

国产CPU市场概况 CPU应用中的挑战

评论