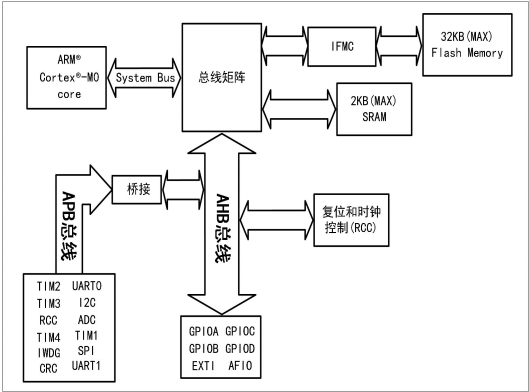

1存储器和总线构架

1.1系统构架

l一个驱动单元

nCortex™-M0内核系统总线(S-bus)

l四个被动单元

n内部SRAM

n内部Flash闪存存储器

nAHB所连接的所有外设

nAHB到APB的桥,它连接的所有APB设备

1.1.1系统总线

此总线连接Cortex™-M0内核的系统总线(外设总线)到总线矩阵,总线矩阵协调内核与外部总线的访问。

1.1.2 AHB/APB桥(APB)

“AHB/APB桥”在AHB和APB总线间提供同步连接。AHB和APB的操作速度均与系统时钟SYS_CLK同步。

连接到每个桥的不同外设的地址映射请参考表1-1。在每一次复位过程当中,除SRAM以外的所有外设都被关闭。

注意:对AHB或APB总线上的寄存器进行8位或者16位操作时,由于数据字节以小端格式存放在存储器中,故有:

1.读操作:该操作会被自动转换成32位的读,对应的数据将按照小端格式被存储在中间变量;

2.写操作:总线和桥会自动将8位或者16位的写入数据扩展,并将缺失的高位补0,以配合

32位的向量。

1.2存储器组织

程序存储器、数据存储器、寄存器和输入输出端口被组织在同一个4GB的线性地址空间内。

数据字节以小端格式存放在存储器中。一个字里的最低地址字节被认为是该字的最低有效字节,而最高地址字节是最高有效字节。

1.3嵌入式SRAM

PT32x00x内置最大2K字节的SRAM。它可以以字节、半字(16位)或全字(32位)访问。SRAM的起始地址是0x2000 0000。

1.4嵌入式Flash闪存

PT32x00x内置的闪存存储器可以用于在线编程(ICP),在线编程(In-Circuit Programming–ICP)方式用于更新闪存存储器的全部内容,它通过SWD协议或系统加载程序(Bootloader)下载

用户应用程序到微控制器中。ICP是一种快速有效的编程方法,消除了封装和管座的困扰。

高性能的闪存模块有以下的主要特性:

最大32K字节的闪存存储器结构,下面罗列存储器的组成部分:

l主程序区

lBootloader区

l用户配置区

通过片内闪存控制器IFMC可以便捷的控制Flash闪存,有关IFMC的详细信息,请参考”16片内闪存控制器(IFMC)”。

注意:PT32x00x不支持中断向量表重映射,故不支持IAP应用。

1.5启动配置

PT32x00x支持两种启动模式:

l从主程序区启动

l从Bootloader区启动

这两种启动模式都基于Flash片内闪存,通过特定的程序配置以实现不同的启动模式,而无需外部硬件的介入。

注意:默认从主程序区启动,关于从Bootloader 区启动的详细信息,请参考”16.3.6系统启动配置”

审核编辑:汤梓红

-

存储器

+关注

关注

38文章

7494浏览量

163909 -

内核

+关注

关注

3文章

1373浏览量

40308 -

sram

+关注

关注

6文章

768浏览量

114709 -

总线

+关注

关注

10文章

2888浏览量

88130

发布评论请先 登录

相关推荐

TMS320C672x DSP外部存储器接口(EMIF)用户指南

什么是ROM存储器的定义

使用SD Flash为TMS320C28x器件编程外部非易失性存储器

内存储器分为随机存储器和什么

PLC主要使用的存储器类型

内部存储器有哪些

ram存储器和rom存储器的区别是什么

EEPROM存储器如何加密

mcast发送中设置dst[6] = {0x01, 0x00, 0x5E, 0x00, 0x00, 0x00}; 这是为什么?

内存储器与外存储器的主要区别

TPS65296-完整 LPDDR4/LPDDR4X存储器电源解决方案数据表

浅谈存储器层次结构

PT32x00x存储器和总线构架说明

PT32x00x存储器和总线构架说明

评论