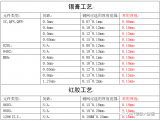

电源管理芯片广泛应用于板级电源系统中,包括控制器和功率MOSFET。但对于大电流电源管理芯片,基于不同半导体工艺的技术特点,即控制器和MOSFET所需要工艺的差别,可能无法使用同一半导体制程把两者集成到同一晶圆(Wafer)上面。因而只能采用multiple-die的结构, 称为多芯片封装 (MCM)加倒装法 (Flip-chip) 的封装形式,从而导致焊盘outline不够对称。如果SMA工序不能完全依照芯片手册的焊盘及钢网的尺寸要求(有些客户可能会有自己默认的CAD和SMA规则),可能会出现焊锡的厚度不足或不均匀。这样贴装的芯片的引脚在长期运行后(对应板级可靠性测试BLR,JESD22-A104)由于板子的翘曲形变导致引脚开裂或短路并使得芯片功能异常甚至损坏。因此正确理解和遵守芯片的焊盘和钢网的尺寸规则,并能针对性的提前做出适当的优化,对于提升SMA 工艺的良率和芯片的工作寿命,具有重要的意义。

芯片的引脚尺寸(footprint)

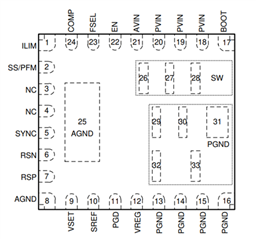

芯片数据手册会标注芯片的引脚尺寸(footprint),如下Figure 1所示。该芯片的引脚在水平和垂直方向上都存在不对称的现象,而且在垂直方向上,这一情况更明显:Pin25 AGND 尺寸比较大,而PIN26-30 的尺寸都比较小且分散。那么由于左右侧的不对称,如果不按照该产品要求的钢网和焊锡厚度,就可能导致

左右侧焊锡厚度不均匀,局部焊锡厚度不足,加之PCB,焊锡,PAD和芯片有不同的热膨胀系数,在温循时的受力就会有差别,容易造成焊锡开裂的现象。

相邻IO由于芯片位置不够水平,焊锡受力不均匀,可能会被挤压流向相邻IO,有短路的风险

Figure 1:TPS542A52 芯片顶视图(左)和芯片的引脚尺寸图(右)

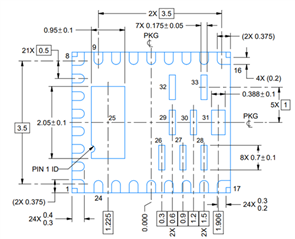

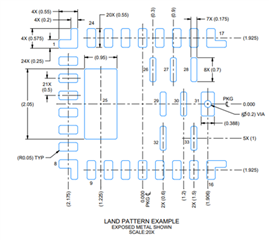

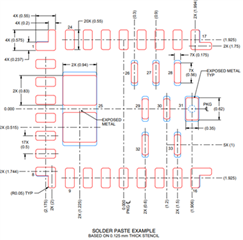

芯片的焊盘尺寸(land pattern) 和钢网尺寸

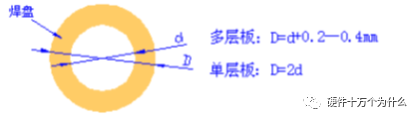

芯片在PCB板上的焊盘尺寸一般大于芯片尺寸,以便承接芯片在PCB板上。钢网(solder stencil) 开窗,比焊盘相当或略小。

Figure 2:TPS542A52 焊盘(land pattern)顶视图(左)和钢网(solder stencil)顶视图(右)

不同焊盘尺寸和钢网厚度尺寸对焊锡厚度和均匀度的影响(TPS542A52)

在实际应用中,芯片客户的CAD 工程师在给供应商的芯片建立CAD 模型时,基于自身SMT 工艺产线精度和经验,有一套默认的CAD rule,因而可能不会完全遵照TI 产品手册推荐的尺寸。对于大多数对称的封装形式如QFP,BGA,LGA等,由于焊盘是对称的,即使不完全按照供应商推荐的焊盘钢网尺寸,焊锡厚度一般也是均匀的。但对于非标准封装的电源芯片,如FLIP-CHIP QFN, 由于功率部分占据较大的面积,但只有VIN/SW/GND 几个IO口,而控制部分面积小但又有很多IO口,因此管脚的分布设计就容易出现不对称的引脚。因此不同的焊盘尺寸和钢网尺寸,就会体现出完全不同的引脚焊接质量和长期可靠性。

如下表Table 1是TPS542A52在不同焊盘和钢网下的焊接质量(焊锡厚度和均匀度)和温度循环测试后的引脚剖面图。

Table 1

| Unit | Land pattern | Solder stencil | Stencil thickness(um)(3) | Solder standoff(µm) |

Imbalance (µm) |

Pin short risk (solder bridge) due to imbalance |

Solder Crack @thermal cycling JESD22-A104 |

||

| PIN1 | PIN17 | ||||||||

| A | 1 | 客户自定义(1) | 客户自定义(2) | 125 | 64.1 | 44.1 | 20 | YES | Yes |

| B | 1 | TI | TI | 150 | 135 | 97 | 38 | YES | No |

| 2 | TI | TI | 150 | 92 | 49 | 43 | No | No | |

| 3 | TI | TI | 150 | 112 | 72 | 40 | No | No | |

| 4 | TI | TI | 150 | 113 | 70 | 43 | No | No | |

| 5 | TI | TI | 150 | 120 | 70 | 50 | No | No | |

| 6 | TI | TI | 150 | 112 | 70 | 42 | No | No | |

| C | 1 | TI | TI | 125 | 90 | 90 | 0 | No | No |

| 2 | TI | TI | 125 | 75 | 75 | 0 | No | No | |

| 3 | TI | TI | 125 | 75 | 83 | 8 | No | No | |

| 4 | TI | TI | 125 | 75 | 75 | 0 | No | No |

(1) 焊盘尺寸相比TI 偏大

(2) 钢网开口尺寸相比TI 偏小

(3) TI推荐125um 钢网厚度

A 焊盘尺寸偏大,钢网开创较小并且没有给PIN 25(GND)开两个窗口

焊锡厚度不足,焊锡开裂

整体焊锡量不足,因为钢网开口小于TI推荐且焊盘尺寸偏大,导致引脚下的焊锡被摊开,流向外部裸露的焊盘上。温度循环后,焊锡由于厚度不足导致容易开裂,引起芯片引脚开路导致损坏。

芯片倾斜

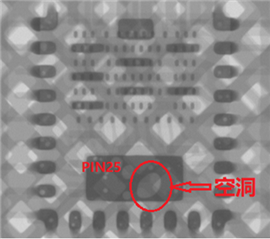

由于没有在PIN25 开多个窗口,导致PIN25焊锡中有较多的空洞(Void)。如下图3所示。

图 3 GroupA Unit 1 的PIN25 的焊锡空洞

B 焊盘和钢网尺寸都符合TI 要求,但钢网厚度偏厚并且没有给PIN 25(GND)开两个窗口

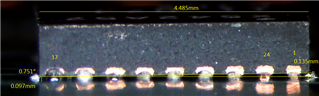

为了解决焊锡厚度不足的问题,有的客户会直接增加钢网厚度。焊锡厚度足够厚(>60um), 不会出现solder crack的问题。但焊接水平方向的倾斜仍然存在短路风险。如下图4所示。

焊锡太厚

仍然不均匀,左侧存在solder bridge导致短路的风险。

图 4 GroupB Unit 2 的剖面图

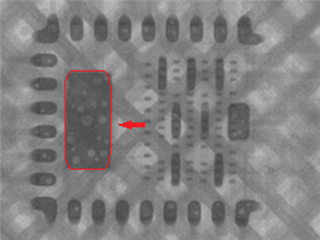

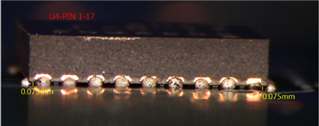

C焊盘和钢网尺寸及开口都符合TI要求,钢网厚度也符合

焊锡厚度均匀,且大于60um,PIN25下焊锡的空洞(void)也较小。

图 5 Group C Unit 4 的X-ray顶视图和剖面图

总结

对于非对称footprint的芯片,建议客户一定要按照TI推荐的焊盘和钢网尺寸进行设计。芯片焊锡厚度不均匀,造成倾斜,IO间焊锡短路。芯片焊锡厚度不足,在温度循环测试中,容易开裂。

对于较大的单一PIN脚,焊锡越多,空洞越大,容易造成不平衡。可以适当把开窗分成多个小的开窗,以减少实际的焊锡量,并减少空洞。

审核编辑:汤梓红

-

芯片

+关注

关注

454文章

50689浏览量

423018 -

焊盘

+关注

关注

6文章

551浏览量

38133 -

钢网

+关注

关注

0文章

23浏览量

9273

发布评论请先 登录

相关推荐

芯片的焊盘和钢网尺寸设计规范

芯片的焊盘和钢网尺寸设计规范

评论