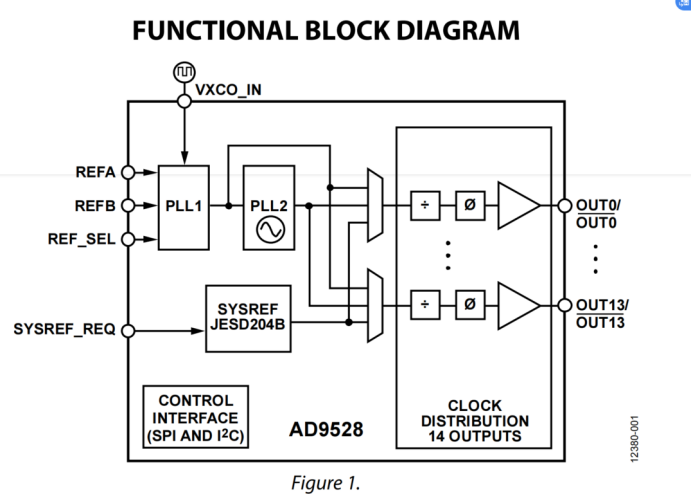

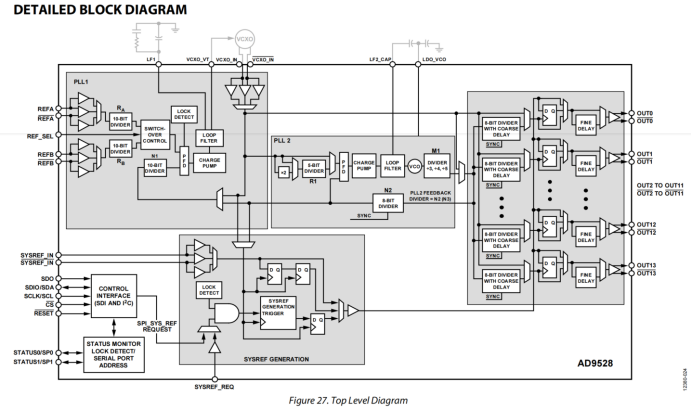

AD9528是ADI(亚德诺半导体技术有限公司,Analog Devices, Inc. 简称ADI )出品的一款双级PLL,集成JESD204B SYSREF发生器,可用于多器件同步。第一级锁相环(PLL) (PLL1)通过减少系统时钟的抖动,从而实现输入基准电压调理。第二级PLL (PLL2)提供高频时钟,可实现来自时钟输出驱动器的较低积分抖动以及较低宽带噪声。外部VCXO提供PLL2所需的低噪声基准电压,以满足苛刻的相位噪声和抖动要求,实现可以接受的性能。片内VCO的调谐频率范围为3.450 GHz至4.025 GHz。集成的SYSREF发生器输出单次、N次或连续信号,并与PLL1和PLL2输出同步,以便对齐多个器件的时间。

AD9528产生最高频率为1.25 GHz的六路输出(输出0至输出3、输出12和输出13),以及最大频率高达1 GHz的八路输出。每一路输出均可配置为直接从PLL1、PLL2或内部SYSREF发生器输出。14路输出通道的每一路都包含一个带数字相位粗调功能的分频器,以及一个模拟微调相位延迟模块,允许全部14路输出具有时序对齐的高度灵活性。AD9528还可用作灵活的双通道输入缓冲器,以便实现14路器件时钟和/或SYSREF信号的分配。

AD9528需要配置的部分如下:

PLL1配置;

PLL2配置;

SYSREF配置;

输出通道配置;

下面对各个配置进行详细说明:

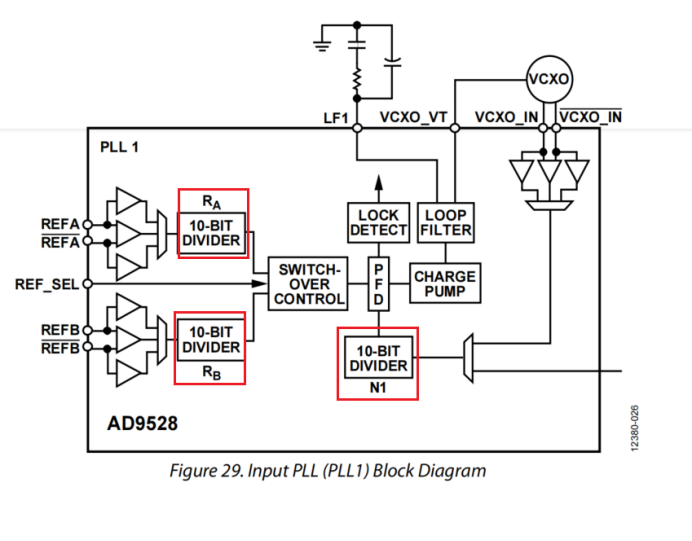

1,PLL1配置。

PLL1的内部结构如下:

PLL1 支持外部压控晶体振荡器(VCXO),外部双路可选的参考时钟。VCXO和参考时钟支持LVDS和COMS两种可选的输入电平。两路参考输入和VCXO路径上分别均有数字时钟分频器(Ra,Rb,N1) 。

参考时钟输入选择支持引脚控制和软件控制两种模式,一般情况下,默认使用软件控制。通过寄存器0x010A的bit2来控制,bit2 = 0, 采用软件控制模式,bit2 = 1,采用引脚控制模式。

参考时钟和VCXO的输入模式通过寄存器 0x0108 和 0x0109 控制,均支持 差分LVDS输入,单端CMOS正极(P端)输入,单端CMOS负极(N端)输入。均有比特位来控制,详情参考AD9528的datasheet。

两路参考输入和VCXO路径上的数字时钟分频器分频数均为10比特,1--1023之间的任意整数分频。

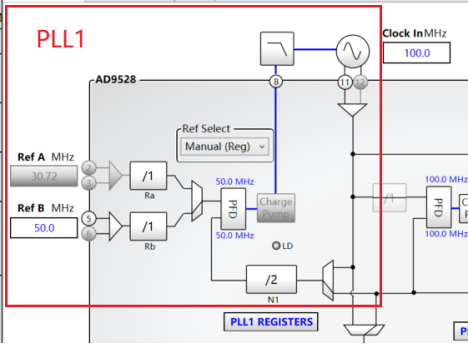

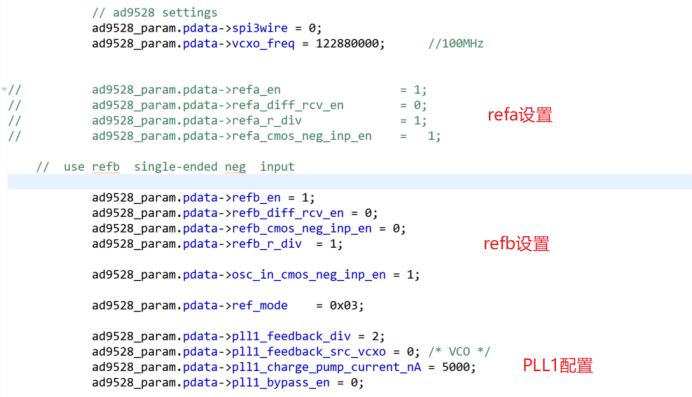

在本教程设计中,PLL1配置如下:

参考输入采用 B 端CMOS电平正极(P端)输入;

参考输入频率为50.00MHz;

VCXO的输入频率为100.00MHz;

参考输入B的时钟分频数为1;

VCXO的时钟分频数为2;

送到鉴相器(PFD)输入端的两个时钟频率均为50.00MHz,保证PLL锁定后VCXO的输出时钟频率为100.00MHz

2,PLL2配置。

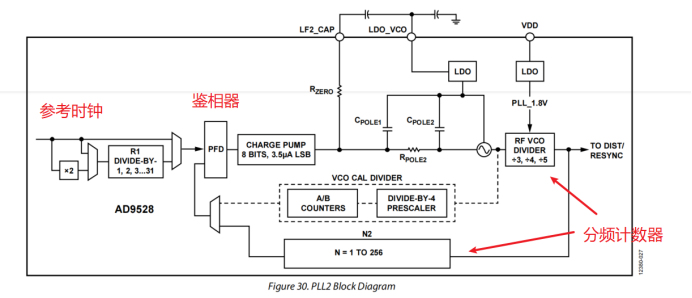

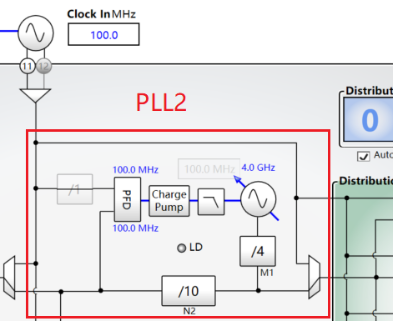

PLL2的内部结构如下:

PLL2的输入参考时钟为PLL1的VCXO的输出时钟,PLL2内部有内置的VCO(压控振荡器)。VCO到鉴相器路径上有两个分频计数器(M1,N2)。M1可配置为 3,4,5 。N2为8比特计数器,支持1-256的任意整数分频。PLL2的内部VCO的输出频率范围为:3.45GHz -- 4.025 GHz 。

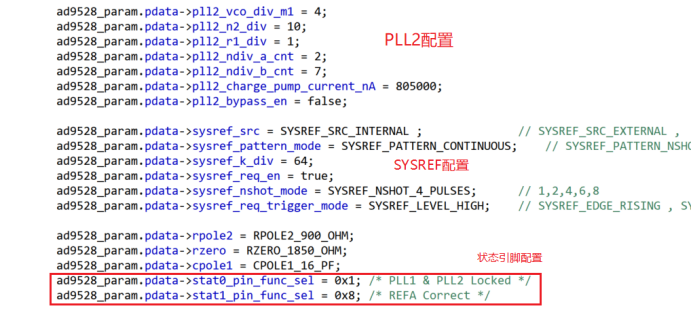

在本教程设计中,PLL2配置如下:

分频计数器M1:4 ;

分频计数器 N2:10 ;

保证VCO稳定时的输出频率为 4.00GHz,在VCO的支持输出频率之内。

3,SYSREF 配置

SYSREF支持三种配置模式,通过寄存器0X0403的bit[7:6]来控制,分别为,bit[7:6]:

00 = 外部输入模式。

01 = 外部输入重采样模式。

1x = 内部生成模式。

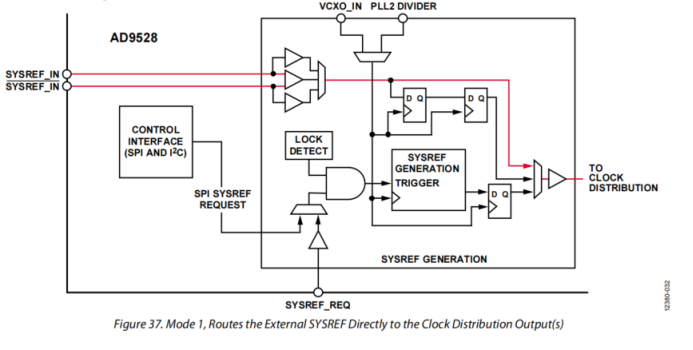

(1)外部输入模式。

该模式下,使用外部的 SYSREF_IN 作为 SYSREF 作为信号源,SYSREF_ IN 输入可配置为差分输入(LVDS电平)和单端输入(CMOS电平)。此模式下,SYSREF_REQ 引脚和 0X0403 的bit0 (SPI SYSREF请求)为使用。

此模式下的SYSREF信号路径如下图所示:

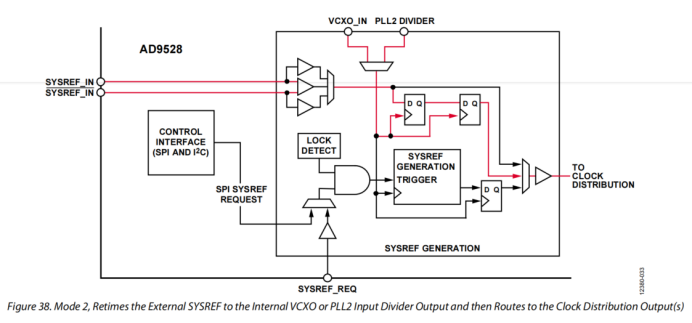

(2)外部输入重采样模式。

该模式下,使用外部的 SYSREF_IN 作为 SYSREF 作为信号源,并通过PLL1的输出时钟或PLL2的输出时钟对SYSREF_IN信号采样,SYSREF_ IN 输入可配置为差分输入(LVDS电平)和单端输入(CMOS电平)。此模式下,SYSREF_REQ 引脚和 0X0403 的bit0 (SPI SYSREF请求)为使用。

此模式下的SYSREF信号路径如下图所示:

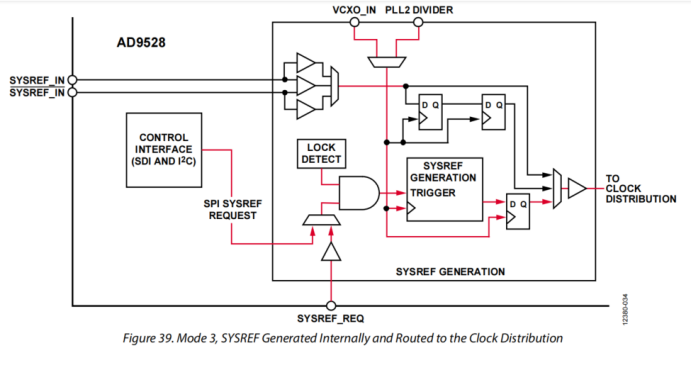

(3)内部生成模式。

SYSREF模式发生器( SYSREF pattern generator)生成用户定义的SYSREF信号。模式发生器的输入时钟由源自VCXO_IN引脚的信号提供,或由PLL2反馈节点的信号提供。模式发生器包含一个固定的2分频比,一个可编程的16位K分频器(由寄存器0x0401和寄存器0x0400设置),以对SYSREF的脉冲宽度进行配置。K的值介于0到65535之间,总分频系数为2×K,是在K分频器寄存器中编程值的两倍。例如,如果码型发生器的输入时钟为122.88 MHz,则最大SYSREF周期为131,070 / 122,880,000秒(1066μs)。模式发生器充当计时器,无论何时发出异步SYSREF请求,该计时器仅发出与所有其他输出同步的脉冲。

SYSREF模式发生器支持以下类型的SYSREF 信号:N-SHOT 模式,连续(Continuous)模式,PRBS 模式,以及停止(STOP)模式。常用配置模式为N-SHOT 模式和连续(Continuous)模式两种。

N-SHOT 模式下,在启动SYSREF请求之后,SYSREF输出N个脉冲,然后SYSREF输出变为逻辑低电平,直到下一个SYSREF请求为止。N 可以配置为 1,2,4,6,8 。连续模式下,SYSREF请求启动后,SYSREF输出连续输出101010…脉冲序列,其行为类似于频率为fIN /(2×K)的时钟。

SYSREF请求支持引脚请求(SYSREF_REQ)和软件请求(SPI SYSREF请求 )。请求模式通过寄存器0X0402 的bit7来控制。

在软件控制模式下,SYSREF模式发生器始终对SYSREF模式发生器触发控制位(寄存器0x402,位[6:5])电平触发。对于电平触发模式,当位6 = 0时,bit5用作触发。如果启用了N-shot模式,则将Bit 5 = 1从0设置为开始SYSREF模式序列。序列完成并输出N个脉冲后,SYSREF模式发生器自动清除bit5,并等待下一个SYSREF请求。在连续模式下,如果bit5 = 1,则模式序列继续。清除bit5以停止序列并等待下一个SYSREF请求。

引脚请求(SYSREF_REQ)又分为电平触发(Level Trigger)和边缘触发(Edge Trigger)两种模式。

在电平触发模式下(寄存器0x0402的位6 = 0),SYSREF模式发生器由SYSREF_REQ引脚控制。如果使能了N-shot模式,则将SYSREF_REQ引脚从0强制为1,以启动SYSREF模式序列。序列完成并输出N个脉冲后,将SYSREF_REQ引脚强制为0。然后,模式生成器等待下一个SYSREF请求。在连续模式下,将SYSREF_REQ引脚从0强制为1,以启动SYSREF模式序列。强制将SYSREF_REQ引脚设置为0以停止序列。然后,模式生成器等待下一个SYSREF请求。

在边沿触发模式下,SYSREF模式发生器由SYSREF_REQ引脚上的上升沿或下降沿控制。上升或下降有效沿由寄存器0x0402的位[6:5]决定。当位6 = 1时,位5控制有效触发沿。如果使能了N-shot模式,则SYSREF_REQ引脚的有效沿将启动SYSREF模式序列。序列完成并输出N个脉冲后,码型发生器将等待下一个SYSREF请求。如果在完成N个脉冲之前将SYSREF_REQ设置为0,则当前模式序列不受影响。因此,如果新的SYSREF_REQ活动边沿在模式序列完成之前到达,则新请求将丢失。在连续模式下,SYSREF_REQ活动边沿启动SYSREF模式序列。序列之后,模式生成器等待下一个SYSREF请求。

此模式下的SYSREF信号路径如下图所示:

在本教程设计中,SYSREF配置为如下模式:

内部生成模式。

连续(Continuous)模式。

高电平触发模式。

分频数K = 64 。

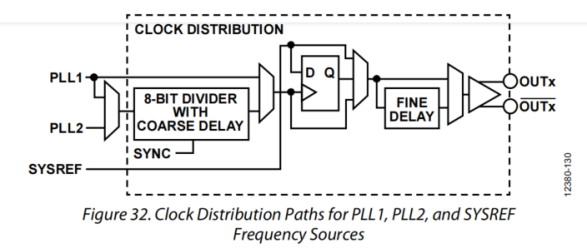

4,输出通道配置。

AD9528拥有14路输出通道,各个通道的结构如下图所示:

每个通道的输出均有 PLL1 ,PLL2 , SYSREF 三个可选源。输出通道可选择如下的输出源:

PLL2 分频输出。

PLL1(VCXO)输出。

SYSREF(PLL1输出重采样)。

SYSREF(PLL2输出重采样)。

反向PLL1(VCXO)输出。

SYSREF(反向PLL1输出重采样)。

各个通道的输出电平支持 LVDS ,LVDS(boost mode),HSTL 三种模式电平。各个通道也均有模拟细延迟和数字粗延迟模块, 用于精确控制各个通道信号的输出延迟。同时各个通道存在8比特的分频计数器。

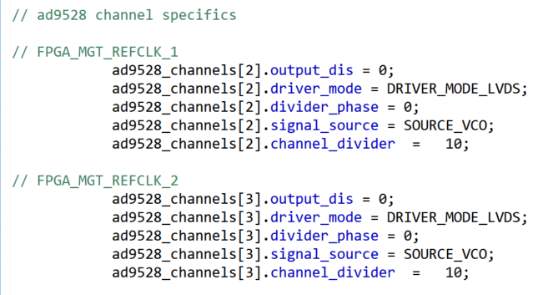

在教程中,各个输出通道配置如下:

| 输出通道 | 用途 | 频率(MHZ) | 源 | 通道分频数 | 备注 |

| Out0 | / | / | / | / | 未使用 |

| Out1 | / | / | / | / | 未使用 |

| Out2 | FPGA_MGT_REFCLK1 | 100.00 | PLL2/divider | 10 | |

| Out3 | FPGA_MGT_REFCLK2 | 100.00 | PLL2/divider | 10 | |

| Out4 | / | / | / | / | 未使用 |

| Out5 | / | / | / | / | 未使用 |

| Out6 | / | / | / | / | 未使用 |

| Out7 | ADC_SYSREF_1 | 0.78125 | SYSREF(PLL2) | / | |

| Out8 | ADC_DCLK_1 | 200.00 | PLL2/divider | 5 | |

| Out9 | ADC_DCLK_2 | 200.00 | PLL2/divider | 5 | |

| Out10 | ADC_SYSREF_2 | 0.78125 | SYSREF(PLL2) | / | |

| Out11 | / | / | / | / | 未使用 |

| Out12 | FPGA_SYSREF | 0.78125 | SYSREF(PLL2) | / | |

| Out13 | FPGA_CORE_CLK | 200.00 | PLL2/divider | 5 |

5,配置程序说明

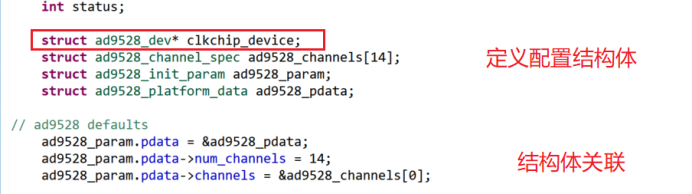

AD9528的配置采用ADI提供的一套基于裸机环境,可跨平台,高度可移植的配置代码。下面大致说明一下该代码的使用流程。

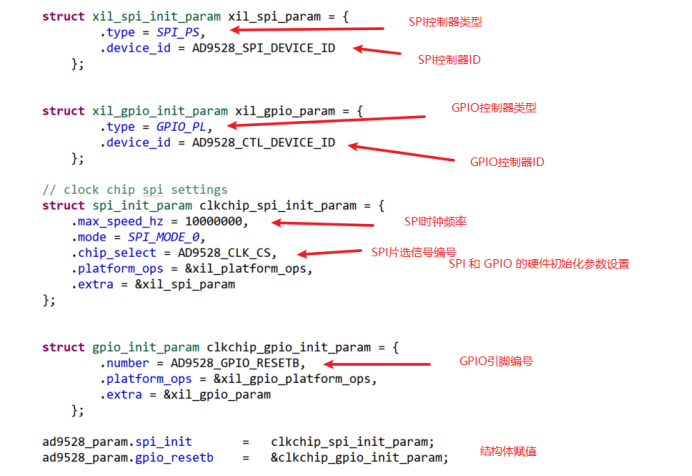

(1)定义并关联配置结构体。

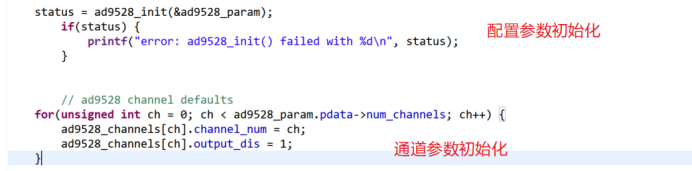

(2)配置参数以及通道参数的初始化

(3)各个需要配置的输出通道的参数配置。包括输出使能,输出模式,信号源,通道分频数的配置。

(4)PLL1,PLL2,SYSREF配置。

(5)SPI以及用于复位的GPIO引脚的参数配置。

包括SPI控制器的类型,SPI控制器的ID,GPIO控制器的类型,GPIO控制器的ID,SPI的时时钟频率,片选编号,AD9528用于复位的引脚编号等等。

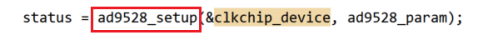

(6)运行AD9528配置函数。

运行函数ad9528_setup() , 完成对AD9528的配置。

审核编辑 :李倩

-

芯片

+关注

关注

455文章

50784浏览量

423450 -

发生器

+关注

关注

4文章

1368浏览量

61693 -

pll

+关注

关注

6文章

776浏览量

135149

原文标题:AD9528芯片介绍及配置详解

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

边缘芯片详解

nginx负载均衡配置介绍

ABB变频器的硬件配置详解

如何配置和校准电阻屏

苹果M3芯片参数配置

雅特力AT32F423时钟配置

AD9528芯片介绍及配置详解

AD9528芯片介绍及配置详解

评论