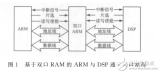

单口 RAM(Single RAM)、双口 RAM(Dual RAM)、简单双口 RAM(Simple-Dual RAM)、真双口 RAM(True-Dual RAM)有什么不同?

【华为2021秋招】FPGA逻辑笔试解析【独家】【数字IC】【FPGA逻辑】【2021届秋招】中的第 2 题,答案正确,解析有误。

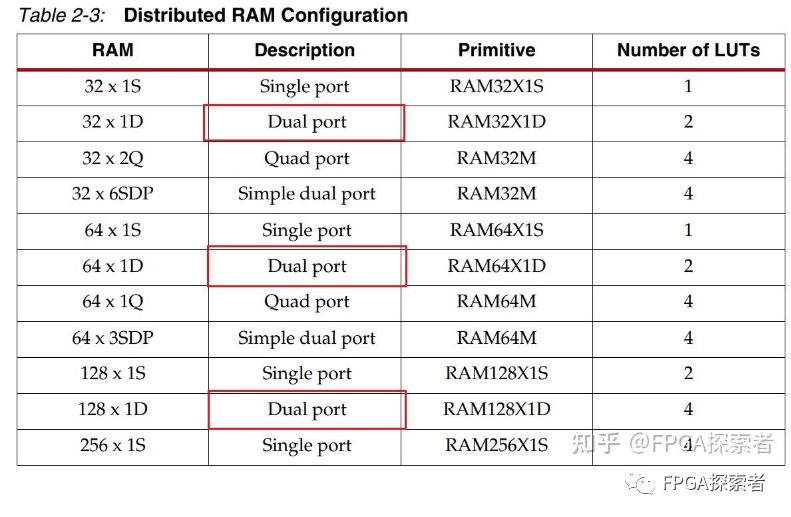

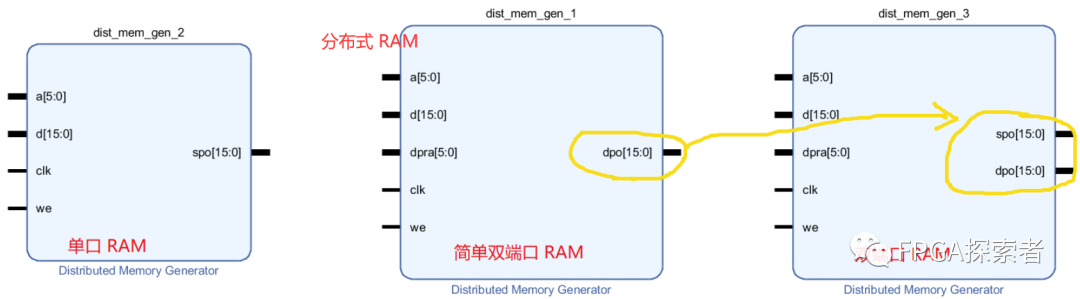

对于 分布式 RAM,支持简单双口 RAM 和双口 RAM,不能配置成真双口 RAM。

问题在于:Xilinx 给出的 DRAM(分布式 RAM)支持双口,我把双口认为包含真双口了,不对。

先总结一下,如有不对,欢迎私信联系批评指正。

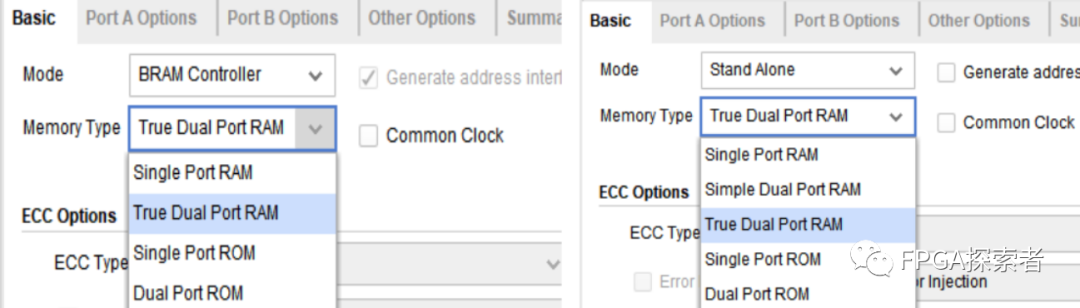

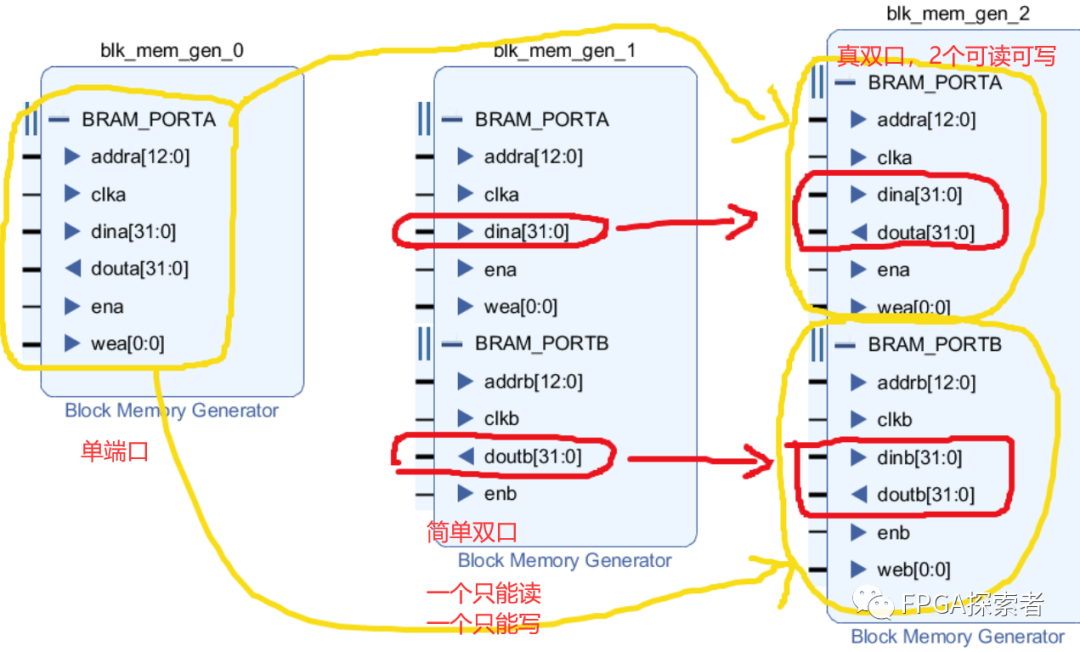

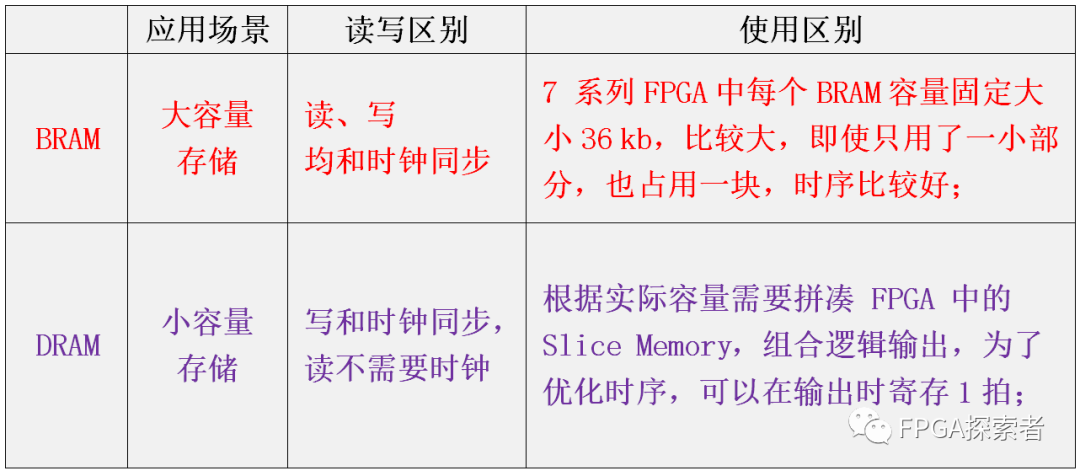

对于 BRAM(Block RAM,块 RAM)

在 BRAM Controller 控制器下,支持单口 RAM、真双口 RAM、单口 ROM 和双口 ROM;

在不使用 AXI 的控制器情况下,支持单口 RAM、简单双口 RAM、真双口 RAM,单口 ROM 和双口 ROM。

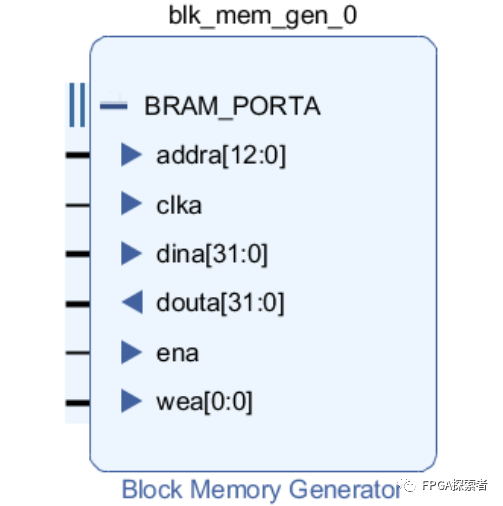

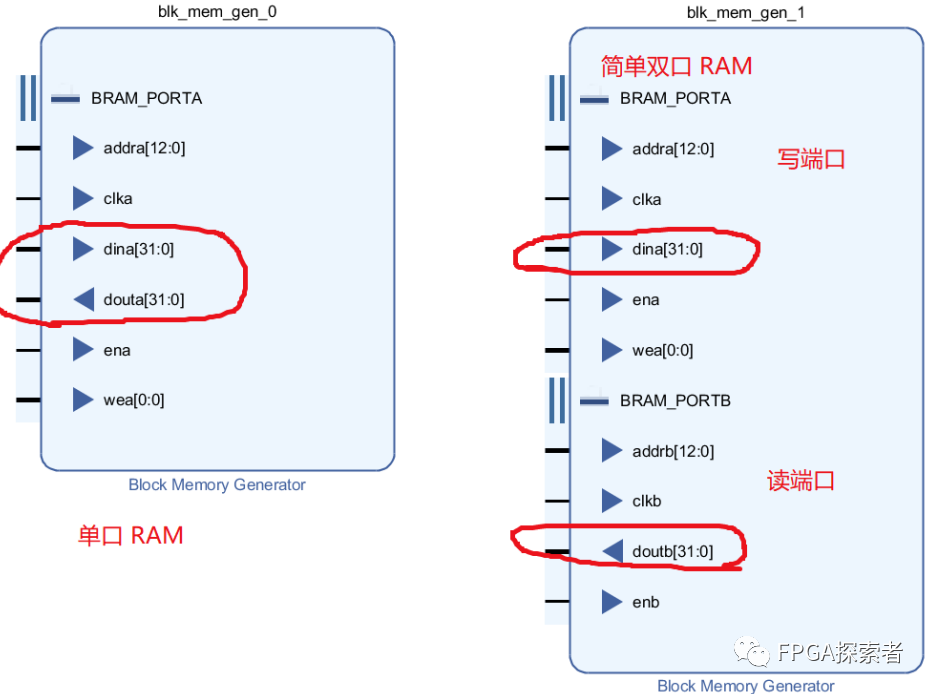

单口RAM:

1 个时钟,1 个读写地址(要么读用,要么写用),可以读也可以写,但是不能同时读写;

简单双口 RAM:

2 个端口,有相互独立的时钟,一个口专门负责写,一个口专门负责读;

真双口 RAM:

和简单双口的区别:

简单双口是一个口专门读,一个口专门写;

真双口是 2 个口都可以读写;

真双口可以看成是 2 个单口拼起来的,且 2 个单口共享存储器。

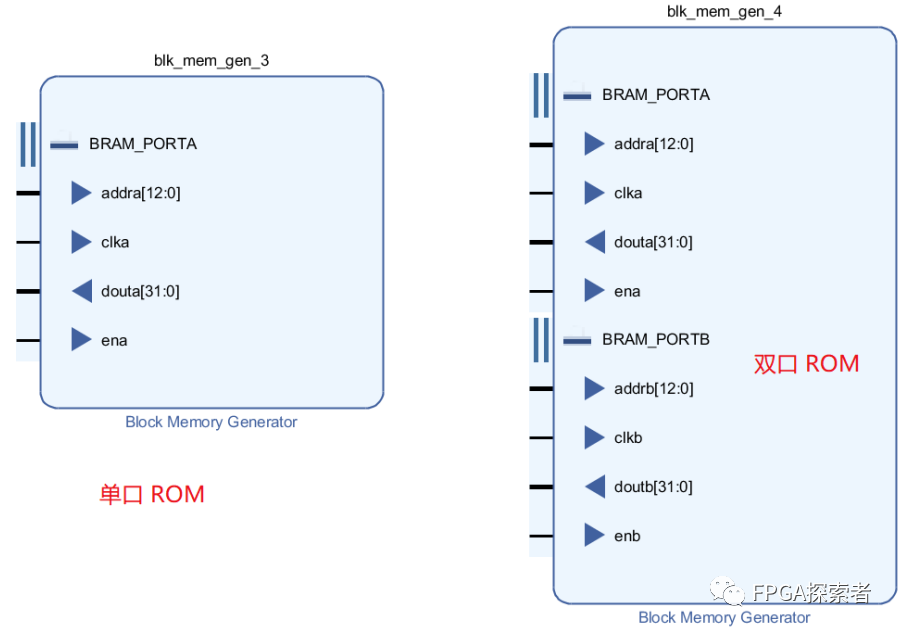

单口 ROM 和 双口 ROM

双口 ROM 可以看成是 2 个单口拼起来的,且 2 个单口共享存储区。

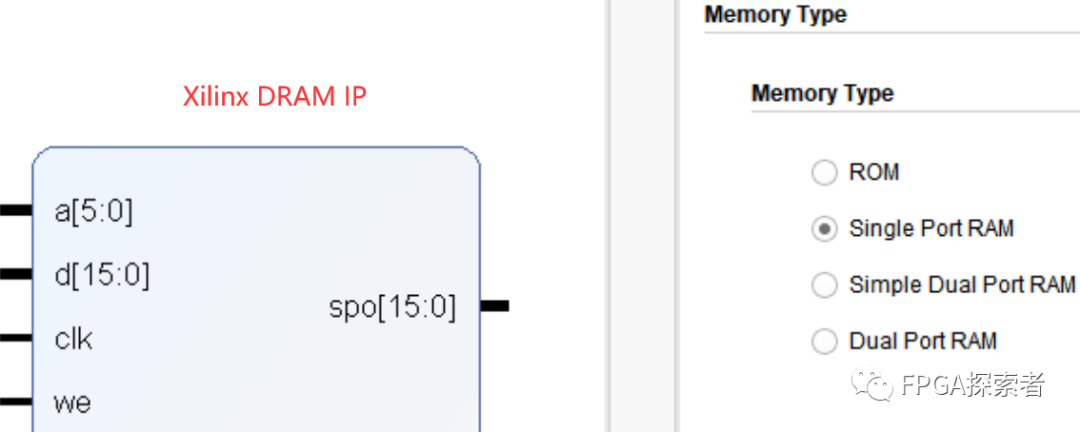

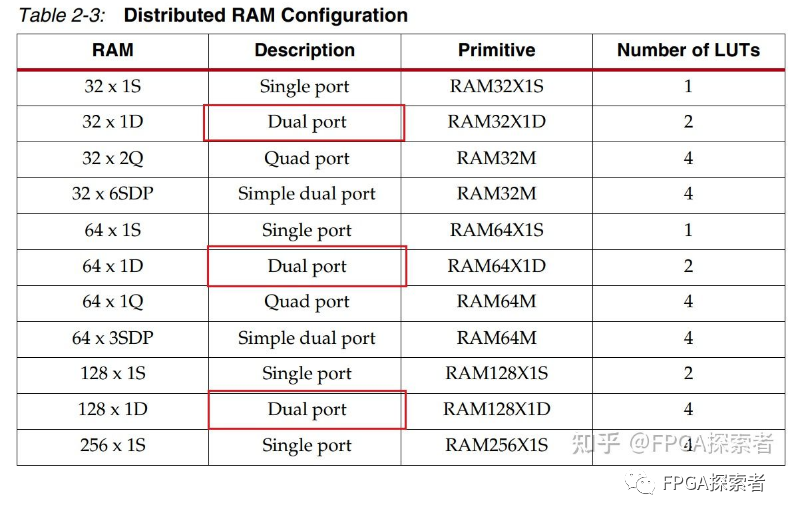

对于 DRAM(Distribute RAM,分布式 RAM)

ROM

给地址,出对应地址的数据,没有时钟

RAM:支持单口、简单双口、双口。

(注意!这里的双口和真双口不同,DRAM 不支持真双口 RAM)

单口 RAM:读写共用地址 a[5:0],写数据时 we 拉高,不能同时读写;

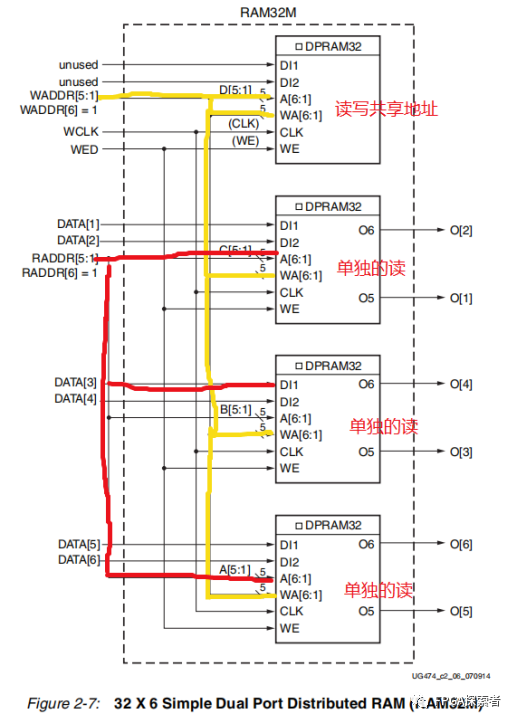

简单双口 RAM:1 个读地址,1 个写地址,1 个输入,1 个输出;

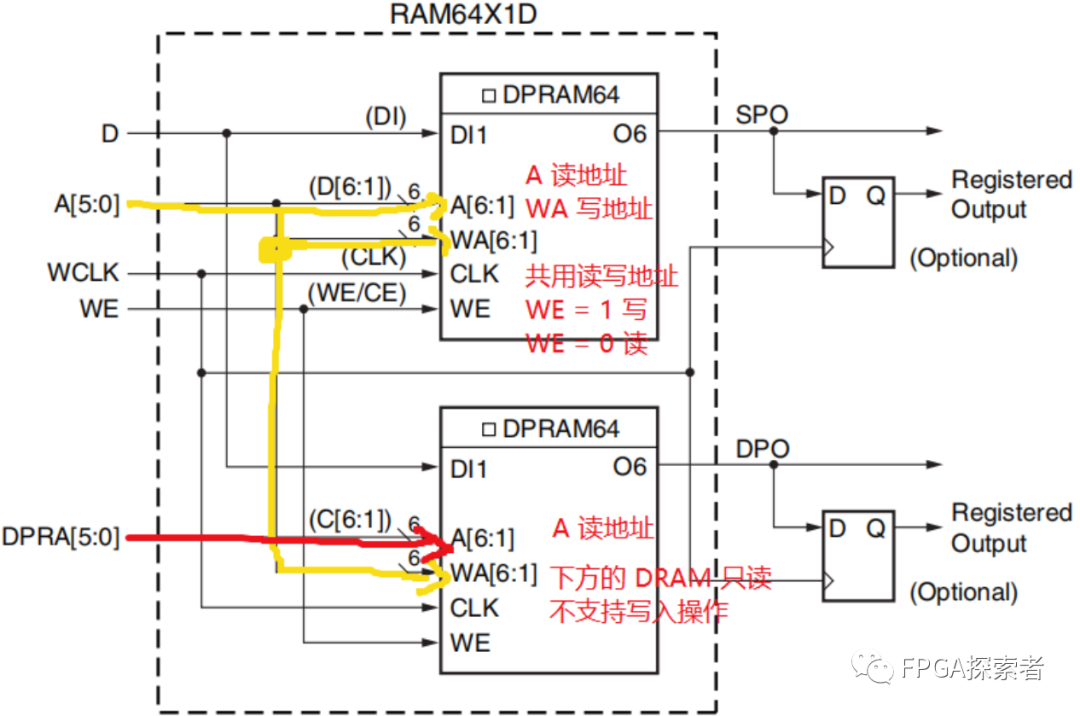

双口 RAM:1 个通道共享读写(等同于单口),1 个通道只读,2 个输出,

spo 数据对应 a 地址,dpo 数据对应 dpra 地址;

a[5:0],读写共用的地址,当 we = 1 时表示写地址,将 d[15:0] 写入 RAM,当 we = 0 时,将 a[5:0] 地址的数据从 spo[15:0] 上输出;

dpra[5:0] 只用于读的地址,读出 dpra[5:0] 上的数据,从 dpo[15:0] 输出。

当进行读取时,简单双口一次读取 1 个数据,双口可以同时读取出 2 个数据。

四口 RAM:1 个通道共享读写,3 个通道只读;

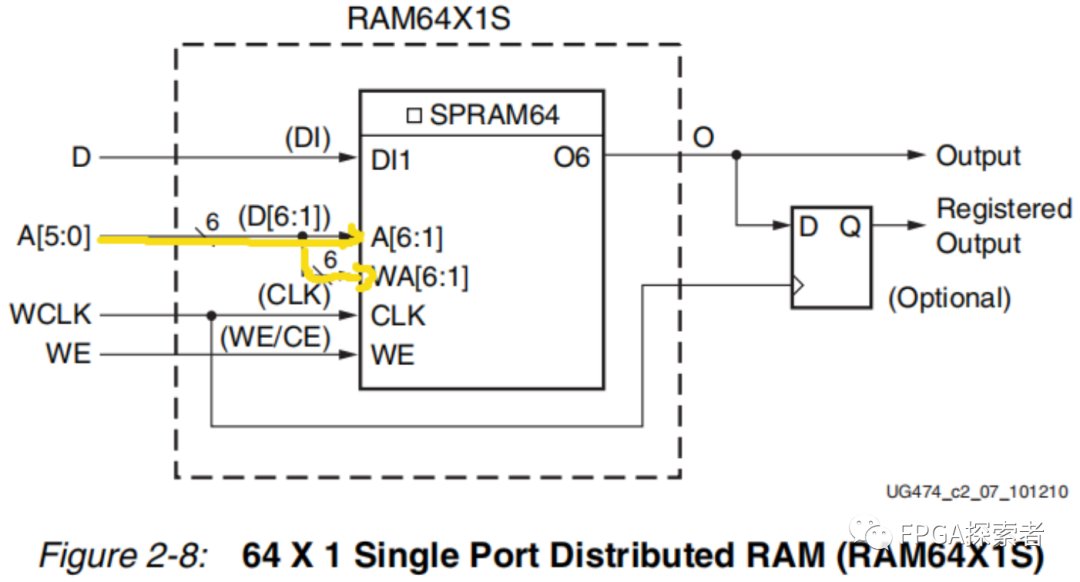

单口:

WE = 1 写入,使用的实际上是 WA[6:1] 地址,写入发生在时钟的上升沿,时序逻辑;

WE = 0 读出,使用的是 A[6:1] 地址,地址线上有地址,数据立刻读出,组合逻辑输出;

单口情况下,A 和 WA 连在一起,共享读写地址线;

双端口:

•一个用于同步写入和异步读取的端口

第一个函数发生器与共享读写端口地址相连

•一个用于异步读取的端口

第二函数发生器具有连接到第二个读端口地址的A输入,并且 WA 输入与第一读/写端口地址共享

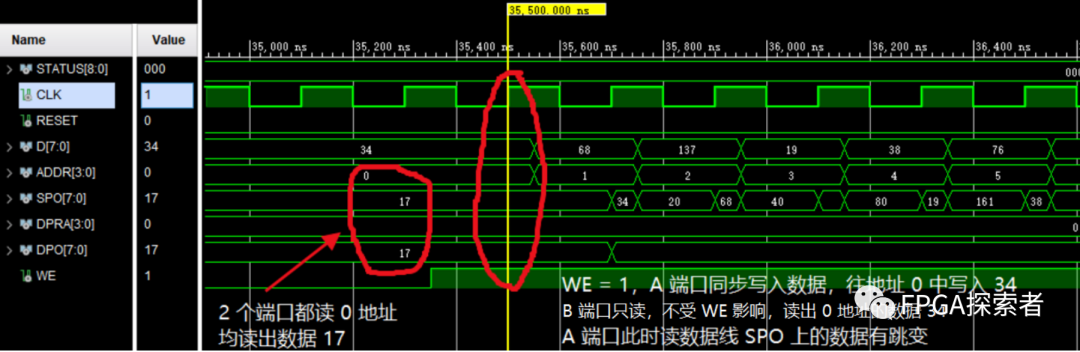

如下图所示为双口 DRAM 的读写仿真:

(1)在 WE = 0 时,两个口均为读出口,A 口的地址线 ADDR[3:0] 的地址为 0,在 SPO[7:0] 上读出数据 17,B 口的地址线 DPRA[3:0] 为 0,在 DPO[7:0] 上读出数据 17;

(2)在 WE = 1 时,A 口为写入口,B 口是只读口,此时仍为读出口,A 口向地址 0 写入数据 D[7:0] = 34,B 口仍为读,读出 0 地址的数据 34;

简单双端口

•一个用于同步写入的端口(没有来自写入端口的数据输出/读取端口)

•一个用于异步读取的端口

参考:

[1] Xilinx ug474_7Series_CLB

[2] Xilinx pg063-dist-mem-gen

[3] Xilinx pg058-blk-mem-gen

原文标题:Xilinx的分布式RAM和块RAM——单口、双口、简单双口、真双口的区别

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1630文章

21796浏览量

605593 -

RAM

+关注

关注

8文章

1369浏览量

114944 -

Xilinx

+关注

关注

71文章

2171浏览量

122029

原文标题:Xilinx的分布式RAM和块RAM——单口、双口、简单双口、真双口的区别

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

单口、双口、简单双口、真双口RAM的区别

单口、双口、简单双口、真双口RAM的区别

评论