学习内容

学习关于ZYNQ IP核中的GP接口和HP接口的异同,介绍关于AXI_GP接口和AXI_HP接口的相关内容。

AXI_HP和AXI_GP异同

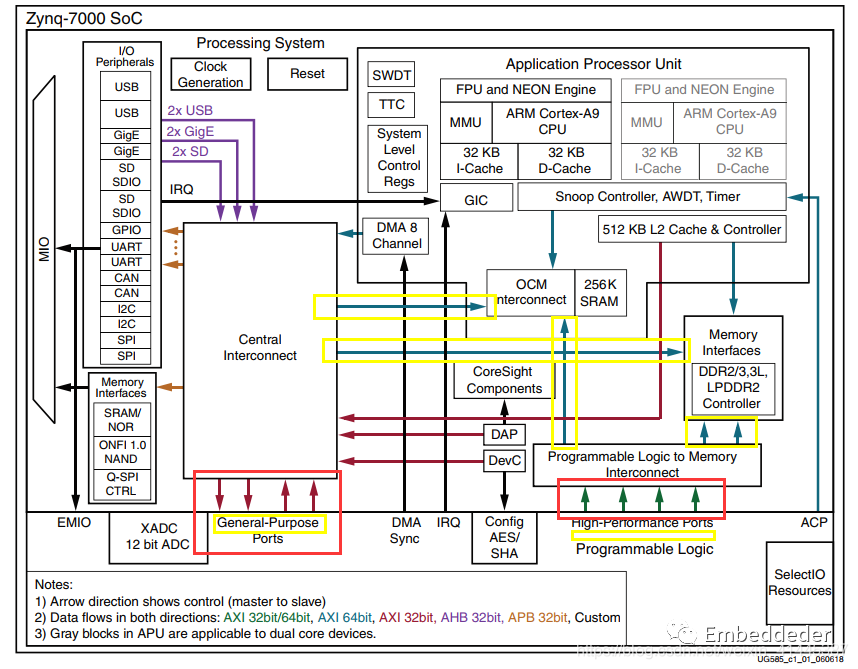

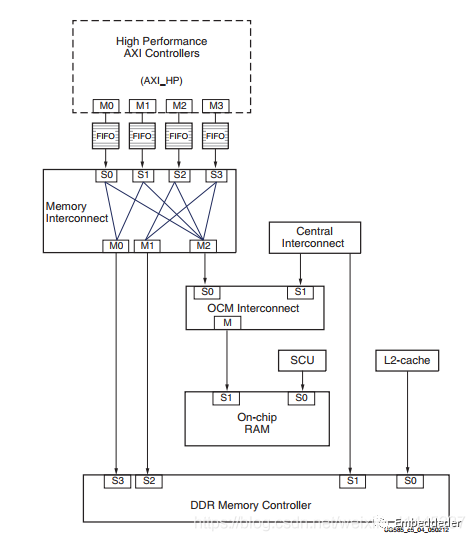

首先给出ZYNQ SoC的系统框图,如下图所示。在图中,箭头方向代表主机到从机的方向。

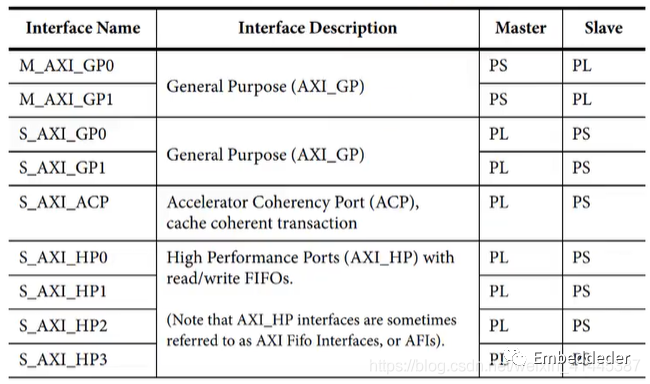

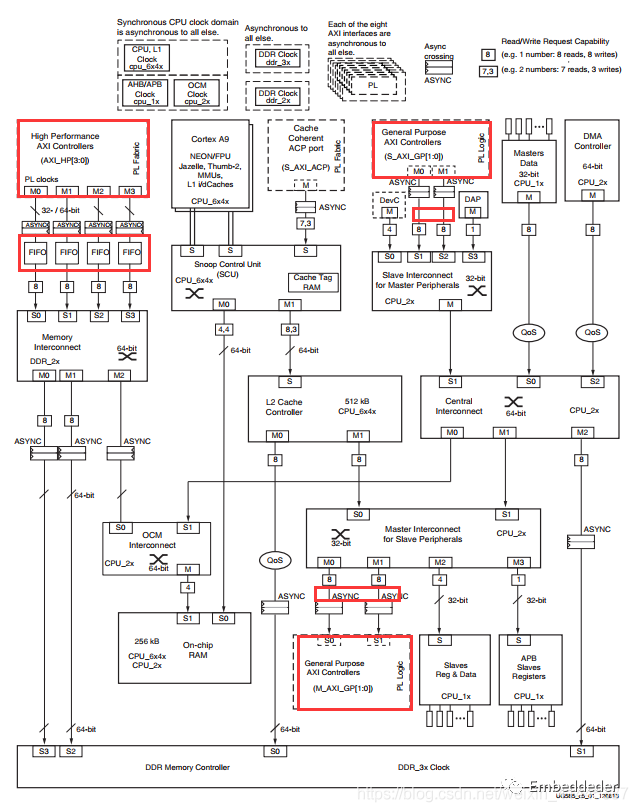

对于GP接口(general purpose)通用目的接口,有四个接口(两个从端口,两个主端口);HP接口(high-performance purpose)高性能接口,有四个接口(四个都是从端口)。GP接口直接连接到的是中央互联区(central interconnect),然后由中央互联区再连接到OCM interconnect和存储器接口上;而HP接口直接连接到的是OCM interconnect和存储器接口。所以对于GP接口,通常使用他进行控制配置;而对于HP接口,通常使用它进行数据传输交互。下图是HP和GP对应主从机具体信息:

AXI_HP接口

4个AXI HP接口为PL的主机提供了DDR和OCM存储器的高带宽的数据路径。 每个HP接口包括两个的FIFO缓存,用于读写传输。PL到内存互连高速AXI HP端口路由连接到两个DDR内存端口和一个OCM存储器端口。AXI HP接口也被称为AFI (AXI FIFO接口),以强调它们的缓冲功能。 PL电平移位器必须通过LVL SHFTR EN启用后,才能进行PL逻辑通信。

特点

这些接口被设计为在PL主存储器和PS存储器(包括DDR和片上RAM)之间提供一个高吞吐量的数据路径。主要功能包括:

可以实现32或64位数据位宽的主接口(每个端口独立编程)。

在32位接口模式下,可以进行动态配置位为64位,以实现对齐传输,通过AxCACHE [1]可以进行控制。

在32位接口模式下,为未对齐的32位传输自动扩展到64位。

可编程的写命令释放阈值。

PL和PS之间的所有AXI接口的异步时钟域交叉。

使用1kb (128 × 64位)数据缓存FIFO来平滑“长延迟”传输,用于读写。

从PL端口提供QoS信令。

命令和数据FIFO填充级计数可用于PL端。

支持标准AXI 3.0接口。

可编程命令下发到互连,分别用于读和写命令。

14到70个指令范围的高性能从接口读接受能力。(取决于突发长度)

8到32个指令范围的高性能从接口写接受能力。(取决于突发长度)

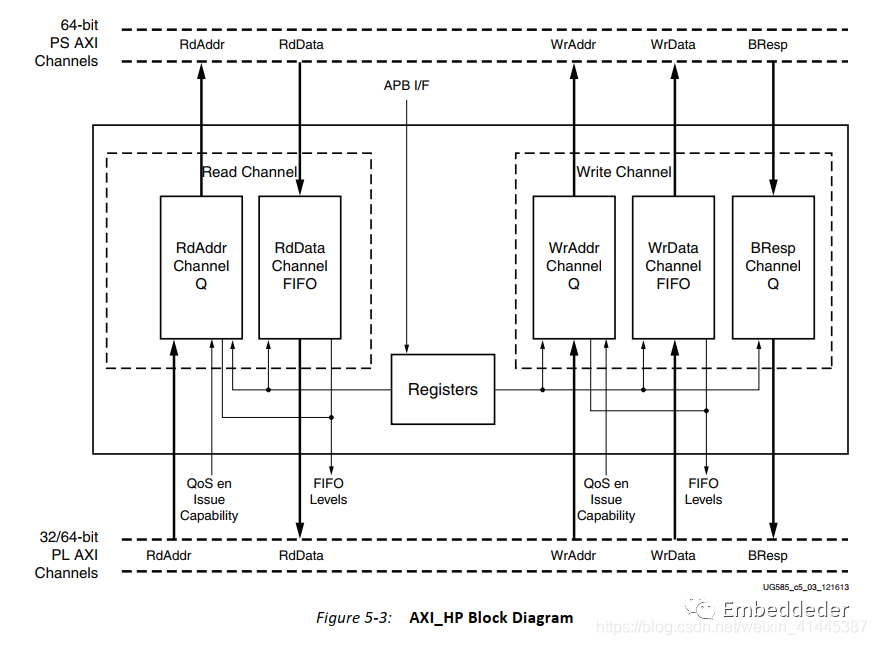

AXI_HP接口的框图

为了提高读写的性能,在读写数据通道添加了FIFO用于读写数据的传输。

有两组AXI端口,一组直接连接到PL,另一组连接到AXI互连矩阵,允许访问DDR和OCM内存:

AXI_GP接口

AXI_GP接口直接连接到主互连和从互连的端口,没有任何额外的FIFO缓冲,不像AXI_HP接口使用FIFO缓冲以提高性能和吞吐量。因此,性能受到主互连端口和从互连端口的限制。这些接口仅用于通用用途,并不是为了实现高性能。

特点

AXI GP的特性包括:

支持标准AXI协议

数据总线宽度只有32位

主端口ID位宽为12位

主端口发送能力:8位读,8位写

从端口ID位宽为6位

从端口接受能力:8位读,8位写

Reference

Xilinx UG585

正点原子ZYNQ开发视频教程

原文标题:Reference

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

-

存储器

+关注

关注

38文章

7528浏览量

164245 -

接口

+关注

关注

33文章

8691浏览量

151776 -

HP

+关注

关注

1文章

86浏览量

40158

原文标题:Reference

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Zynq MPSoC系列器件的AXI总线介绍

如何实现从microblaze端访问ARM DDR?

玩转Zynq连载34——[ex54] 基于Zynq的AXI GP总线的从机接口设计

如何避免AXI_hp总线锁死?

何谓 AXI?关于AXI3/AXI4的相关基础知识

你必须了解的AXI总线详解

AXI4-Stream Video 协议和AXI_VDMA的IP核介绍

关于AXI BRAM控制器的相关内容

AXI VIP当作master时如何使用?

AXI_GP接口和AXI_HP接口的相关内容

AXI_GP接口和AXI_HP接口的相关内容

评论