锁相环的一些概念

1、捕获、锁定与跟踪的概念

捕获,是指从输入信号加到锁相环输入端开始开始,一直到环路达到锁定的全过程。

锁相环的锁定是指锁相环的输出频率等于输入频率,而输出信号的相位跟随输入信号的变化而变化。

跟踪是指锁相环锁定后的状态,一旦锁相环进入锁定状态,若输入信号产生了相位的变化,环路就调整压控振荡器的控制电压使得其输出信号的相位跟随输入信号的相位变化,即保持恒定的稳态相位差。这种状态称为跟踪或同步状态。

2、捕获时间和稳态相差

捕获时间是指捕获过程所需的时间。捕获时间的大小不仅与环路参数有关,而且与起始状态有关。

当环路进入同步状态之后,环内被控振荡器的振荡器频率已经等于输入信号的频率,两者之间只差一个固定的相位。这个相位差称为稳态相差。反过来说,若稳态相差为一个常数或等于0,则说明环路处于锁定状态。

3、相位捕获和频率捕获

“相位捕获”指在捕获过程中,相位没有经过2π的周期跳跃就能进入的锁定状态,即捕获过程小于一个2π周期的捕获过程称为相位捕获,又称快捕获。“频率捕获”指捕获经历一个以上的频率周期的捕获过程。即意味着环路的输入信号频率与输出信号频率在开始捕获前相差至少一个周期。一般来说,一个锁相环从捕获到锁定都要经历从频率捕获到相位捕获两个过程。

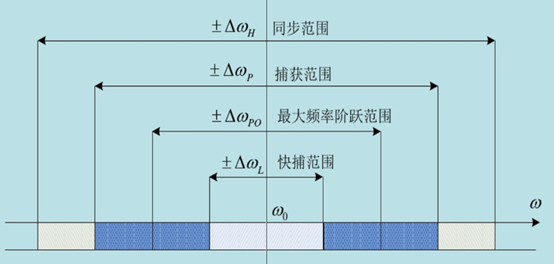

如下图的快捕范围就是快捕带,只有相位捕获,因此收敛较快,而除快捕范围的捕获带则首先要进行频率捕获,然后才是相位捕获。频率捕获相对来说是一个慢的过程,因此收敛较慢。

4、捕获带和同步带

捕获带是指保证环路必然进入锁定的最大固有频差值。换句话说,就是在保证环路不出现稳定的差拍状态所允许的最大固有频差值。

一旦环路进入锁定状态,系统就处于跟踪状态。随着输入信号的频率和相位的变化,环路应该始终能跟踪其变化,但一旦输入信号的频率与被控压控振荡器的自由振荡器频率相差太多,环路就会失去跟踪能力,这种状态称为“失锁”。

同步带是指系统保持同步的最大固有频差值

5、最大频率阶跃范围

描述PLL对于稳定工作状态的动态限制。环路初始处于锁定状态,当输入信号的频率发生阶跃变化的幅度在失锁带的范围之内,环路能够保持锁定。然而,当输入信号的频率发生阶跃变化的幅度超出失锁带的范围,环路不能保持锁定,输出信号无法跟踪输入参考信号。当然,通过缓慢的捕获过程,环路可再次入锁。

鉴相器

关于鉴频器介绍一下2种鉴频器:

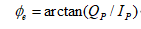

鉴频器1,二象限反正切函数,

优点:最准确的鉴相方法,实际相位差异位于-90°至+90°的范围之内时,该鉴相器的工作保持线性,并且其输出的鉴相结果与信号幅值无关。

缺点:需要进行反正切求值,因而它也是计算量最大的一种。

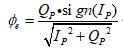

鉴频器2

优点:计算量小, 适合纯逻辑实现

缺点:鉴频近似准确,鉴相结果与

成正比,并且与信号幅值有关

环路滤波器 和 频率可变振荡器 与锁频环一样,不在重复叙述

Matlab 程序

在锁频环的程序基础上添加锁相环,设定前面500ms是锁频环工作,将频率快速的拉到接近的范围,然后切换到锁相环,期间在1s的时候频率突变10Hz,在2s的时候突变30Hz,在3s的时候突变100Hz,来理解快捕范围,频率阶跃、捕获带等这些概念。为了显示更加清楚,这里就不加码元信息了

format long g;

clc;clear all;close all

SampleClk = 4.1e6;

PointNum = SampleClk*5;

IF = 1e6- 240 ;

Carr_cos(1:SampleClk) = cos(2*pi*(IF/SampleClk).*[1:SampleClk] + 0);

Carr_sin(1:SampleClk) = sin(2*pi*(IF/SampleClk).*[1:SampleClk] + 0);

IF = IF + 10;

Carr_cos(1+SampleClk:PointNum) = cos(2*pi*(IF/SampleClk).*[SampleClk+1:PointNum] + 0);

Carr_sin(1+SampleClk:PointNum) = sin(2*pi*(IF/SampleClk).*[SampleClk+1:PointNum] + 0);

IF = IF + 30;

Carr_cos(1+2*SampleClk:PointNum) = cos(2*pi*(IF/SampleClk).*[2*SampleClk+1:PointNum] + 0);

Carr_sin(1+2*SampleClk:PointNum) = sin(2*pi*(IF/SampleClk).*[2*SampleClk+1:PointNum] + 0);

IF = IF + 100;

Carr_cos(1+3*SampleClk:PointNum) = cos(2*pi*(IF/SampleClk).*[3*SampleClk+1:PointNum] + 0);

Carr_sin(1+3*SampleClk:PointNum) = sin(2*pi*(IF/SampleClk).*[3*SampleClk+1:PointNum] + 0);

signal0 = Carr_cos +j*Carr_sin;

data = awgn(signal0,-5,'measured');

n = SampleClk/1000;

num=1000;

a=rand(1,num);

a(a>0.5)=1;

a(a<=0.5)=-1;

% for m = 1 1000

% data(m*n+1:(m + 1)*n) = a(m)*data(m*n+1:(m + 1)*n);

% end

fc = 1e6;

n = SampleClk/1000;

nf = floor(length(data)/n);

FAccCarReg0 = 0;

PAccCarReg0 = 0;

frame = 0;

FLL_BL = 100;

PLL_BL = 20;

tc1 = 1/1000;

k1 = 1;

[d0,d1] = Fil2ndPara(k1,FLL_BL,tc1);

[c0,c1] = Fil2ndPara(k1,PLL_BL,tc1);

df(1:nf) = 0;

df1(1:nf) = 0;

PQaccu = 0;

PIaccu = 0;

fll = 0;

pll = 0;

carr_accu = 0;

counter = 1;

init_carr_freq = fc;

for frame = 1 : nf

% frame

carr_freq = init_carr_freq + fll + pll;

for clk = 0 : n-1

%clk

carr_accu = rem(carr_accu,1);

cosine = cos(2*pi*(carr_accu));

sine = sin(2*pi*(carr_accu));

baseband = (data(((frame-1)*n+clk+1))).*(cosine -j*sine);

PI_clk = real(baseband);

PQ_clk = imag(baseband);

PQaccu = PQaccu + PQ_clk;

PIaccu = PIaccu + PI_clk;

carr_accu = carr_accu + carr_freq/SampleClk;

end

PQ(frame) = PQaccu;

PI(frame) = PIaccu;

if PI(frame) == 0

PI(frame) = 0.0000001;

end

PQaccu = 0;

PIaccu = 0;

if frame <5

fll = 0;

pll = 0;

elseif(frame <500 )

df(frame) = FrqErr(PI,PQ,frame);

[fll,FAccCarReg0] = Fil2nd(d0,d1,FAccCarReg0,df(frame));

else

df1(frame) = PhaErr(PI,PQ,frame);

[pll,PAccCarReg0] = Fil2nd(c0,c1,PAccCarReg0,df1(frame));

end

fll_frame(frame) = fll + pll;

end

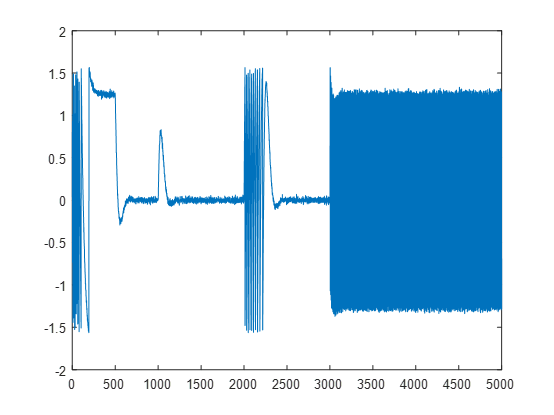

figure(1)

plot(fll_frame);

figure(4)

plot(PI);

hold on

plot(PQ);

hold on

figure(5)

plot(atan(PQ./PI))

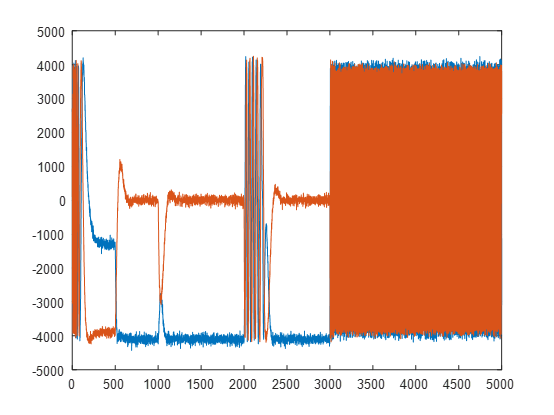

从频率跟踪图可以明显的看出

在500ms锁频环转锁相环的时候,误差频率很小,因此处于快捕带,只需要对相位进行捕获,收敛很快。在1s的时候,频率突变10Hz,环路仍然保持锁定,很快便调整到了正确的频率,因此10Hz属于最大阶跃范围内,2s的时候,频率突变30Hz,很明显的频率出现了震荡,这就是失锁了,但仍处于捕获带内,因此花了一点时间又重新锁定到正确的频率上,最后,频率突变100Hz,则直接跳出了捕获带之外,无法重新锁定了。

从I/Q幅度图以及鉴相值可以看出

在500ms和1s的时候,相位没有出现2*pi的翻转,而在2s的时候出现了多次的2pi的翻转,这也印证了最开始介绍锁相环的概念中的 频率捕获和相位捕获的内容。

IQ幅度图:

鉴相值图:

原文标题:FPGA学习-数字锁相环

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

锁相环

+关注

关注

35文章

584浏览量

87756 -

振荡器

+关注

关注

28文章

3832浏览量

139074 -

频率

+关注

关注

4文章

1499浏览量

59226

原文标题:FPGA学习-数字锁相环

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

锁相环PLL在无线电中的应用 锁相环PLL与模拟电路的结合

锁相环PLL的工作原理 锁相环PLL应用领域

简述锁相环的基本结构

锁相环和锁相放大器的区别

锁相环相位噪声的影响因素

锁相环的工作原理和应用场景

锁相环的基本原理和主要作用

锁相环锁定后一定不存在频差吗?

锁相环到底锁相还是锁频?

为什么说锁相环相当于一个窄带跟踪滤波器

锁相环不是能够完全跟踪输入信号的频率吗?为什么还会有固有频差?

锁相环同步带与捕获带有区别吗?

数字锁相环技术原理

锁相环的一些概念

锁相环的一些概念

评论