1. 概述

1)PCIe(Peripheral Component Interconnect Express)是继ISA和PCI总线之后的第三代I/O总线。一般翻译为周边设备高速连接标准。

2)PCIe协议是一种端对端的互连协议,提供了高速传输带宽的解决方案。目前PCIe已经发展到第四代PCIe4.0, 每一代的发展,最明显的特征就是速率翻倍。

3)是Intel公司1991年推出的。批准组织:PCI SIG (PCI兴趣小组)

4)一个x16插槽可以运行x1、x2、x4、x8、x16的卡

2. PCIe 布线规则

从金手指边缘到PCIe芯片管脚的走线长度应限制在4英寸(约100MM)以内。

PCIe的PERP/N,PETP/N,PECKP/N是三个差分对线,注意保护(差分对之间的距离、差分对和所有非PCIe信号的距离是20MIL,以减少有害串扰的影响和电磁干扰(EMI)的影响。芯片及PCIe信号线反面避免高频信号线,最好全GND)。

差分对中2条走线的长度差最多5MIL。2条走线的每一部分都要求长度匹配。差分线的线宽7MIL,差分对中2条走线的间距是7MIL。

当PCIe信号对走线换层时,应在靠近信号对过孔处放置地信号过孔,每对信号建议置1到3个地信号过孔。PCIE差分对采用25/14的过孔,并且两个过孔必须放置的相互对称。

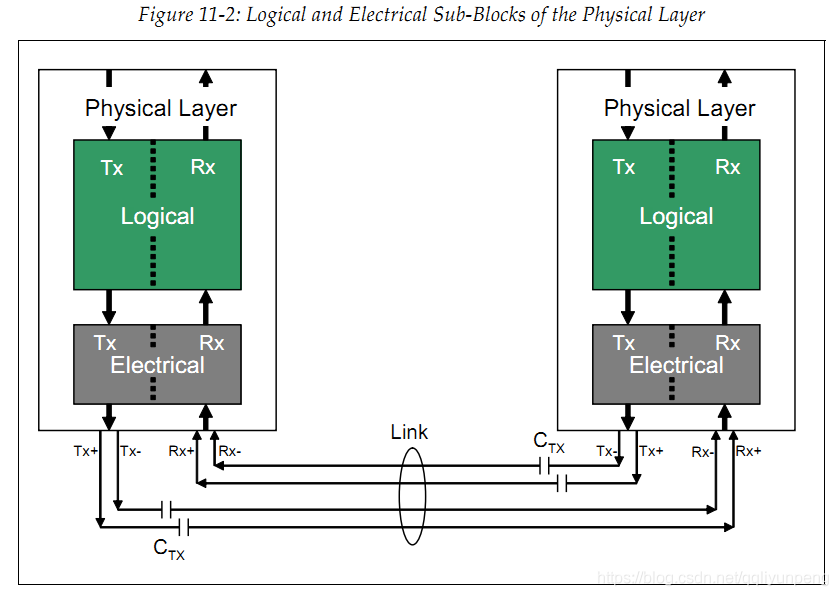

PCIe需要在发射端和接收端之间交流耦合,差分对的两个交流耦合电容必须有相同的封装尺寸,位置要对称且要摆放在靠近金手指这边,电容值推荐为0.1uF。

SCL等信号线不能穿越PCIe主芯片。

3. PCIe 分类、速度

按lane( 车道 --》 通道 )的个数分有 x1 x2 x4 x8 x16 (最大可支持32个通道)

按代来分 有 gen1 gen2 gen3 gen4 gen5

速度:

PCIe 与 PCI 之间的区别

速度上

PCI的工作频率分为33MHz和66MHz,最大吞吐率 266MB/s

PCIe如3中描述,PCIe 1.0 x1 的吞吐率就达到了250MB/s

传输方式上

PCI 是并行数据传输,一次传输4字节/8字节,半双工

PCIe是串行数据传输,全双工

硬件上

传输PCI信号的是普通电平

传输PCIe信号的是差分电平

链路上

PCI是总线的连接方式

PCIe是点对点的连接方式

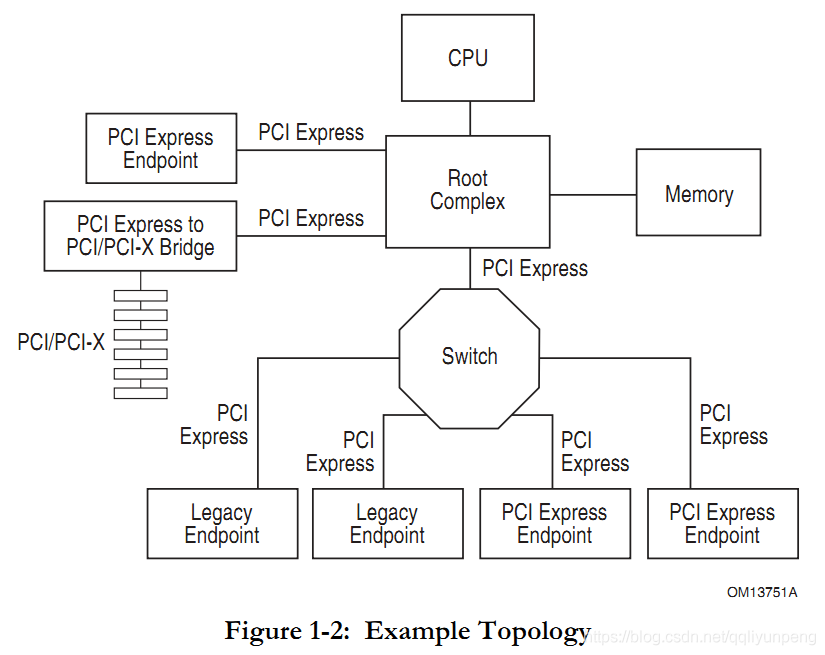

点对点拓扑是什么样的?

PCIe的物理连接方式:

5. 编码方式介绍

PCIe gen1 和 PCIe gen2 采用的编解码方式是 8b/10b,PCIe gen3 和 之后的 采用的是 128b/130b 的编码方式。

8b/10b 意思是说,当我们要传输8b的数据时,实际在通道上传输的是10b的数据,解码的时候,我们希望得到的是8b的有效数据。这样,相当于有效的带宽是实际带宽的 80%。

同理128b/130b,是传输128bit数据实际线路中传输的是130bit数据。

速率图中的单位间的关系:

传输速率单位 GT/s,表示 千兆传输/秒,是实际每秒传输的位数,他不包括额外吞吐量的开销位。

两个例子:

PCIe gen1 x1 传输速率 2.5GT/s = 2500MT/s = ( 2500 / 10 ) MB/s

PCIe gen3 x1 传输速率 8GT/s = 8000MT/s = ( 8000 / 130 ) x ( 128/8 ) MB/s= 984.6153.。. MB/s

6. inbound 和 outbound

在PCIe设备和系统内存互相访问时,outbound是指CPU到设备方向;inbound指Device--》 RC(CPU端)方向。从这个概念上说,设备(device)都是外部的,没有内部设备之说。CPU读写RC 端的寄存器时,还是属于片上系统的范围,所以既不是inbound 也不是outbound。

7. PCI 配置空间

PCI设备拥有256B的配置空间,PCIe还提供另外4KB的扩展,这256B的配置空间中前64B是规范了的,其他的字节是各个厂商自己定义的。

7.1 PCI 设备的地址组成

① 总线号 --- 厂家ID

② 设备号 --- 设备ID

③ 功能号 --- 设备类

查看PCI设备的工具是 lspci

使用工具 lspci 查找 ①②③

》lspci

上边输出的每行开头逻辑地址(XX:YY.Z)分别表示①②③,

其中一个PCI域能容纳 256 个总线,

每个总线可以支持 32 个PCI设备,

每个PCI设备可容纳 8 个PCI功能

》 lspci -t (以树状结构显示)

》 lspci -x (打印出配置空间前64字节的内容)

》 lspci -s (指定哪个)

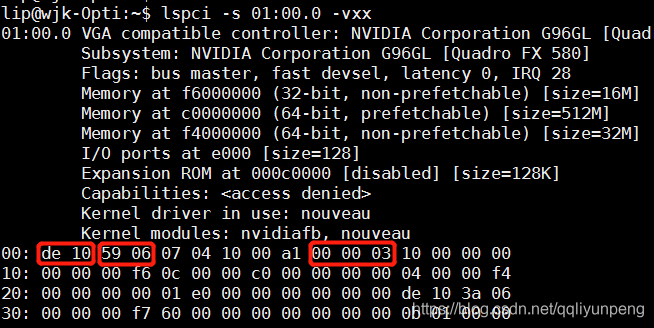

挑选一个 VGA compatible controller,如下

》 lspci -s 01:00.0 -vxx

字节序是小端格式,

[ 0 - 1 ] 表示的是厂家 ID,上图的是 0x10de

[ 2 - 3 ] 表示的是设备 ID,上图的是 0x0659

[ 9 - 11 ] 表示的是设备类型代码,上图的是 0x030000

[14]表示的是设备类型,00表示普通端点设备;01表示Bridge设备;02表示CardBus bridges

使用命令查询PCI设备的厂商号和设备号

》 lspci -n -s 01:00.0

列出格式 【设备类型:厂商ID:设备ID】

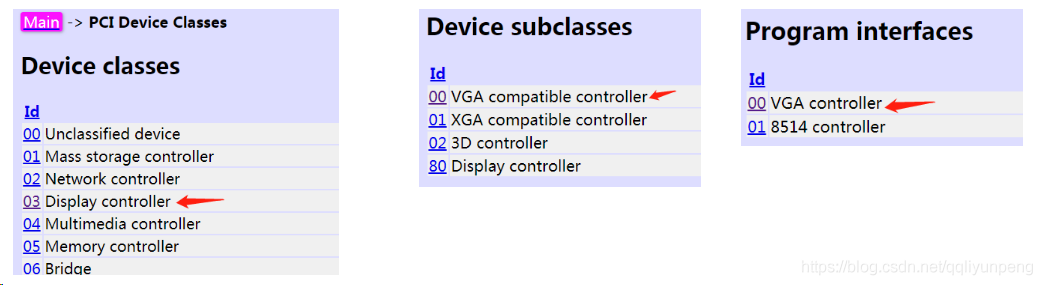

设备类型介绍:

设备类型可以在 http://pci-ids.ucw.cz/read/PD 网站进行查询,包括 classes、subclasses、Program interfaces 三部分,上图中的设备类型是 030000依次对应下图,03是 Device classes,00是Device subclasses,00是Program interfaces

7.2 基地址/BAR

BAR0: 0XF6000000

BAR1: 0XC000000C

。..。

BAR5:0X0000E001

有6个BAR空间,每个BAR记录了该设备映射的一段地址空间,为了区分 IO空间和 IO内存,分开描述如下:

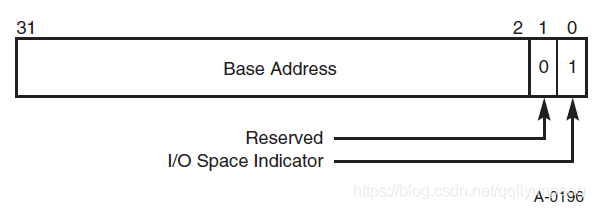

当BAR的最后一位为0,如下图,表示这是映射的IO内存,1-2位表示内存的类型,00=任意32位地址,01=少于1M,10=任意64位地址,11保留。bit1为1表示区间大小超过1M,为0表示不超过1M。bit3表示是否支持可预取。

如上例子中,BAR0是 映射的IO内存,32位地址,不超过1M,不支持预取。

BAR1(最后几位0110)也是映射的IO内存,64位地址,区间大小超过1M,不支持预取。

当BAR的最后一位为1,如下图,表示这是映射的IO地址空间。上边例子中的BAR5(最后一位是1)是映射的是IO地址空间,基地址是 0x0000e

中断

由配置空间的IRQ Pin决定是否支持中断,1表示支持,0表示不支持,加入支持,IRQ Line是中断号。

上边的例子中支持中断号,中断号是0x0b

访问PCI

PCI设备包含3个寻址空间:配置空间、I/O端口 和 设备内存。

驱动中操作 PCI 的配置区(上边讨论的64B的空间)

pci_read_config_[byte|word|dword](struct pci_dev *pdev, int offset, int *value);

pci_write_config_[byte|word|dword](struct pci_dev *pdev, int offset, int value);

offset, 想访问的配置空间中字节位置

value, 对read函数来说,用于存放读回来的数据

对write函数来说,是要写进去的值(这个int.。..。)

驱动中操作 I/O和内存

I/O区域包含寄存器,内存区域存放数据。

驱动中操作 PCI 的I/O和内存

unsigned long pci_resource = pci_resource_[start|len|end|flags] (struct pci_dev *pdev, int bar);

start, 区域的基地址

bar, 取值 0 - 5

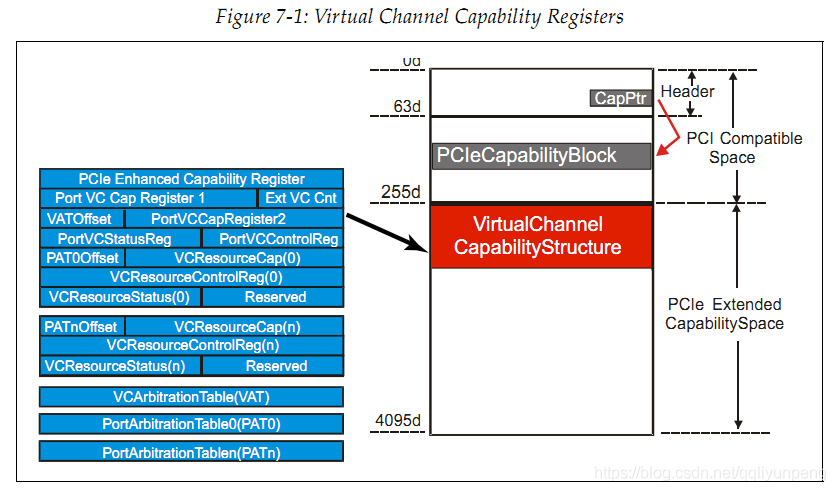

8. PCIe 的配置空间

PCI的配置空间是256字节,即 0x00~0xFF,而PCIe的配置空间是4k字节,即 0x00~0xFFF。

PCIe 一共支持 256条bus,32个dev,8个fun。同PCI是一样的。共需要内存大小= 4k * 256 *32*8 = 256K Bytes = 256M,这个256M的内存空间是为PCIe设备准备的空间系统不可用。

PCIe设备发展向前兼容PCI,每个设备的配置空间的前256个Byte是PCI空间,后(4k-256)个Byte的空间是PCIe扩展空间

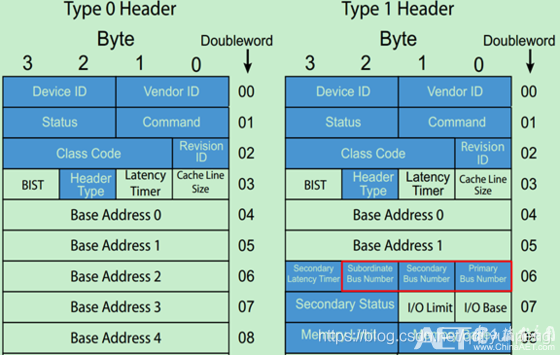

Root和Switch的每一个端口中都包含一个P2P桥,桥的配置空间是Type1型

每个Type1型的Header中都包含最后一级总线号(Subordinate Bus Number)、下一级总线号(Secondary Bus Number)和上一级总线号(Primary Bus Number)等信息。当配置请求进行BDF路由的时候,正是依靠这些信息来确定要找的设备的。

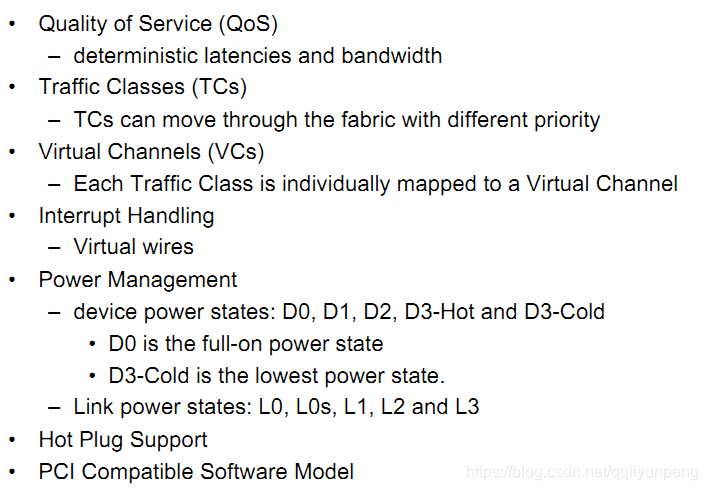

9. PCIe 属性

服务质量(Qos)

决断振幅和带宽

10. FAQ

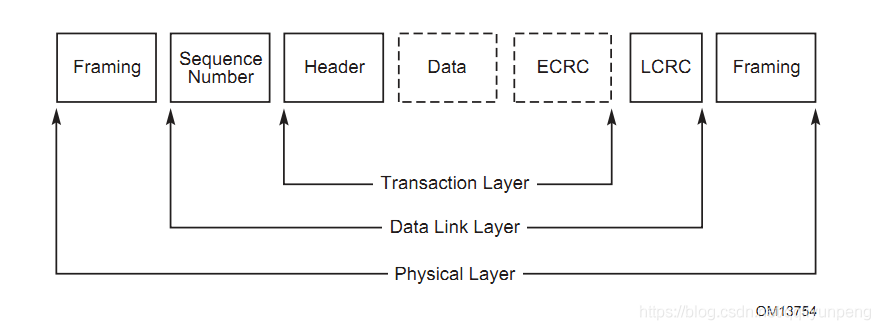

TLP 和 DLLP 是什么?

TCP 是 事务层包的简写,结构下图

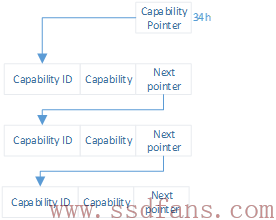

Capability是什么?

Capability是device通过在4k Byte的Configuration Space里告诉host它支持哪些特性的,而Capability又大致分为基本的Capability与之后扩展的Capability,在使用4K的配置空间时两者大同小异,都是采用链表形式来自定义Capability的位置的,唯一的区别是后者种类多,且不同厂商所支持的Capability有很大区别。如下图为Configuration Space的基本架构——0-3Fh(PCI Head域),40h-FFh(基本Capability区域),100-FFF(扩展Capability区域)。

基本的Capability

Capability point是在0-3Fh(PCI Head域),偏移为34h,用于存放第一个Capability的偏移量,偏移量的范围是40h-FFh(基本Capability区域),这段区间可任意让你分配各种基本Capability。

扩展的Capability

第一个扩展Capability默认就从100h的偏移位置开始放置,而不是像基本的Capability那样从34h通过指针指过来。

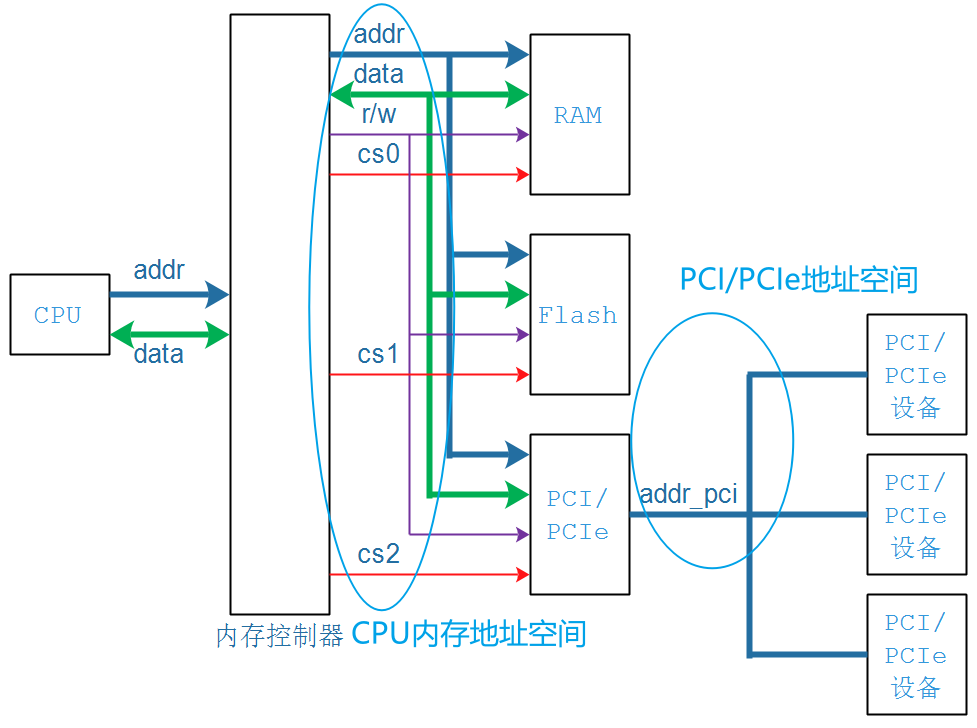

PCI总线空间与处理器空间隔离

PCI设备具有独立的地址空间,即PCI总线地址空间,该空间与存储器地址空间通过HOST主桥隔离。处理器需要通过HOST主桥才能访问PCI设备,而PCI设备需要通过HOST主桥才能访问主存储器。

处理器访问PCI设备时,必须通过HOST主桥进行地址转换,反过来也是。HOST主桥的一个重要作用就是将处理器访问的存储器地址转换成PCI总线地址。

原文标题:FPGA学习-PCIe基础知识

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

芯片

+关注

关注

459文章

51893浏览量

433293 -

数据传输

+关注

关注

9文章

1988浏览量

65381 -

PCI

+关注

关注

5文章

675浏览量

131177 -

PCIe

+关注

关注

16文章

1299浏览量

84343

原文标题:FPGA学习-PCIe基础知识

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

不到两年,PCI-SIG宣布完成PCIe 5.0标准制定工作

PCIE板设计规则--PCI Express Board Design Guidelines

国外PCIE的书籍《pci express system architecture》

从PCI、PCI-X到PCI-Express之间的连接

pcie和pci插槽有什么区别

PCIe与PCI之间的区别

PCIe与PCI之间的区别

评论