对于单板而言,热量传递有导热,对流换热以及辐射换热三种方式,在终端设备散热过程中,这三种方式都有发生。对于芯片而言,主要有以下三个途径:

1.die热量通过封装材料传导到器件表面后对流散热,低导热的封装材料影响传热,当然我们有时候也会根据设计需要增加散热器;

2.die热量通过pad,封装材料和器件底面与PWB之间的空气层后,传递到PWB散热;

3.die热量通过lead Frame和die之间是极细的键合线,因此die和Lead frame之间存在很大的导热热阻,这会限制管脚散热。

随着芯片越做越小,对散热的要求也越来越高,方式1和方式2变得越来越通用,而通过方式1往往需要散热器的配合使用。

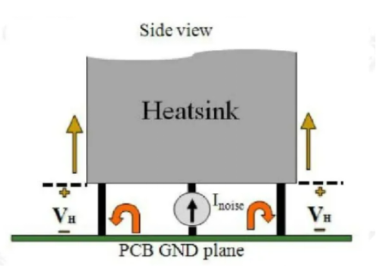

我们在前面的文章中也提到过,共模干扰分为电流驱动型,电压驱动型和电磁耦合型。而散热器不接地属于共模干扰的电压驱动型。通常在使用散热器时,需要将散热器接地,这样可以大大减少EMI问题,因为大地为共模干扰提供了低阻抗路径,当然了,地的阻抗要低。不然会引起地弹现象,引发新的干扰问题。

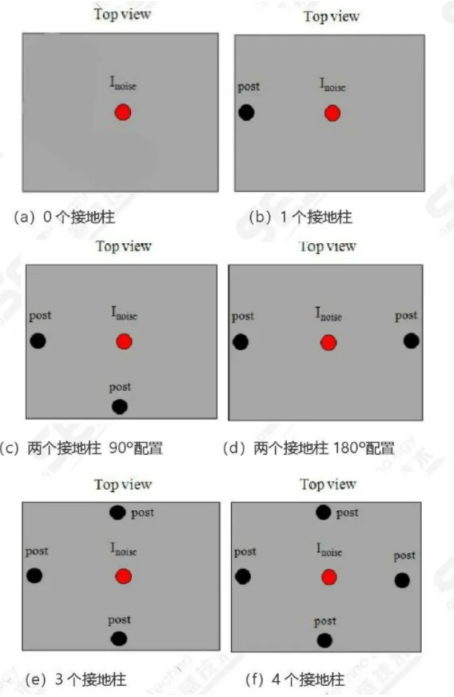

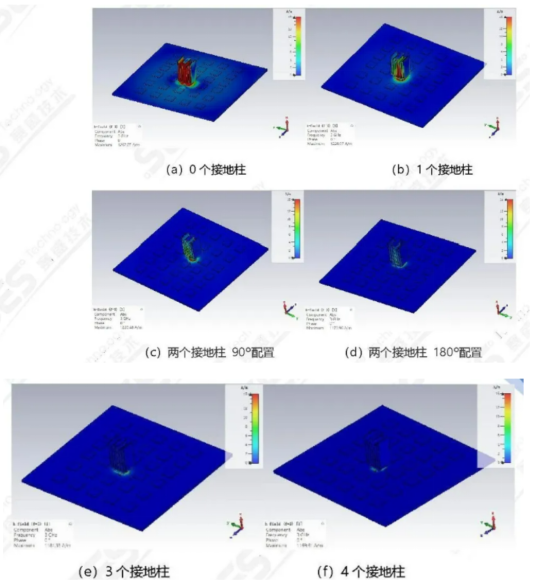

根据散热器的长宽高比例不同,当散热器的高度达到电磁辐射波长的1/4长度时,会形成单极子天线。随着器件开关频率的提高,引起的辐射EMI问题会越来越严重,图示为散热器与PCB地平面耦合电流分布图,图中Inoise为耦合电流,黑色柱子为接地点,接地点需要靠近耦合电流(减小环路面积),同时增加接地点(降低接地阻抗),使得更多噪声选择低阻抗的地平面作为回流路径,从而减少辐射到空间的电磁波,减小辐射的目的。

散热器的接地点和接地点数目都很好理解,但是接地点如何分布又是怎么样的,可以通过以下仿真获得,以下图为几种不同的节点方式:

通过仿真软件,可以看出:

1.在数量相同的情况下,180°接地柱比90°效果要好;

2.散热器接地点数目越多,对辐射抑制效果越好。

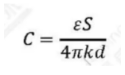

在实际产品散热设计中,我们为了增加导热性能,往往需要使用导热胶填充散热器与元器件之间的间隙,增加接触面积,减小热阻,导热胶是一种介电常数大于1的绝缘材料,在芯片与散热器之间使用散热胶后,电容的计算公式:

介电常数增加,电容C增大,根据不考虑损耗情况下的阻抗公式:Z=L/C,开根,可以看出,C越大,阻抗越小,电磁波越容易通过散热器,增加了对外辐射的能量。

总结:

1.接地点成180°设计排列可获得更好的效果;

2.尽可能的增加接地点的数目;

3.热其实也是一种电磁波,良好的散热设计可能会带来EMI问题,这个时候需要考虑给EMI提供比散热器更好的回路路径,这个就好比信号完整性问题跟EMI问题可能在某些方面对立存在的,从EMI角度来看,电感应该是放置在最靠近信号输出端,但是从信号完整性角度考虑,为了减小传播路径的耦合干扰,需要将电感放置在插座端/接收端,不过解决方法永远比问题多,我们还是可以考虑电感放置在插座端,因为相对于板间的干扰,外界的干扰才是最难评估的。

审核编辑 :李倩

-

电流

+关注

关注

40文章

6972浏览量

133025 -

散热器

+关注

关注

2文章

1065浏览量

37905

原文标题:使用散热器会带来这些坑,你知道吗?[20220704]

文章出处:【微信号:EMC_EMI,微信公众号:电磁兼容EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

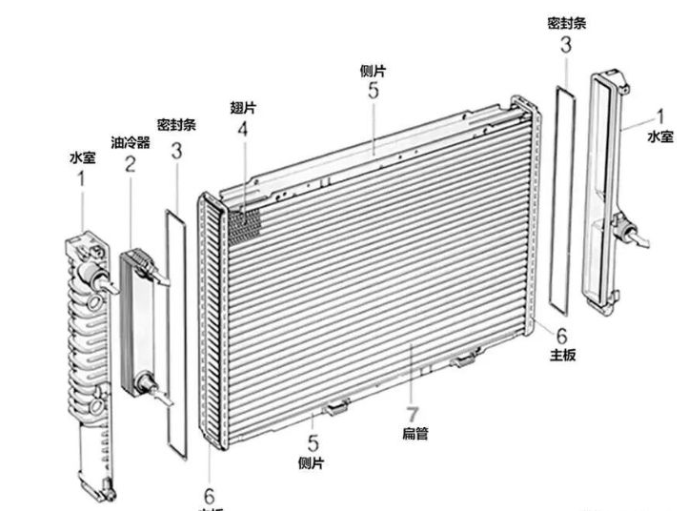

汽车散热器构造对汽车散热效果产生的影响

普诚PT2513B芯片在三相水冷显卡散热器的应用

汽车散热器支架焊接技术分析与应用

NTC温度传感器如何护航新能源汽车散热器

功率器件热设计基础(三)——功率半导体壳温和散热器温度定义和测试方法

TAS5630B器件顶部散热焊盘和散热器之间加导热绝缘垫,散热器需要接地吗?

手机散热器拆解

如何选择合适的风冷散热器?

IGBT散热器的材料选择

IGBT散热器的进水出水口的区分方法

散热器到处都是,到处都是!为什么不在每个发热组件的顶部放置一个散热器呢?

散热器气密性检测仪的操作方法

一文详解散热器

汽车散热器结构与分类 汽车散热器常见故障有哪些?

使用散热器会带哪些坑

使用散热器会带哪些坑

评论