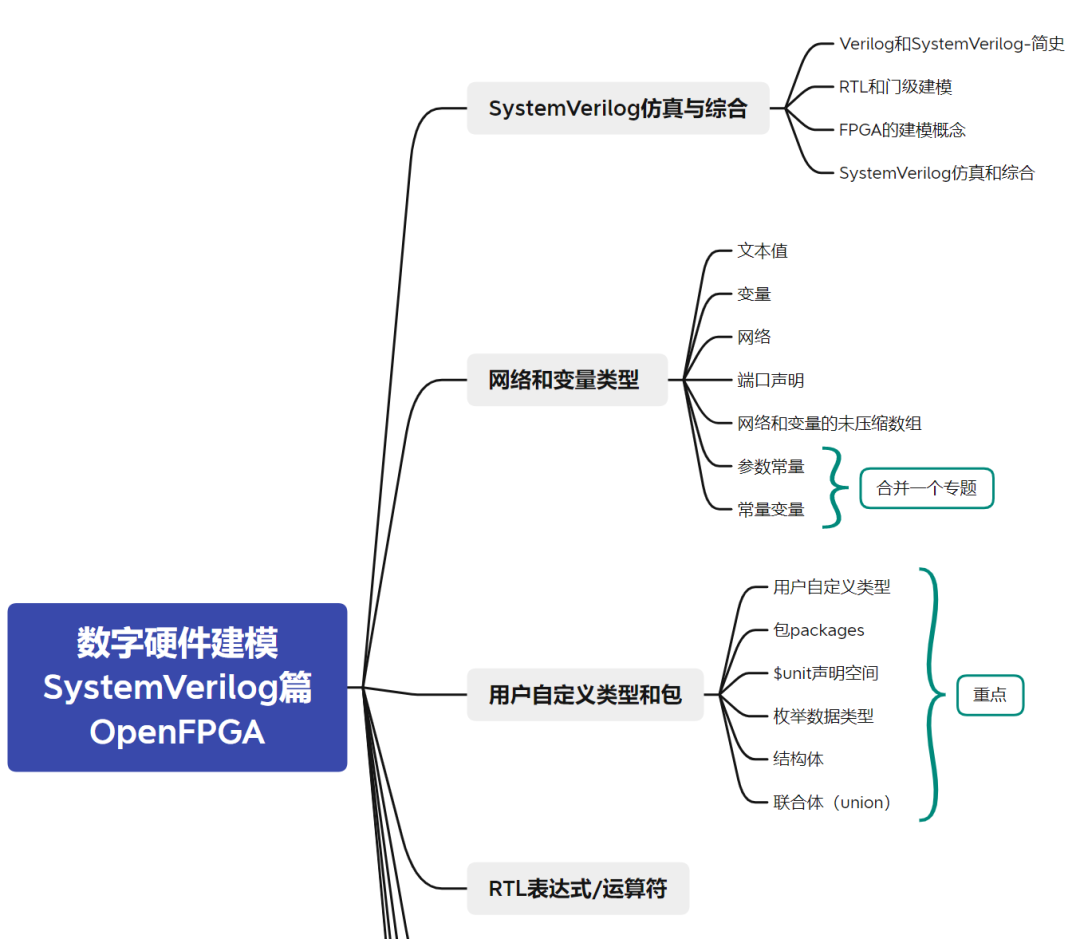

前面已经写了大约10篇左右文章介绍了SV,效果不是特别理想,对于一些常规的概念还是比较好理解的,但是对于一些新的专业术语,翻译的比较拗口还是比较难理解的,这是因为国内还没有针对可综合SystemVerilog系统的介绍,导致标准里的术语翻译不精确,后续可能还是使用英语单词来表示,然后用一些非专业术语去解释,下面简单总结一下这十几篇内容。

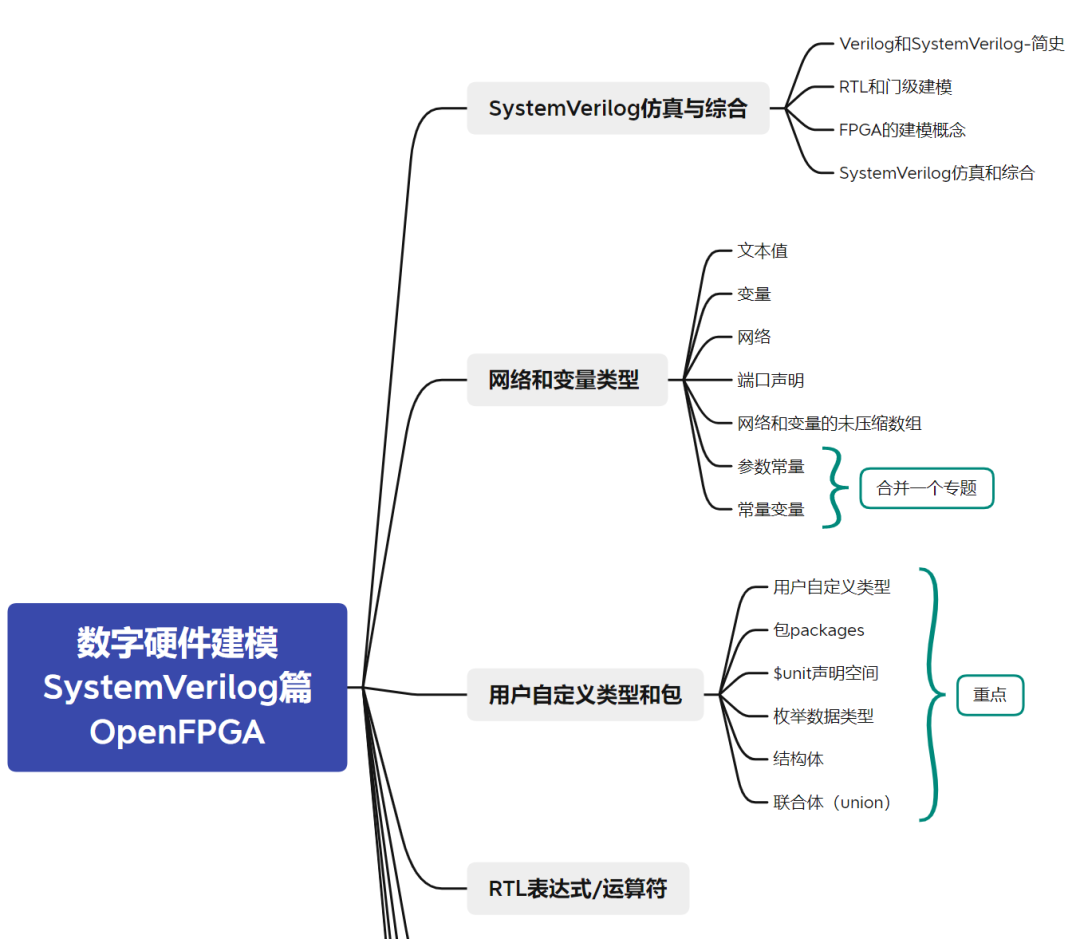

最前面几篇文章重点介绍SystemVerilog仿真与综合概念及一些对比,总结如下:

SystemVerilog是硬件设计和验证语言的IEEE行业标准。标准编号为IEEE 1800。SystemVerilog名称将替换旧版Verilog名称。SystemVerilog语言是原始Verilog硬件描述语言的完整超集。SystemVerilog是一种双用途语言,用于描述数字硬件功能以及验证测试台。

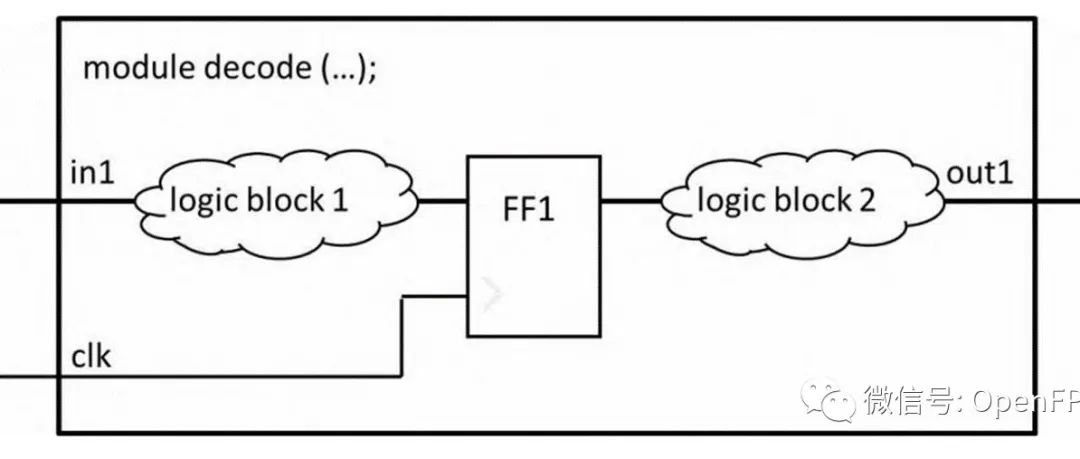

硬件行为可以在几个抽象级别上表示,从非常详细的门级模型到非常抽象的事务级模型。本系列的重点是在寄存器传输级别(RTL)编写SystemVerilog模型。RTL模型表示基于周期的行为,很少或根本没有提及如何在硅中实现功能。

SystemVerilog RTL模型如果编码正确,可以进行仿真和综合,仿真使用用户定义的测试台将激励应用于设计输入,并验证设计功能是否符合预期。仿真对SystemVerilog语言的使用没有任何限制。综合将抽象的RTL功能转换为详细的门级实现。综合编译器限制了可以使用哪些SystemVeriIog语言结构以及如何使用这些结构。Lint checker工具可用于检查RTL模型是否符合综合编译器的限制。

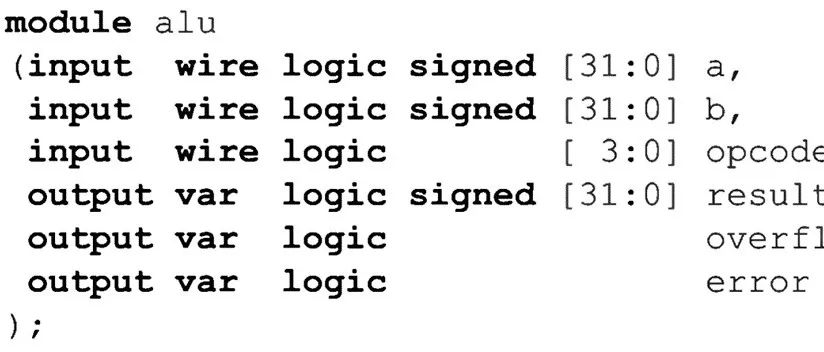

接下来完整的介绍了SV的数据类型:网络和变量类型,总结如下:

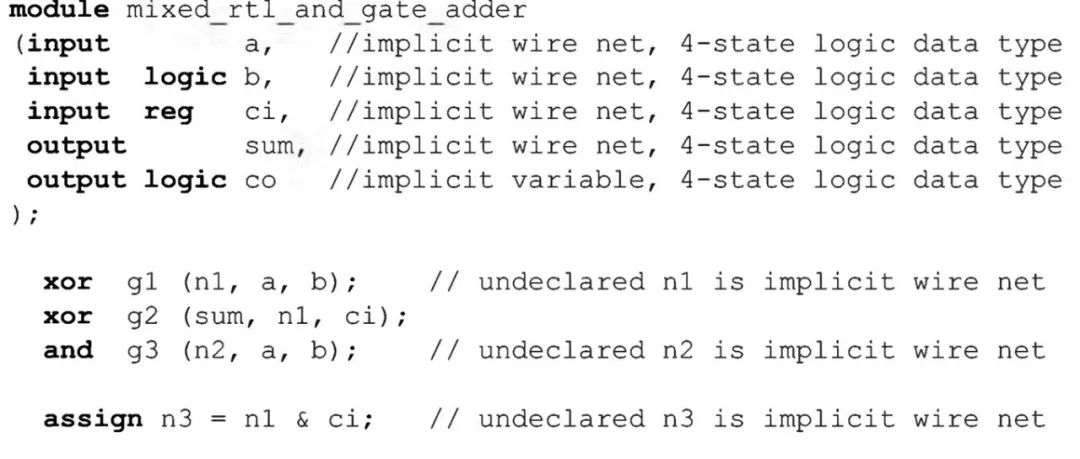

研究了SystemVerilog语言中预定义的内置类型和数据类型。重点是对编写RTL模型有用的类型和数据类型,这些RTL模型将以最佳方式进行仿真和综合。

SystemVerilog具有2-state和4-state数据类型。4-state数据类型的四值系统允许建模硬件行为值0、1和Z表示物理硬件。值X用于仿真不关心条件,其中设计工程师不关心物理硬件是否具有0或1值。仿真器还使用X值表示潜在问题,其中仿真无法确定实际逻辑门是否具有0、1或Z。SystemVerilog的2-state类型不应用于仿真硬件行为,因为它们没有X值来表示仿真期间的潜在设计错误。

SystemVerilog网络类型(如wire类型)用于将设计块连接在一起。网络始终使用4-state数据类型,并且当有多个源驱动同一网络时,可以解析最终值。SystemVerilog变量类型用于接收赋值语句左侧的值,并将存储赋值=直到对变量进行另一次赋值。SystemVerilog有几种网络类型和变量数据类型。已经展示了声明网络和变量的语法,并讨论了重要的语义规则。还讨论了在RTL模型中如何正确使用这些不同的网络和变量。

SystemVeriIog允许通过使用参数和localparam常量编写可配置的模型。可以使用参数重写(也称为参数重新定义)为模块的每个实例指定常数的唯一值。

优秀的 Verilog/FPGA开源项目介绍(二十二)- SystemVerilog常用可综合IP模块库

谈谈Verilog和SystemVerilog简史,FPGA设计是否需要学习SystemVerilog

SystemVerilog数字系统设计_夏宇闻 PDF

SystemVerilog(一)-RTL和门级建模

数字硬件建模-Verilog篇阶段总结及SystemVerilog篇介绍

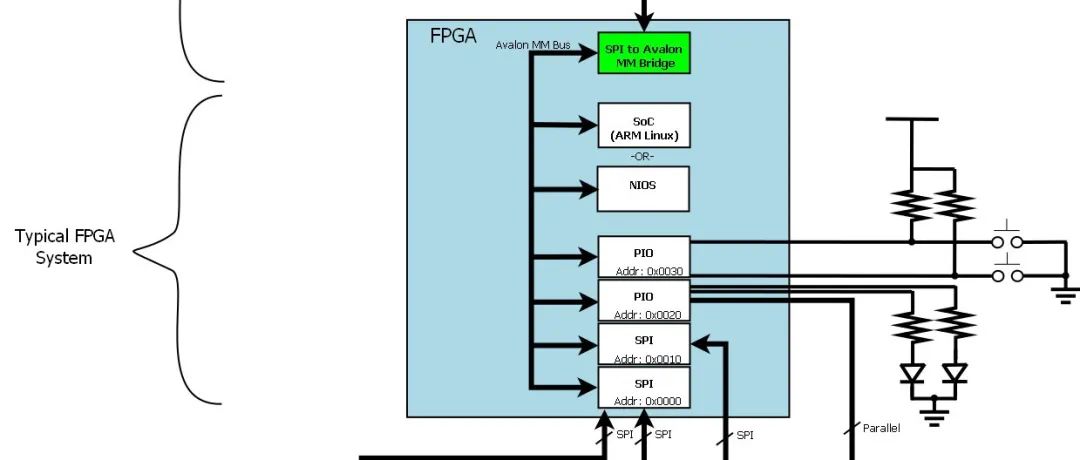

SystemVerilog(二)-ASIC和FPGA区别及建模概念

SystemVerilog(三)-仿真

FPGA的综合和约束的关系

SystemVerilog(五)-文本值

SystemVerilog(六)-变量

SystemVerilog(七)-网络

数字硬件建模SystemVerilog(八)-端口声明

现在介绍完前两级的内容,后续将介绍最重要的一章-《用户自定义类型和包》。有什么问题可以后台留言。

原文标题:SystemVerilog-阶段性总结(一)

文章出处:【微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1664文章

22504浏览量

639301 -

IEEE

+关注

关注

7文章

418浏览量

50394 -

寄存器

+关注

关注

31文章

5620浏览量

130423 -

硬件

+关注

关注

12文章

3635浏览量

69172

原文标题:SystemVerilog-阶段性总结(一)

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

安达发|是什么让日化行业瞬间“开挂”?原来是APS软件!

FPGA时序收敛的痛点与解决之道——从一次高速接口调试谈起

Vivado时序约束中invert参数的作用和应用场景

输入引脚时钟约束_Xilinx FPGA编程技巧-常用时序约束详解

开源RISC-V处理器(蜂鸟E203)学习(二)修改FPGA综合环境(移植到自己的Xilinx FPGA板卡)

时序约束问题的解决办法

关于综合保持时间约束不满足的问题

蜂鸟e203移植fpga上如何修改约束文件

FPGA开发板vivado综合、下载程序问题汇总

技术资讯 I 图文详解约束管理器-差分对规则约束

Vivado无法选中开发板的常见原因及解决方法

PCB Layout 约束管理,助力优化设计

FPGA的综合和约束的关系

FPGA的综合和约束的关系

评论