继最近发布一些突破性新硅光子(SiPh)探针的发展对于CM300xi探针台,我们想向后盘旋并深入了解一些细节。我们之前展示了一些OptoVue Pro™的亮点,可以在不移除当前被测试晶圆的情况下原位执行光学定位器校准,从而缩短了数据采集时间。在这里,我们将探讨高带宽的新边缘耦合效率。

用于水平模级边缘耦合

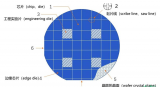

通过使光纤/阵列通过水平裸片级边缘耦合尽可能靠近裸露的波导小平面,可以实现高带宽应用的最佳耦合效率。真正的边缘耦合功能可实现逼真的环境条件仿真,其设备性能最接近最终应用。

我们提供了市场上唯一的解决方案,该解决方案能够实现水平模具级边缘耦合的高级自动对准,部署专有的光纤到面对准自动对准技术并通过避免碰撞技术将损坏光纤的风险降至最低。

像AlignOpticalProbes3D这样的独特软件算法(请参见下文)可优化光纤与光纤之间的间隙以及输入和输出端的最大耦合功率。

没有其他可用的解决方案使您能够在YZ平面中校准定位硬件,并准备执行边缘耦合光学优化。

晶圆级边缘耦合

晶圆级边缘耦合现在可以通过硬件和软件功能的创新组合实现,以对准和优化晶圆级沟槽中的光纤/阵列。

一套软件对准算法可在晶片沟槽中进行YZ优化扫描,而带锥状透镜的光纤支架可相对于晶片表面提供较小的接近角。这使得探针在沟槽中的对准尽可能靠近小平面,从而以最小的沟槽尺寸最小化耦合损耗。

该解决方案意味着即使对于经验不足的用户也可以轻松设置,由于独特的光纤到面间隙对齐技术,可重复获得测量结果,并通过防撞技术降低了损坏光纤的风险。

以下是我们现已提供的先进对准解决方案的四个关键功能:

1. Measure3DCoupling–执行连续的区域扫描,然后沿耦合轴步进移动,以构建功率耦合的3D图像。可用于多种目的,例如检测光纤损坏,检测DUT污染,测量透镜光纤的焦距等。适用于边缘和垂直耦合。

2. AlignOpticalProbesEdge–对多个选定的探针执行基于视觉的间隙比对,然后执行YZ区域扫描,同时根据需要进行重新居中。

3. AlignOpticalProbes3D–搜索输入和输出光纤的最佳间隙,以产生最大耦合功率。

4. AlignOpticalProbeGap–在XY中的单个探针上执行基于视觉的间隙对齐,移至Z中的探针高度,并准备进行YZ区域扫描。

审核编辑:符乾江

-

芯片

+关注

关注

459文章

51726浏览量

430939 -

晶圆

+关注

关注

52文章

5045浏览量

128762

发布评论请先 登录

相关推荐

台积电研发芯片封装新技术:从晶圆级到面板级的革新

采用微型晶圆级芯片封装的TPS63036高效率降压/升压转换器数据表

晶圆和芯片级应用的边缘耦合效率

晶圆和芯片级应用的边缘耦合效率

评论