奇技淫巧我不会,但我这有一些我工作后才学到的一些Verilog写法。

数字电路设计主要就是,选择器、全加器、比较器,几个常用逻辑门,再加个D触发器,电路基本都能实现了。写代码其实是个体力活,电路和时序图应该在设计阶段就已经到了你的文档里或在脑子里没来得及写出来。组合逻辑+时序逻辑

assign或always@(*)always@(posedge clk or negedge rst_n)有人说掌握Verilog 20%的语法就可以描述 90%以上的电路,说的对。

casez

always @(*)begin casez(code) 8'b1???_???? : data[2:0] = 3'd7; 8'b01??_???? : data[2:0] = 3'd6; 8'b001?_???? : data[2:0] = 3'd5; 8'b0001_???? : data[2:0] = 3'd4; 8'b0000_1??? : data[2:0] = 3'd3; 8'b0000_01?? : data[2:0] = 3'd2; 8'b0000_001? : data[2:0] = 3'd1; 8'b0000_0001 : data[2:0] = 3'd0; default : data[2:0] = 3'd0; endcaseend这样的case有优先级选择,可综合,实际项目可以使用,不过我个人习惯上还是,有优先用if-else,没有直接用case。synopsys的EDA工具有关于full case与parallel case可以查看下面博客链接。https://blog.csdn.net/li_hu/article/details/10336511 generate+for

合理使用generate+for循环可以提高编码效率,同样的赋值语句需要赋值多次。generate genvar i; for(i=0;i<16;i=i+1) begin: neg_data assign neg_data_out[i*DATA_WIDTH +:DATA_WIDTH] = -data_in[i*DATA_WIDTH +:DATA_WIDTH] endendgenerate同一个模块需要实例化多次

generate genvar i; =0;i<16;i=i+1) begin: mult_12x12 DW02_mult #( .A_WIDTH(12), .B_WIDTH(12) u_DW02_mult0( +:12]), +:12]), .TC(1'b0), +:24]) ); endendgenerate当然这样写debug会有一些困扰,Verdi会显示每一个generate块,选中对应的块,加进去的波形就会是对应的bit信号。

generate if/case

做一些通用IP的方法,随便举个例子比如要做一个选择器通用IP,支持二选一,三选一,四选一。generate if(MUX_NUM == 0)begin : mux4_1 always@(*)begin case(sel[1:0]) 2'b00:data_out = data_in0; 2'b01:data_out = data_in1; 2'b10:data_out = data_in2; default:data_out = data_in3; endcase endend else if(MUX_NUM = 1) begin : mux3_1 always@(*)begin case(sel[1:0]) 2'b00:data_out = data_in0; 2'b01:data_out = data_in1; default:data_out = data_in2; endcase endend else begin : mux2_1 always@(*)begin case(sel[1:0]) 2'b00:data_out = data_in0; default:data_out = data_in1; endcase endend endgenerategenerate case可以写更多的分支

generate case(MUX_NUM) 0:begin:mux_2 end 1:begin: mux_3 end 2:begin: mux_4 end default:begin end endcaseend endgenerate调用的时候只需要

mux #( .MUX_NUM(0))u_mux( ...);参数化定义

模块化设计,功能模块的划分尽可能细,差别不大的代码通过参数化达到重复使用的目的。always @(*)begin case(sel) CASE0:data_out = data_in0; CASE1:data_out = data_in1; CASE2。。。 default:; endcase end实例化

mux #( .CASE0(8'd11), .CASE1(8'd44) ...)u_mux( ...);移位操作

对于移位操作直接用位拼接assign data_shift[6:0] = data[4:0] << 2;assign data_shift[7:0] = data[4:0] << shift[1:0];写成

assign data_shift[6:0] = {data[4:0], 2'b0};always @(*)begin case(shift[1:0]) 2'b00: data_shift[7:0] = {3'b0, data[4:0]}; 2'b01: data_shift[7:0] = {2'b0, data[4:0], 1'b0}; 2'b10: data_shift[7:0] = {1'b0, data[4:0], 2'b0}; default:data_shift[7:0] = {data[4:0], 3'b0}; endcaseend如果是有符号数,高位要补符号位。也就是算术移位。

always @(*)begin case(shift[1:0]) 2'b00: data_shift[7:0] = {{3{data[4]}}, data[4:0]}; 2'b01: data_shift[7:0] = {{2{data[4]}}, data[4:0], 1'b0}; 2'b10: data_shift[7:0] = {data[4], data[4:0], 2'b0}; default:data_shift[7:0] = {data[4:0], 3'b0}; endcaseendshift也可能是有符号数,正数左移,负数右移。右移方法同理。

$clog2系统函数

Verilog-2005引入了$clog2系统函数,为了方便计算数据位宽,避免位浪费。(这个是拿来凑字数的)parameter DATA_WIDTH = 4,parameter CNT_WIDTH = log2(DATA_WIDTH)parameter CNT_WIDTH = clog2(DATA_WIDTH-1)parameter CNT_WIDTH = $clog2(DATA_WIDTH) reg [DATA_WIDTH-1:0] data_r0; reg [CNT_WIDTH-1:0] cnt; //-------------------------------------------------------//以下两个函数任用一个//求2的对数函数function integer log2; input integer value; begin value = value-1; for (log2=0; value>0; log2=log2+1) value = value>>1; endendfunction //求2的对数函数function integer clogb2 (input integer bit_depth);begin for(clogb2=0; bit_depth>0; clogb2=clogb2+1) bit_depth = bit_depth>>1;endendfunction对齐

tab键还是空格键?留言区说出你的故事。我把编辑器设置成tab自动替换成4个空格。 用空格对齐代码,提高代码观赏性。assign signal_b = signal_a;assign data_b = data_a;assign cs_en = 1'b1; assign signal_b = signal_a;assign data_b = data_a;assign cs_en = 1'b1;第二种写法更美观,always块里面的语句也应该对齐。

命名

给模块起名字,给信号起名字,真的很难,但是不管怎样都不要用拼音,会遭人鄙视。是的,我见过!

阶梯式assign

assign data_out[5:0] = data_vld0 ? data0[5:0] : data_vld1 ? data1[5:0] : data_vld2 ? data2[5:0] : data_vld3 ? data3[5:0] : 6'b0;由于if-else和case不能传播不定态,有的EDA工具有X态传播选项,可以强行传播,但是并不是所有的EDA工具都有这个功能,所以有些书上建议都用组合逻辑用assign。 这种写法没什么问题,但是有一点,覆盖率不好收,如果一些情况没跑到需要一个个分析。覆盖率会把数据信号当作一个情况列出来,比如数据信号data没出现过0 的情况,实际上数据信号没出现0的情况是正常的,这就要你一个一个的exclude掉。 所以不要写很长的assign做选择器,有优先级用if-else,或根据具体情况用case。这样哪一行哪一种情况没跑到会一目了然。当然if中的条件太多,覆盖率也不好收,条件太多组合的情况多,分析起来繁琐。如果上述信号的vld不同时出现也可以采用这种写法,减少cell的使用数量。这样也是有覆盖率的问题,这只是一种特殊情况,很长的assign选择器尽量不要写。

assign data_out[5:0] = ({6{data_vld0}} & data0[5:0]) | ({6{data_vld1}} & data1[5:0]) | ({6{data_vld2}} & data2[5:0]) | ({6{data_vld0}} & data3[5:0]);关于X态传播,一定要注意,带有reset的寄存器面积和时序会稍微差一些,控制通路的寄存器必须带有复位,数据通路的寄存器可以不带复位,但是要注意使用时如果使用数据通路的数据去做了控制条件,就必须要复位,否则如果X态没有查出来,事情就大了。

布线太密的原因

寄存器位宽太大。reg [10000-1:0] data;

这样写在功能上没什么问题,但是如果你之后有对这个数据做了很多逻辑,可能会造成后端布线太密,从后端的角度看到其实cell数量并不多,就是线比较密,比如说这个数据后面再放个选择器,或者输出给其他模块,就相当于一万根线连到很多地方,布线很紧张,如果时序有问题需要绕线,或者需要ECO,做成的可能性很小。

尽量不要这样做逻辑,除非对面积没限制,要么最后只能改架构。

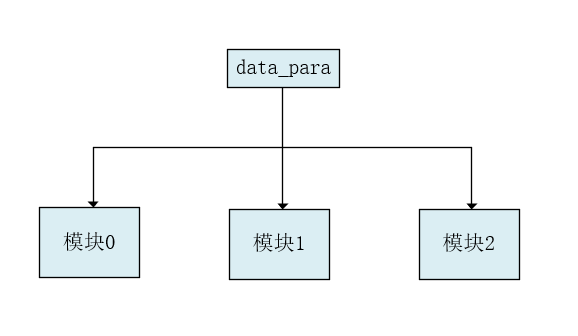

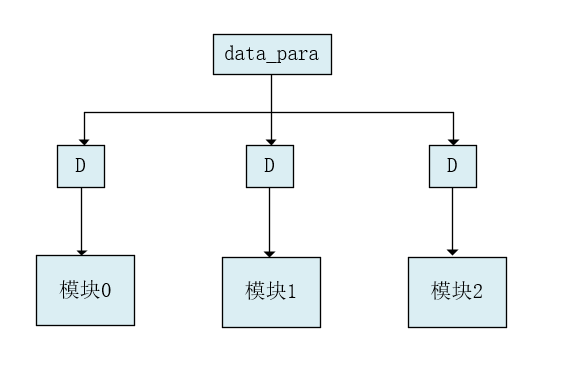

第二个原因是负载太大。同一个信号在很多地方使用,布线也会变复杂,比如最常见的是参数信号,在很多模块都会有用到的情况,用寄存器复制的方法。always @(posedge clk or negedge rst_n)begin if(!rst_n)begin data_para0 <= 4'b0; data_para1 <= 4'b0; data_para2 <= 4'b0; end else begin data_para0 <= data_para; data_para1 <= data_para; data_para2 <= data_para; endend画俩图大概意思一下。这样每个寄存器的驱动变少。

有网友提到这样子写被综合掉的概率也是很大。所以就只能在设计时尽量注意负载的问题。

加比选

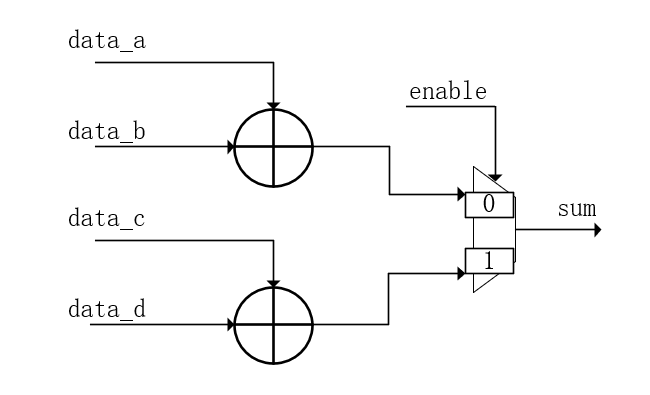

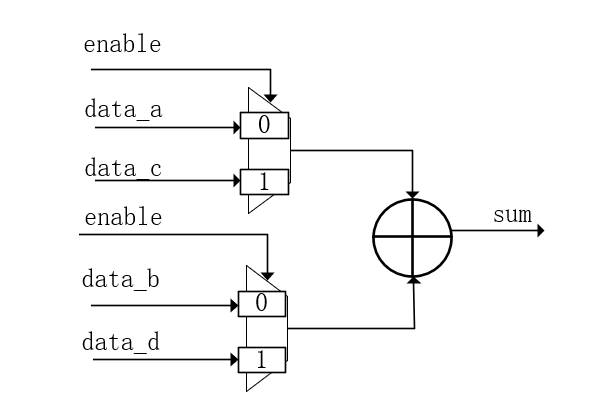

面积:加法器 > 比较器 > 选择器乘法器本质上也是全加器。所以就有先选后比,先选后加,先选后乘。assign sum[4:0] = enable ? (data_a + data_b) : (data_c + data_d); assign add_a[3:0] = enable ? data_a : data_c;assign add_b[3:0] = enable ? data_b : data_d;assign sum[4:0] = add_a + add_b;画个图意思一下。

数据通路与控制通路

数据通路打拍可以不带复位,带着使能信号去打拍,减少信号翻转,减少功耗。保证数据用的时候不是X态, 组合逻辑路径是否需要插入pipeline,插入pipeline的位置需要注意。寄存器能少用就少用。 尽量不要用除法,首先除法器面积更大,除法也会有余数,余数是否需要保留就很麻烦。除以常数可以做成乘以定点常数的方法。 乘以常数用移位加,也可直接用*号。例如a * 2‘d3,工具会帮你优化成 a << 2’d1 + a。甚至可能优化得更好。(杠:不要过度依赖工具)。关于用移位加还是*号的问题,博主做过综合后的面积对比,相对来说,工具还是优化那么一点点。直接用 * 号吧。 尽量不要用减法,减法要考虑到减翻的问题,尽量用加法。方案设计

方案最重要,一个好的方案往往事半功倍。 状态机设计要状态明确,一个状态尽量只做一件事情。状态机大法好。 做成IP化设计,功能分割尽量独立并可复用性,相同的功能用同一块IP,保证IP的没问题,最后像搭积木一样,搭建起数字系统。多积累些常用IP,常用的一些写法的代码。审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

寄存器

+关注

关注

31文章

5382浏览量

121419 -

比较器

+关注

关注

14文章

1660浏览量

107522 -

Verilog

+关注

关注

28文章

1355浏览量

110544

原文标题:Verilog有什么奇技淫巧?

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA算法工程师、逻辑工程师、原型验证工程师有什么区别?

。

总的来说,虽然全部使用时序逻辑也可以实现状态机,但综合考虑资源利用、性能、灵活性和代码可读性等因素,通常会采用组合逻辑和三段式写法来实现

发表于 09-23 18:26

时序逻辑电路的基本概念、组成、分类及设计方法

Logic Circuit)是一种在数字电路中,其输出不仅取决于当前输入,还取决于过去输入历史的电路。与组合逻辑电路(Combinational Logic Circuit)不同,组合逻辑

时序逻辑电路的功能表示方法有哪些

复杂逻辑功能的关键组成部分。它们能够存储信息,并根据输入信号和当前状态产生输出。时序逻辑电路的设计和分析对于理解和实现数字系统至关重要。 2. 时序

组合逻辑电路设计时应遵循什么原则

一定的原则,以确保电路的性能、可靠性和可维护性。 二、设计原则 功能明确 在设计组合逻辑电路之前,需要明确电路的功能和性能要求。这包括输入信号的数量、类型、范围,输出信号的数量、类型、范围,以及电路的时序要求等

组合逻辑电路的结构特点是什么?

时序逻辑电路形成对比,后者具有记忆功能,输出不仅取决于当前输入,还与过去的状态有关。 并行处理能力 :组合逻辑电路可以同时处理多个输入信号,实现并行运算。这种并行处理能力使得

组合逻辑电路逻辑功能的测试方法

一、引言 组合逻辑电路是数字电路中的重要组成部分,它仅由逻辑门电路(如与门、或门、非门等)和输入/输出端组成,不包含任何存储元件。组合逻辑电

组合逻辑控制器是什么设备

组合逻辑控制器(Combinatorial Logic Controller,简称CLC)是一种用于控制和管理复杂系统或设备的电子设备。它通常由多个逻辑门、触发器和其他逻辑元件组成,能

组合逻辑控制器是用什么实现的

组合逻辑控制器是一种用于控制和管理复杂系统中各个组件之间交互的逻辑设备。它可以应用于各种领域,如计算机科学、通信、自动化控制等。在这篇文章中,我们将详细探讨组合

时序逻辑电路的分类及各种电路特点是什么?

时序逻辑电路是数字电路中的一种,它不仅具有组合逻辑电路的即时输出特性,还拥有记忆功能,能够根据输入信号和当前状态产生输出。

Verilog写法:组合逻辑+时序逻辑

Verilog写法:组合逻辑+时序逻辑

评论